一个简单的UVM项目的学习记录(三) |

您所在的位置:网站首页 › 计算器上键的介绍及使用 › 一个简单的UVM项目的学习记录(三) |

一个简单的UVM项目的学习记录(三)

|

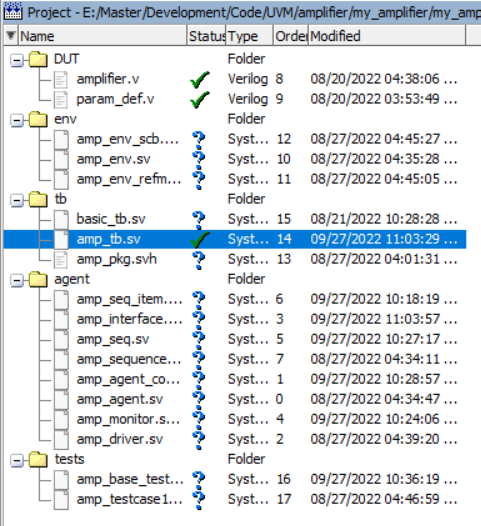

在之前的仿真中,都是用鼠标在图形化界面上操作的。然而为了验证过程更加灵活的操作,肯定不能依赖鼠标,因此这里先使用命令行对之前的验证模式进行优化。 一、文件的编译和运行 1.1 编译在Questa Sim中,不同的文件有不同的编译命令: 编译命令 vlog vcom sscom 编译对象 verilog文件 VHDL文件 System C文件在之前,由于已经成功编译并运行了amp_tb.sv,所以此处会显示绿色的勾。

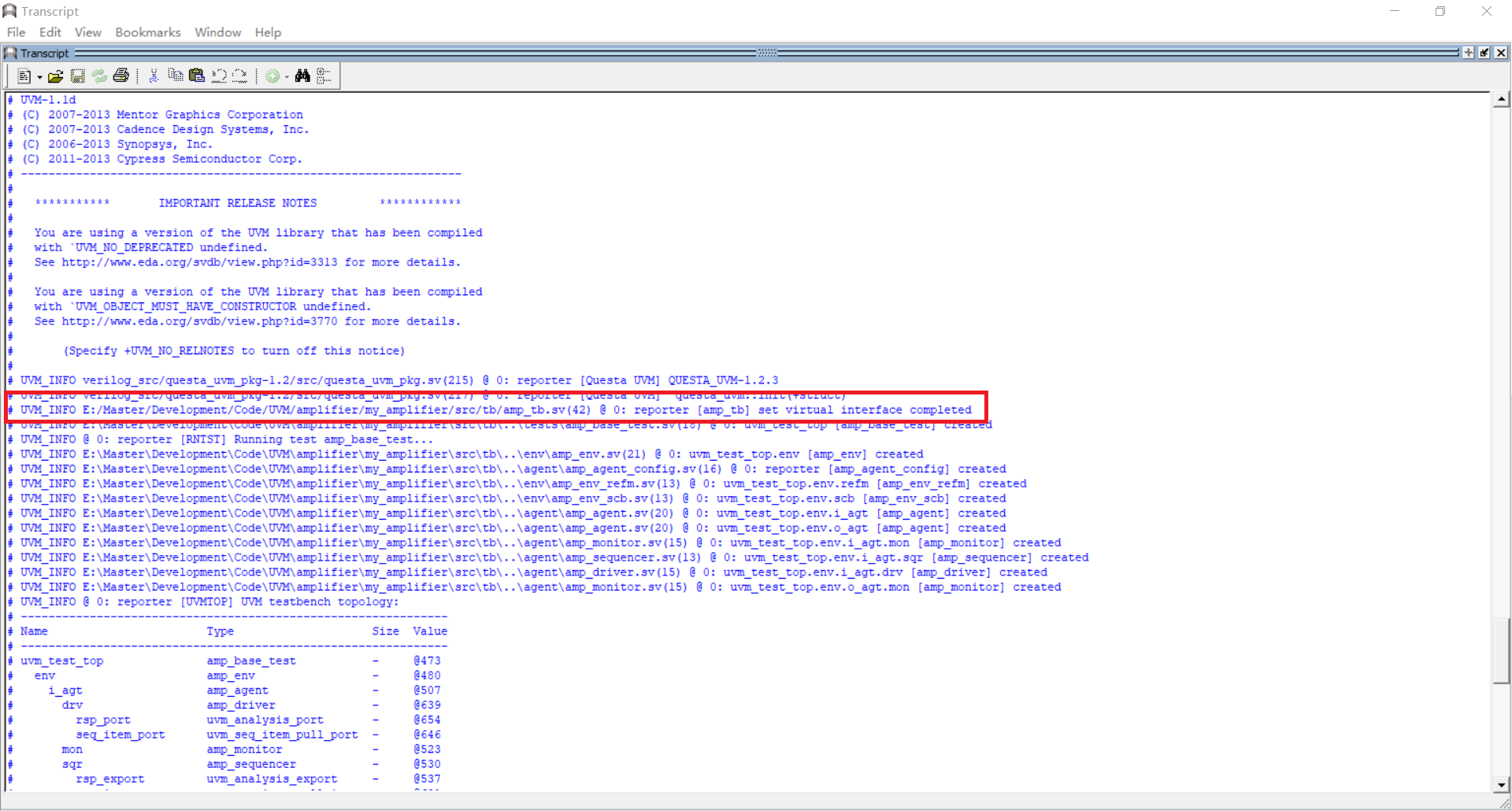

在命令行中,虽然这里的amp_tb.sv是sv文件,但仍然使用vlog命令进行编译。打开该sv文件,在里面添加一行输出后,在Questa Sim的图形化界面可以看到其状态从之前的绿色的勾变成了蓝色的问号,说明文件发生了改变。其中,添加的代码及位置如下: 点击查看代码 initial begin uvm_config_db #(virtual amp_interface)::set(null, "uvm_test_top.env.i_agt", "vif", itf); uvm_config_db #(virtual amp_interface)::set(null, "uvm_test_top.env.o_agt", "vif", itf); `uvm_info("amp_tb", "set virtual interface completed", UVM_LOW) end在命令行输入:vlog -sv amp_tb.sv,其中-sv表示编译的是Syetem Verilog文件。发现提示了编译错误: QuestaSim> vlog -sv amp_tb.sv # QuestaSim-64 vlog 10.6c Compiler 2017.07 Jul 26 2017 # Start time: 17:11:48 on Aug 27,2022 # vlog -reportprogress 300 -sv amp_tb.sv # ** Error: (vlog-7) Failed to open design unit file "amp_tb.sv" in read mode. # No such file or directory. (errno = ENOENT) # End time: 17:11:48 on Aug 27,2022, Elapsed time: 0:00:00 # Errors: 1, Warnings: 0 # D:/DevelopmentTool/QuestaSim-64/win64/vlog failed. 从报告里面很容易就能知道错误原因:找不到该文件。解决方法也很简单,将文件补充成绝对路径即可:vlog -sv {E:/Master/Development/Code/UVM/amplifier/my_amplifier/src/tb/amp_tb.sv},提示编译完成。 当然,注意把其中的路径换成自己电脑下的绝对路径。 在图形化界面上,使用命令行这种方式即使编译成功后,amp_tb.sv处的状态图标也没有变成绿色的勾。是否真的编译成功,在运行完仿真后就能够知道了。 1.2 启动启动仿真的命令其实在图形化界面中见过不少次了。在work库中选择amp_tb文件,右键选择Simulate without Optimization,可以看到下方的命令行窗口输出的指令为:vsim -novopt work.amp_tb。退出仿真,在命令行照猫画虎,输入这条命令就进入了仿真窗口了。 1.3 运行仿真成功进入仿真窗口后,在命令行输入run 100ns,可以仿真amp_tb总计100ns。当然,由于没有使用到挂起机制,仿真会立即结束。 在打印信息中,可以找到这样一条: # UVM_INFO E:/Master/Development/Code/UVM/amplifier/my_amplifier/src/tb/amp_tb.sv(42) @ 0: reporter [amp_tb] set virtual interface completed 说明的确编译成功了。

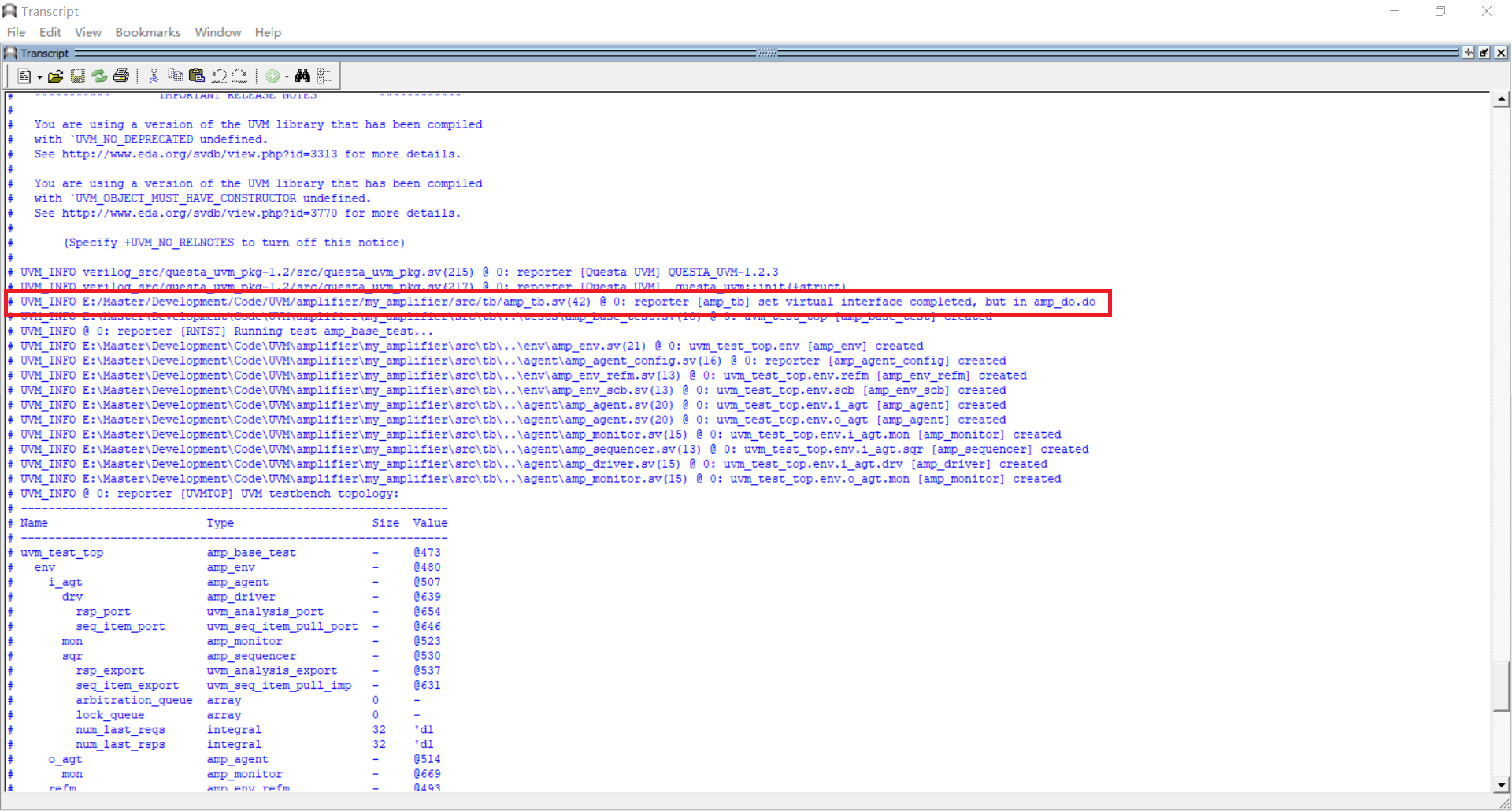

这个没啥好说的,命令为:quit -sim。 二、命令的打包有了以上几条命令,就能实现一个简单的命令脚本了。在sim文件夹下创建一个名为amp_do.do的文件,将上诉四条命令放入文件当中: 点击查看代码 # quit the latest sim quit -sim vlog -sv {E:/Master/Development/Code/UVM/amplifier/my_amplifier/src/tb/amp_tb.sv} vsim -novopt work.amp_tb run 100ns quit -sim#后面的内容为注释,不过必须单独为一行,不能跟在代码后面。 编辑好并保存后,修改amp_tb.sv中uvm_info的内容,然后在Questa Sim的软件中,依次选择File->Load->Macro File,加载写好的do文件,就能自动执行编译和运行了。

当然,也有命令行版本,命令为: QuestaSim> cd E:/Master/Development/Code/UVM/amplifier/my_amplifier/src/tb QuestaSim> do amp_do.do 三、简单的优化如果完全关闭Questa Sim,重新打开后再执行该do文件,会发现打印出了错误信息。错误原因在于未能找到DUT,这是由于没有编译DUT文件导致的。当重新编译了DUT文件,再执行do文件后,就没有报错了。 这一问题也说明,当前的do文件是不完善的,这里对其进行简单的完善: 点击查看代码 # quit the latest sim quit -sim .main clear set WORK_PATH E:/Master/Development/Code/UVM/amplifier/my_amplifier set TimeTag [clock format [clock seconds] -format "%H_%M_%S"] cd $WORK_PATH vlib ./work vmap work ./work file mkdir $WORK_PATH/log vlog -work work $WORK_PATH/src/DUT/*.v vlog -sv -l $WORK_PATH/log/vlog_$TimeTag.log $WORK_PATH/src/tb/amp_tb.sv vsim -novopt -c -l $WORK_PATH/log/vsim_$TimeTag.log work.amp_tb run 100ns quit -sim # quit -f其中: .main clear:清空命令行窗口中的已显示内容 set:设置路径变量,使用$使用该路径变量 clock:与时间有关的操作。seconds表示返回一个以秒为单位计时的时间戳,format表示格式化,最后的字符串表示格式化的形式,这里是以“时-分-秒”进行表示的。最终生成一个变量,交给TimeTag cd:进入该路径下的目录 vlib:在当前路径下创建一个工作库,编译后的文件会存放到该库中 vmap:映射逻辑库到指定的目录 file mkdir:在路径中创建一个文件夹 vlog:后面的选项表示将路径中的文件编译到指定的库中;选项-l表示将日志输出到后面的文件中,这一操作对vsim也是同理优化后的do文件,会在log文件夹中生成带时间信息的日志文件,这样就不需要在命令行查看输出日志了。此时文件目录结构变为: log src work其中的log文件夹内包含有此次运行脚本后生成的日志文件vlog_11_25_12.log和vsim_11_25_12.log。 运行过一次do文件后,在Questa Sim的命令行界面,按下键盘光标控制区的“上”键,就会出现执行do文件的命令: QuestaSim> do E:/Master/Development/Code/UVM/amplifier/my_amplifier/src/sim/amp_do.do 这就是为什么使用do文件进行仿真的原因:“上”键加回车键就能代替图形化界面的一堆操作,实在是非常方便。 当然,还能往这个do文件中添加一些其他命令来提高仿真效率,但现在这个do文件已经能够胜任大部分的工作了。之后的重心将回到验证代码上面。 本文来自博客园,作者:TooyamaYuuouji,转载请注明原文链接:https://www.cnblogs.com/Lexington-CV2/articles/16626728.html |

【本文地址】

今日新闻 |

推荐新闻 |