verilog语言中的门级描述、行为描述及测试验证 |

您所在的位置:网站首页 › 行为描述和数据流描述 › verilog语言中的门级描述、行为描述及测试验证 |

verilog语言中的门级描述、行为描述及测试验证

|

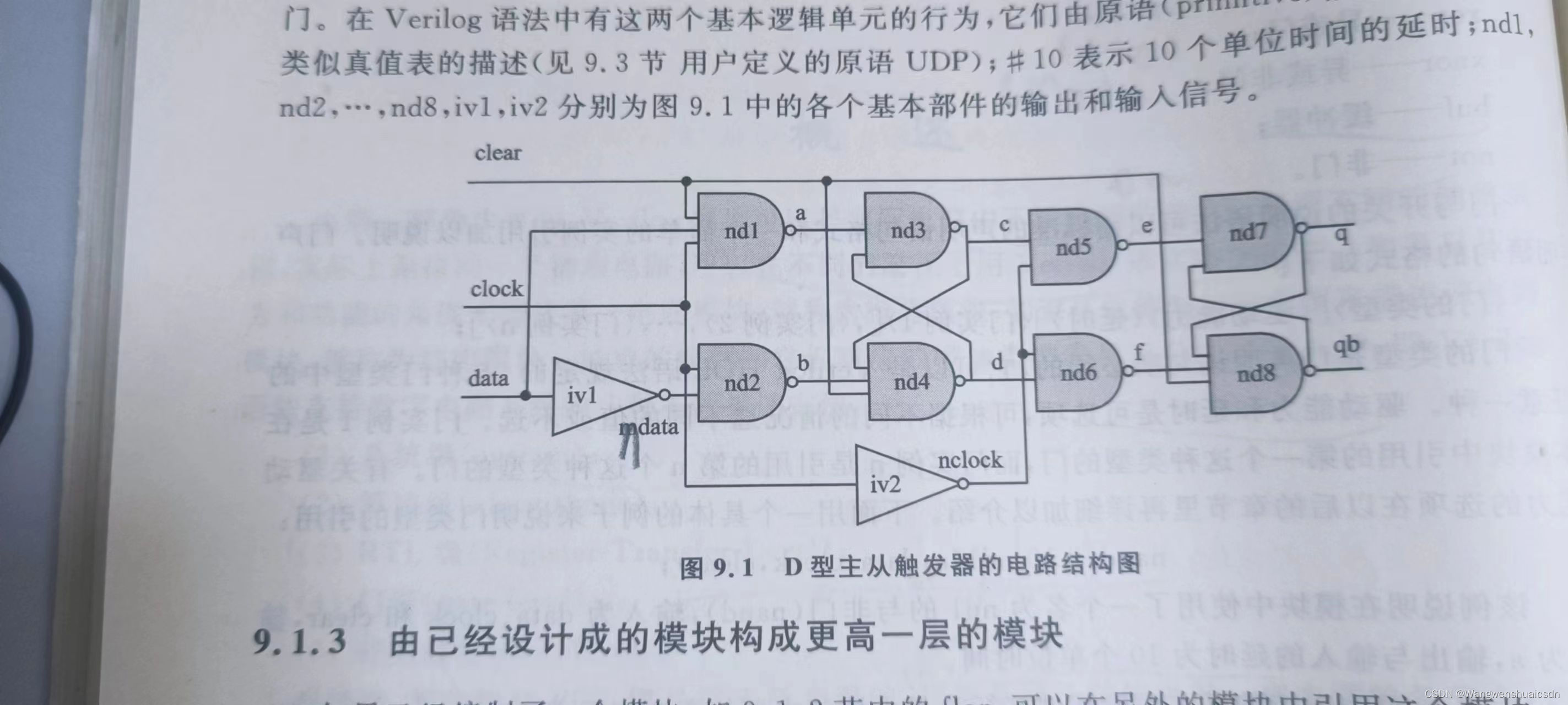

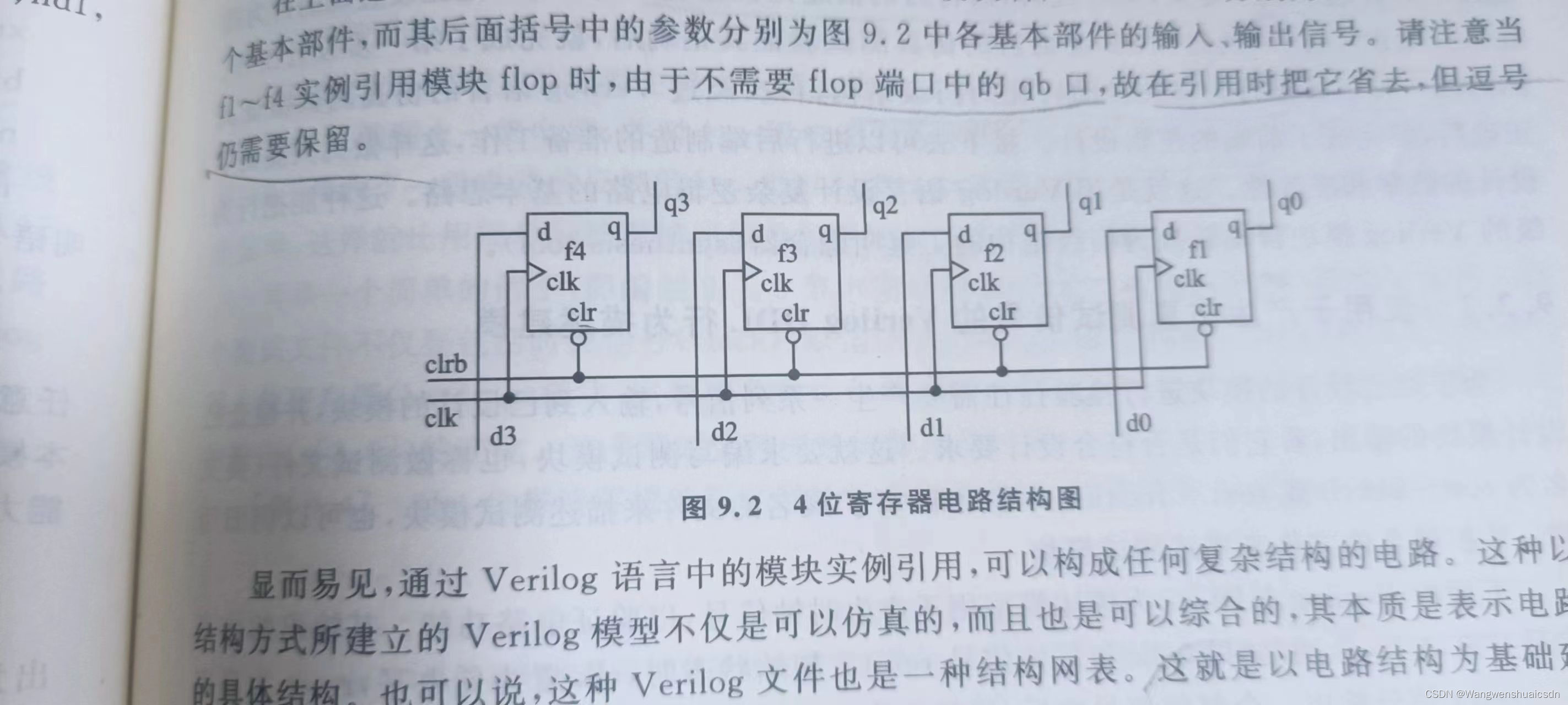

描述D型主从触发器模块的门级结构建模: module flop(data, clock, clear, q, qb); input data, clock, clear; output q, qb; // 批量定义门电路 nand #10 nd1(a, data, clock, clear), nd2(b, ndata, clock), nd4(d, c, b, clear), nd5(e, c, nclock), nd6(f, d, nclock), nd8(qb, q, f, clear); nand #9 nd3(c, a, d), nd7(q, e, qb); not #10 iv1(ndata, data), iv2(nclock, clock); endmodule在该模块中,flop定义了模块名,设计上层模块时可以用模块名调用模块; 创建的电路模型图如下: 引用已编制好的模块进行实例化,用于行为级描述: 使用触发器组成带清零端的4位寄存器(hardreg.v) `include "flop.v" module hardreg(d, clk, clrb, q); input clk, clrb; input[3:0] d; output[3:0] q; flop f1(d[0], clk, clrb, q[0], ), f2(d[1], clk, clrb, q[1], ), f3(d[2], clk, clrb, q[2], ), f4(d[3], clk, clrb, 1[3], ); endmodulehardreg定义了模块名,f1,f2,f3,f4分别为基本D触发器,在实例引用模块flop时,由于不需要flop端口的qb口,故在引用时省去,但逗号仍保留。

行为描述建模 用行为描述的方法来描述带清零端的4位寄存器: module hardreg(d,clk,clrb,q); input clk, clrb; input[3:0] d; output[3:0] q; reg[3:0] q; always@(posedge clk or posedge clrb) begin if (clrb) q |

【本文地址】

今日新闻 |

推荐新闻 |

更高一级建模:

更高一级建模: 通过模块之前的实例引用,可以构成任何复杂的电路,不仅可以用来仿真,也可以进行综合,本质是一种结构网表。

通过模块之前的实例引用,可以构成任何复杂的电路,不仅可以用来仿真,也可以进行综合,本质是一种结构网表。