数字IC中时钟频率和综合面积的关系 |

您所在的位置:网站首页 › 芯片面积大是优点吗 › 数字IC中时钟频率和综合面积的关系 |

数字IC中时钟频率和综合面积的关系

|

数字IC中时钟频率和综合面积的关系

综合RTL代码时发现,时钟频率设的越高,综合出的面积就越大,本文试着从MOS层面分析下原因 文章目录 数字IC中时钟频率和综合面积的关系一、逻辑门和MOS管二、电容角度分析三、电流角度分析四、总结五、参考资料 一、逻辑门和MOS管目前数字IC设计中,一般以逻辑门和寄存器作为最小单元来设计电路,而逻辑门一般由MOS管搭建;

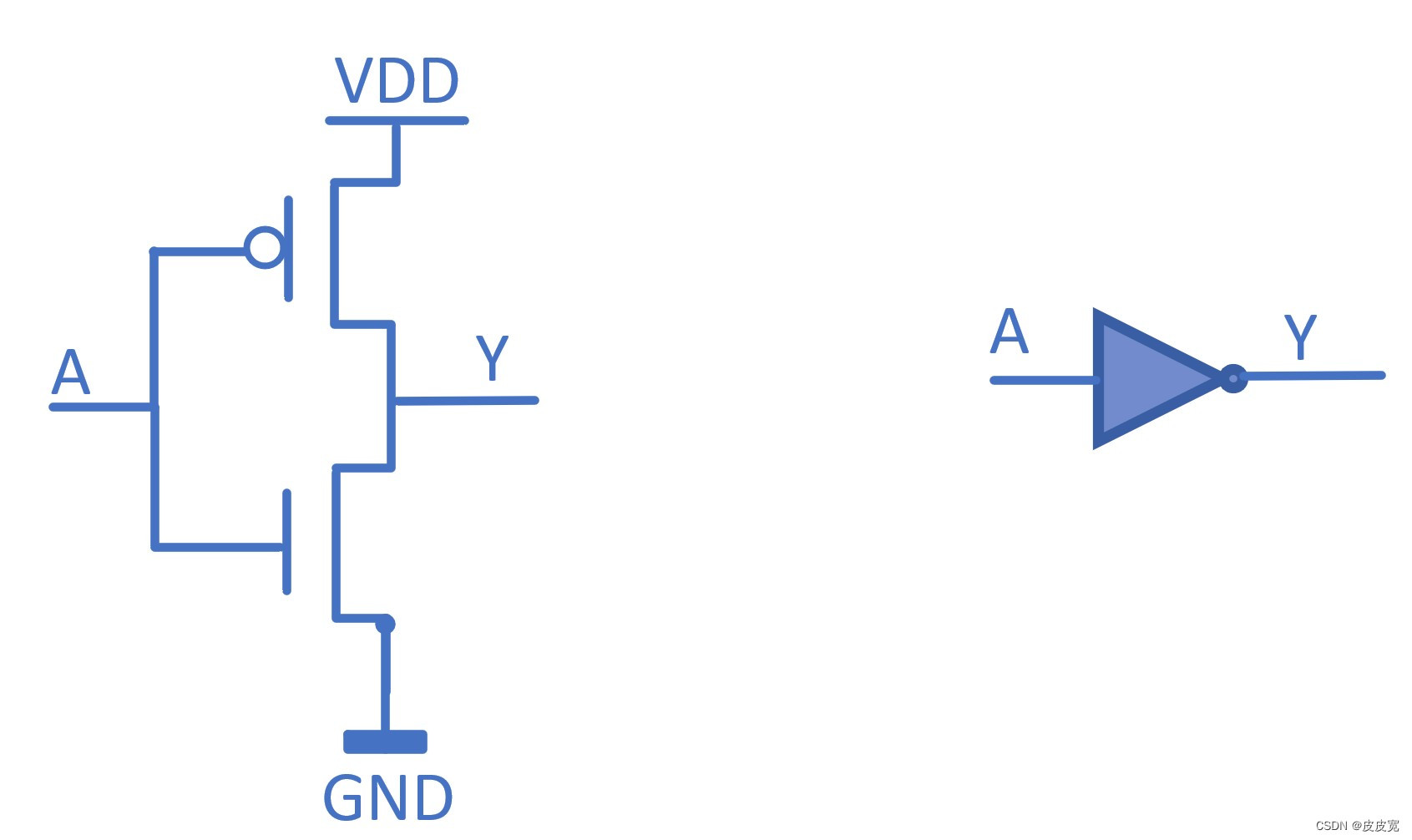

如图所示,一个反相器由一个NMOS管和PMOS管搭建;如果A输入的变换频率较高(电路工作频率较高),那么对应的Y也需要能快速的改变状态;我们下面分别从两种角度分析下这件事: 二、电容角度分析MOS管可以被等效为充放电的电容,工作频率较高时,我们就希望他能快速的充放电(改变输出电平); 举个例子,比如这样一个充放电的电容:

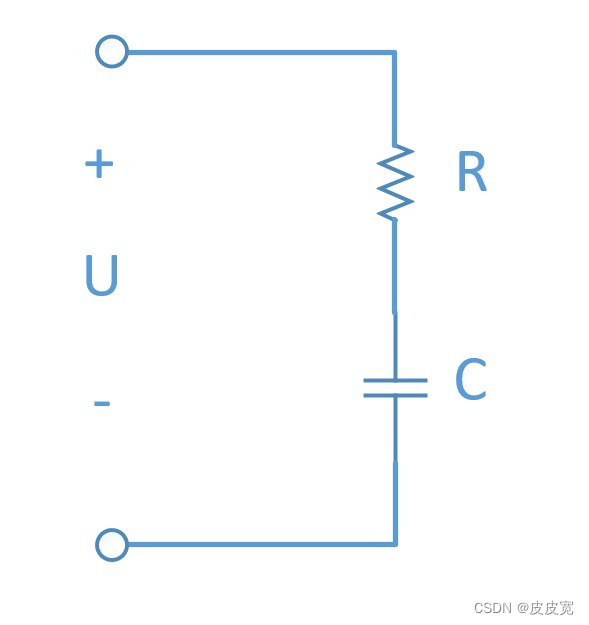

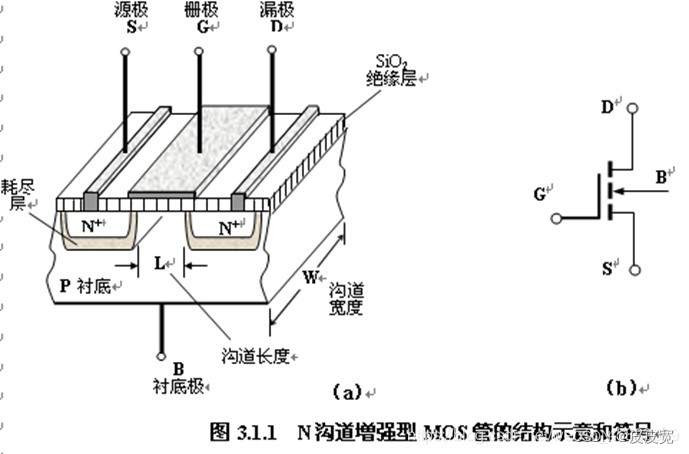

根据大一时学过的电路分析原理的知识(书上的例题),若起始设C两端电压为0,则其两端电压的充电公式为 U c = U ( 1 − e − t R C ) U_{c}=U(1-e^{-\frac{t}{RC}}) Uc=U(1−e−RCt) 电源U短路时,放电公式为 U c = U e − t R C ) U_{c}=Ue^{-\frac{t}{RC}}) Uc=Ue−RCt),也就是说其他条件不变的情况下,RC的值越大,电容的充放电速度就越慢; MOS管的最高工作频率计算公式(百度到的)为: f m = 1 2 π R O N C G f_{m} = \frac{1}{2\pi R_{ON}C_{G}} fm=2πRONCG1 和我们用等效电容分析的结论一样,MOS管电路的等效RC越大,其等效电容充放电的速度就越慢,最高工作频率也就越低。 MOS管的等效电容计算公式为: C G = E t W L C_{G} = \frac{E}{t}WL CG=tEWL, 由于 R O N R_{ON} RON也和尺寸有关,总的工作频率表达式如下所示: f m = u 2 π L 2 ( V g s − V T ) f_{m}=\frac{u}{2\pi L^{2}}(V_{gs}-V_{T}) fm=2πL2u(Vgs−VT) 其中,L是MOS管的沟道长度,L越小,MOS管的最高工作频率越高。

还有一种比较简单粗暴的分析,电流越大,电容/MOS管改变输出电压就越快,MOS管的宽长比W/L越大,电流越大,因此提高沟道宽度,就可以提高工作频率。因此频率较高时,综合出来的面积就会越大。 四、总结个人能力有限,只能分析到这一步了,网上没找到有别人分析过这个事,我这样分析也不知道对不对。 PS: 感谢评论区大佬答疑,我也更倾向于这种说法综合时应该会指定相应的library,一般这个工艺库中的特征沟道长度L应该是不太会变的;频率越快,综合出的面积越大,还是DC优化时面积换速度的结果。举个例子,加法器有多种实现方式,有的加法器需要的逻辑门更少,也就是面积较小,但是速度慢。有的加法器需要更多的逻辑门,面积大,但是速度快,DC会根据不同的频率去选择最合适的加法器。 五、参考资料【1】CSDN:电容的充放电过程及应用 【2】场效应晶体管及其放大电路 |

【本文地址】

今日新闻 |

推荐新闻 |

MOS管结构如上所示,图片来源参考资料【2】,沟道长度L越小,面积越大?这块还是不太理解

MOS管结构如上所示,图片来源参考资料【2】,沟道长度L越小,面积越大?这块还是不太理解