ESD笔记(二) |

您所在的位置:网站首页 › 芯片防护等级 › ESD笔记(二) |

ESD笔记(二)

|

文章目录

一:HBM & MM 测试1. 输入输出(I/O)管脚----电源(Power)管脚 ESD测试2. I/O管脚 ---- I/O管脚 ESD测试3. 电源管脚 ---- 电源管脚 ESD测试

二:CDM 测试三:lEC测试方法* ESD 等级划分四:传输线脉冲(TLP)测试

一:HBM & MM 测试

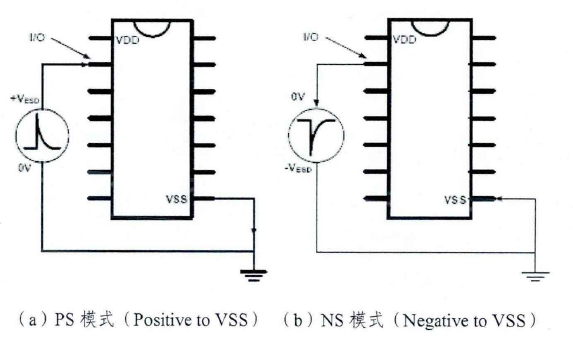

常用的HBM和MM测试设备为ZAPMASTER MK.2 SE; 下面,对这三种分类逐一讲解: 1. 输入输出(I/O)管脚----电源(Power)管脚 ESD测试针对一个I/O管脚,其对电源和地分别有正向和负向两种ESD应力模式,因此总共有四种I/O管脚—电源管脚的测试组合,如图1.8中的PS ( Positive toVSS )、PD ( Positive to VDD )、NS ( Negative to VSS)、ND (Negative to VDD )。 PS模式是当人体或机器上携带正电荷与I/O管脚相接触,同时VSS管脚接地时的放电情况。 NS模式是当人体或机器上携带负电荷与I/O管脚相接触,同时VSS管脚接地时的放电情况。 PD模式是当人体或机器上携带正电荷与I/O管脚相接触,同时VDD管脚接地时的放电情况。 ND模式是当人体或机器上携带负电荷与I/O管脚相接触,同时VDD管脚接地时的放电情况。

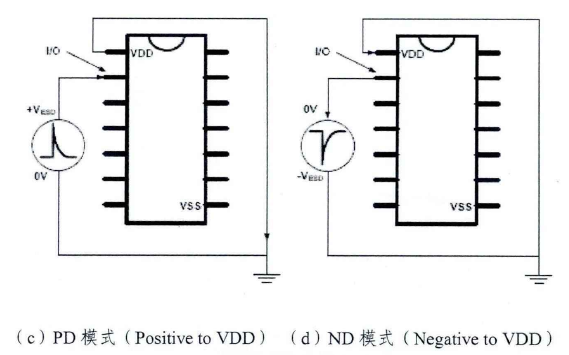

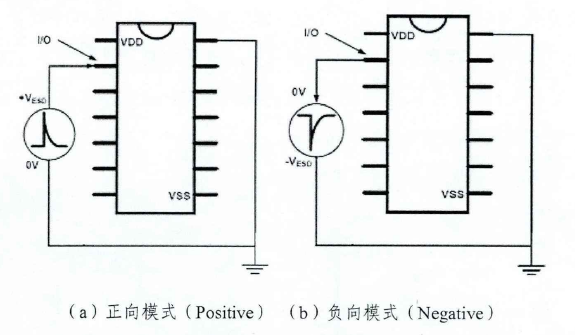

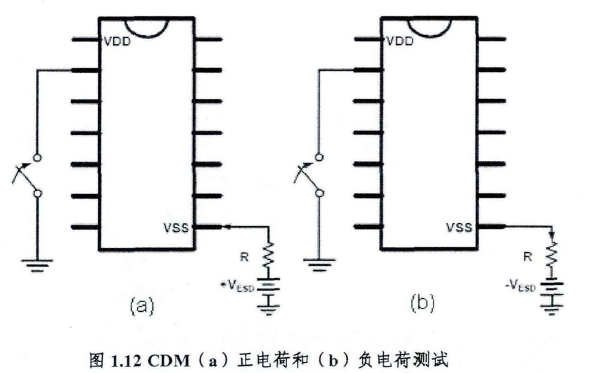

I/O管脚对I/O管脚进行测试时,也分为正向和负向两种ESD应力模式。 正向模式:当某一 I/O管脚进行I/O到I/O的正向应力测试时,其他所有I/O管脚、电源和地管脚浮空。 负向模式:当某一 I/O管脚进行I/O到I/O的负向应力测试时,同样其他所有I/O管脚、电源和地管脚浮空。 电源管脚的组合也有正向和负向模式的ESD测试组合。 正向模式:当携带正电荷的人或机器接触VDD电源管脚,而VSS管脚接地,其他管脚浮空的放电情况。负向模式:当携带负电荷的人或机器接触VDD电源管脚,而VSS管脚接地,其他管脚浮空的放电情况。备注:当芯片中存在多组不同的电源域时,各电源域之间也要分别进行正负向ESD应力测试。 CDM的放电模式与HBM和MM有所不同,CDM需要将芯片内部先携带有一定量的电荷后通过一个或多个管脚接地,ESD电流从芯片内部流向芯片外部的ESD过程。 测试设备的工作原理是通过直接探针接触或场感应的方法,使得整块芯片衬底带上正电荷或负电荷,通过对芯片的每一个管脚进行依次放电,来模拟CDM ESD事件。且对于每一个管脚来说,都要经过芯片内部正电荷放电和芯片内部负电荷放电两种模式。**(疑问:VSS为何接Vesd??) ** 以上的HBM、MM和CDM均为对芯片抗ESD能力的测试方法,当通过芯片ESD防护等级的芯片用在整机系统中,并不能保证整个电子系统在ESD应力下不发生故障,因此对于系统级的电子产品还需要IEC测试。常见设备为图1.13的静电放电枪,测试方法如图1.14所示,使用静电枪对电子产品直接进行接触式放电或隔着空气进行非接触式放电。

由于在设计初期,没有独立封装的形式,无法进行单独ESD器件的HBM、MM和CDM的测试。 传输线脉冲发生器(TLP,Transmission Line Pulsing system )应运而生,它可以使用探针对晶圆上的独立ESD器件进行触发电压(开启电压)、维持电压(回滞电压)、失效电流等重要ESD防护特性进行评估。 TLP成为业界在研发阶段评测ESD器件性能的主要手段,可以通过不同的上升沿和脉宽来调整TLP脉冲能量,从而等效为器件自身的抗ESD性能。 TLP技术通过利用 能量等效的原理可以用来模拟现实中的HBM和CDM波形。经学者研究:100ns的TLP脉冲的能量与相同电流峰值150ns脉宽的HBM波形所具有的能量等效,5ns的快速传输线脉冲发生器VFTLP, Very-Fast Transmission Line Pulsing system )脉冲与CDMESD波形具有相似的能量。 大多数TLP设备的上升时间可调,约为0.2 ~ 10ns,脉宽范围为10ns ~ 500ns。VFTLP系统的上升时间为0.2~ 2ns,脉宽为2 ~ 10ns; TLP根据其脉冲产生方式的不同,通常分为: TDR ( Time DomainReflection )、TDRT( Time Domain Reflection and Transmission )、TDT( Time DomainTransmission )和电流源(500Q阻抗)四种方式,其中TDR又可细分为:TDR-0和TDR-S, TDR-0方式待测器件上的电压和电流通过直接测量得到,TDR-S方式待测器件上的电压和通过的电流是通过计算得到。

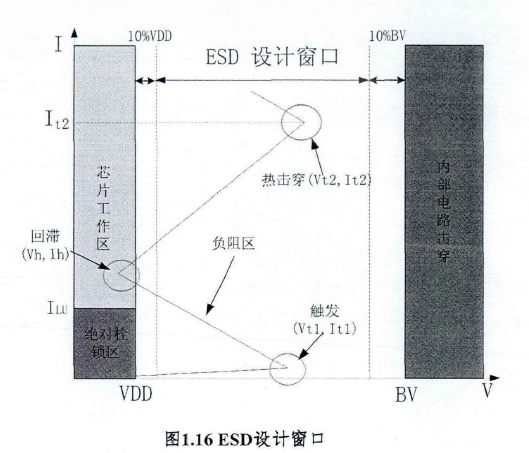

如图1.16所示为一条回滞类ESD器件的TLP曲线和ESD窗口的定义,以电压为横坐标,整个坐标轴被分为三个区域,低于芯片工作电压(VDD)的为芯片工作区,高于被保护电路的击穿电压(BV)为内部电路击穿区,除去10%的安全裕量后中间的区域(1.1 X VDD ~ 0.9 X BV)为该电路的安全ESD设计窗口。 BV对输入端来说一般是所接的MOS管的栅氧击穿电压,对输出端来说该电压是输出级驱动管的漏级击穿电压。在大多数字I/O (input/output)中,输入与输出功能做在同一个单元内,同一个端口既可以用作输入,也可以用作输出,那么ESD设计窗口的上限由核心电路栅氧击穿电压和漏极击穿电压最小值所决定的。当ESD器件的I-V曲线符合ESD设计窗口时,表明ESD器件在芯片正常工作电压下不会由于意外开启导致栓锁效应(latch-up),在ESD应力下也能保护内部电路不会击穿。 因此对于一个ESD防护器件的TLP曲线,有三个关键坐标点是我们逐需关注的,触发点(Vtl,Itl )、回滞点(Vh, Ih)和失效点(VU,It2),触发点决定了 ESD防护器件的有效开启特性,回滞点决定了 ESD防护器件的抗H锁特性,失效点决定了该ESD防护器件的鲁棒性。 由于对于10ns脉冲上升时间,100ns脉宽的TLP能量等效于HBM ESD能量,其测得的失效电流It2与HBM防护等级一般有以下关系:器件HBM等级 = TLP失效电流 X 1500Q (人体等效电阻) |

【本文地址】

根据所编写的程序可以快速自动的对所有芯片管脚组合进行ESD应力测试。由于芯片的每个管脚均有遭受正电荷或负电荷ESD的可能,因此我们需要对每一组管脚分别进行正向ESD应力和负向ESD应力的测试。根据管脚分组的种类,一般可分为:

根据所编写的程序可以快速自动的对所有芯片管脚组合进行ESD应力测试。由于芯片的每个管脚均有遭受正电荷或负电荷ESD的可能,因此我们需要对每一组管脚分别进行正向ESD应力和负向ESD应力的测试。根据管脚分组的种类,一般可分为: