数电Day06:主从触发器和边沿触发器,触发器的逻辑符号,时序波形 |

您所在的位置:网站首页 › 芯片表示符号 › 数电Day06:主从触发器和边沿触发器,触发器的逻辑符号,时序波形 |

数电Day06:主从触发器和边沿触发器,触发器的逻辑符号,时序波形

|

目录 #主从触发器和边沿触发器 #主从触发器 #边沿触发器: #触发器的逻辑符号以及时序图 #时序波形 #主从触发器和边沿触发器首先,只要钟控信号为0,钟控触发器就是保持状态。 只有当钟控信号为1的时候,输入信号才能使得触发器发生置0,置1,反转等功能。

例如当钟控JK触发器jk均为1的时候是翻转功能,那么在钟控信号为1的时间段内,输出Q会不断的翻转翻转翻转再翻转。 这样就达不到我们精确控制电路状态的目的。 #主从触发器如何避免这种空翻现象呢?这就产生了主从触发器。 首先,主从触发器都是D触发器(吃什么拉什么,次态=输入) 其次,在钟控信号上加一个反相器,保证主触发器和从触发器的钟控信号一定相反。 当钟控信号为为1时,主触发器时钟有效(即输入能发挥功能),也就说输入可以被原模原样送到从触发器 但是从触发器的时钟信号却为0,因此时钟无效(为保持状态),即不管输入为啥,次态都不受其影响,一直等于现态。 主从触发器奥妙在于钟控信号1变0前那一瞬间,只有这一瞬间的的输入信号D,才能经过主从触发器的两道大肠,从触发器给拉出来。此后主触发器为保持状态,所以从触发器一直吃到的就是那一瞬间的D,一直将这个D给拉出出来。 即此后一直保持,直到遇到下次1变0的一瞬间。

即只有在上升沿,jk的输入才会发生作用。 总结:边沿触发器,即没有遇到有效边沿时,为保持状态 遇到有效边沿时,输入才能发生对应的功能。 #触发器的逻辑符号以及时序图

注意CLK高电平有效,就代表高电平时RS可以发挥作用,低电平时触发器为保持状态。 钟空RS触发上下两个异步set 和reset是不收CLK控制的。因此他们具有最高优先权

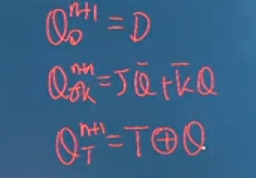

复习:常用触发器的触发方程,注意:只有当触发信号有效时(有效电平/有效边沿),我们才去计算这个触发方程。

可以假设上升沿到来之前Q为0,也可以像上图画一个阴影表示Q为任意。

注意:C是异步Reset,优先级最高,不收CLK控制。可以在波形图中将异步信号有效时的次态先画出来。 |

【本文地址】

当触发信号无效的时候,触发器都是保持状态。次态都等于现态。

当触发信号无效的时候,触发器都是保持状态。次态都等于现态。