【微机原理作业】存储器扩展 |

您所在的位置:网站首页 › 芯片组成存储器 › 【微机原理作业】存储器扩展 |

【微机原理作业】存储器扩展

|

文章目录

一.作业要求二.8086芯片介绍1.CPU提供的信号线2.存储器的奇偶分体

三.2764芯片介绍1.容量2.引脚

四.6264芯片介绍1.容量2.引脚

五.思路1.确定所需2764和6264的个数2.确定ROM和RAM地址范围3.确定译码电路的接法

六.存储器的扩展示意图七.proteus 仿真原理图

一.作业要求

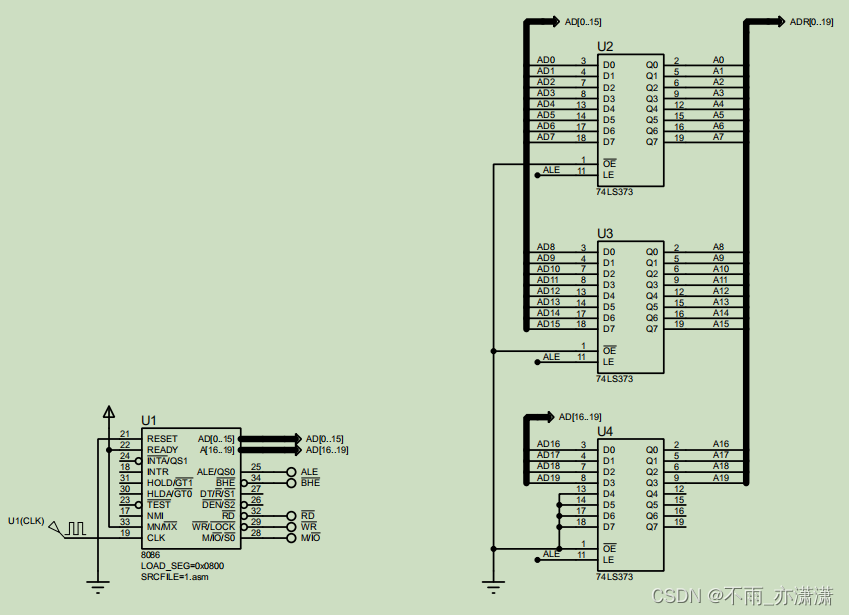

利用 2764 和 6264 在 8086 最小模式下扩展 64K ROM 和 64K RAM,给出其电路连接和地址范围。 二.8086芯片介绍 1.CPU提供的信号线(1)D0 ~ D15 16位数据线 (2)A0 ~ A19 20位地址线 (3)M / #IO 存储器或I/O端口访问信号 (4)#RD 读信号线 (5)#WR 写信号线 (6)#BHE 总线高位有效信号

8086系统的存储器采用分体结构,即1MB的存储空间分为两个512KB的存储体,一个存储体包含偶数地址,另一个存储体包含奇数地址。 偶存储体同8086的低8位数据总线D0~D7相连,奇存储体同 8086的高8位数据线D8~D15相连,地址总线的A1~A19同两个存储体中的地址线A0~A18 相连,最低位地址线A0和总线高允许BHE相互配合,使CPU可以访问一个存储体中的1字节或同时访问两个存储体中的1个字。

2764属于27系列的EPROM芯片,“27”后面的数字除以8就是容量,单位为KB,2764的容量就是8KB. 2.引脚

6264属于64系列的SRAM芯片,“64”后面的数字除以8就是容量,单位为KB,6264的容量就是8KB. 2.引脚

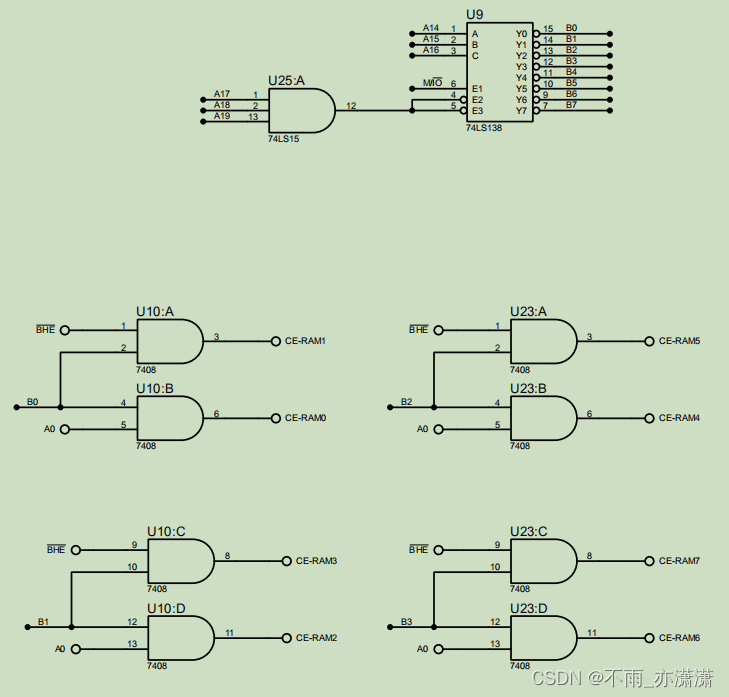

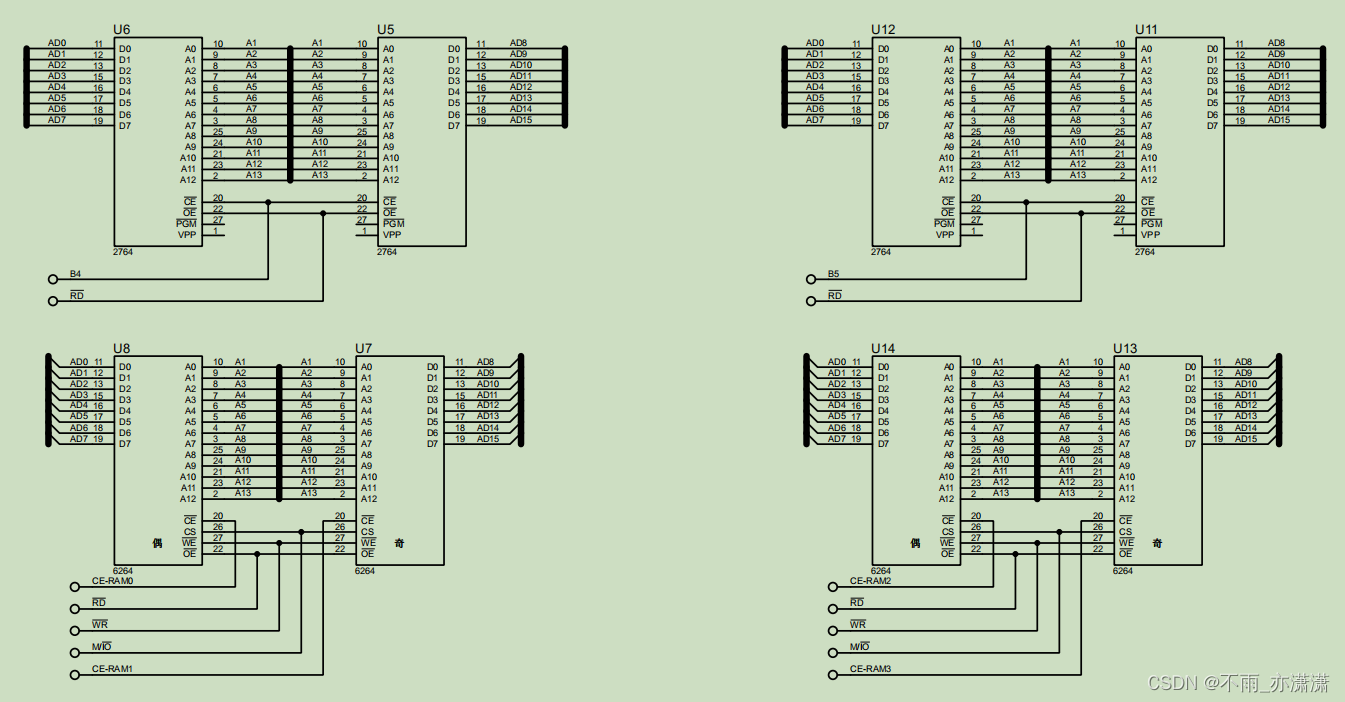

由于 2764 和 6264 的容量均为8KB,拓展 64KB ROM 和 64KB RAM ,需要 64/8=8 片2764和 64/8=8 片6264。 2.确定ROM和RAM地址范围00000H ~ 01FFFH 即为8K (1)从00000H开始的 64K RAM,地址范围 00000 ~ 0FFFFH A19A18A17A16A15A14A13A12A11A10A9A8A7A6A5A4A3A2A1A0最小地址序号00000000000000000000最大地址序号00001111111111111111分为四组: 组别地址范围第一组00000H ~ 03FFFH第二组04000H ~ 07FFFH第三组08000H ~ 0BFFFH第四组0C000H ~ 0FFFFH(2)从10000H开始的 64K ROM,地址范围 10000 ~ 1FFFFH A19A18A17A16A15A14A13A12A11A10A9A8A7A6A5A4A3A2A1A0最小地址序号00010000000000000000最大地址序号00011111111111111111分为四组: 组别地址范围第一组10000H ~ 13FFFH第二组14000H ~ 17FFFH第三组18000H ~ 1BFFFH第四组1C000H ~ 1FFFFHROM 和 RAM 在地址变化过程中高位地址 A19-A16 均保持不变,说明片选信号由 A19-A16产生,CPU的 A15-A0 作为片内单元的译码线,可以寻址64KB(216)。 当 A16 = 0 时,针对 RAM 的片选信号有效; 当 A16 = 1 时,针对 ROM 的片选信号有效。 3.确定译码电路的接法在译码电路部分,采用 74LS138 芯片提供片选信号。 74LS138 功能表如下: B0、B1、B2、B3接RAM,B4、B5、B6、B7接ROM 输出引脚标号A16A15A14最小地址序号最大地址序号B00000000H3FFFHB10014000H7FFFHB20108000HBFFFHB3011C000HFFFFHB410010000H13FFFHB51011400H17FFFHB61101800H1BFFFHB71111C000H1FFFFH

RAM 与 ROM 的接口电路不同,CPU对 RAM 不仅要进行16位读操作,还要进行写操作。写操作有3种类型:写16位数据、写低8位数据和写高8位数据。 对于写16位数据,RAM区的奇片和偶片同时工作; 对于写8位数据,RAM区的奇片和偶片只有一片工作。 最低位地址线A0和总线高允许BHE相互配合,可以实现上述的三种操作。

ROM扩展示意图: RAM扩展类似,只是6264芯片多一个写控制 #WE 引脚,需要与CPU的写信号线 #WR 相连,其次6264的片选端 #CS 除了和74LS138的输出引脚B0、B1、B2、B3相连,还要考虑 #BHE 和 A0,用来区分奇偶片。 七.proteus 仿真原理图

|

【本文地址】

今日新闻 |

推荐新闻 |

2764的主要信号线: (1)总线: D0 ~ D7 8位数据线 A0 ~ A12 13位地址线(要实现对8KB地址寻址,需要13根地址线进行译码) (2)控制: #OE 读控制 #CE 使能(片选信号输入)

2764的主要信号线: (1)总线: D0 ~ D7 8位数据线 A0 ~ A12 13位地址线(要实现对8KB地址寻址,需要13根地址线进行译码) (2)控制: #OE 读控制 #CE 使能(片选信号输入) 6264的主要信号线: (1)总线: D0 ~ D7 8位数据线 A0 ~ A12 13位地址线 (2)控制: #WE 写控制 #OE 读控制 #CE 使能 #CS 片选(片选信号一般由高位地址产生)

6264的主要信号线: (1)总线: D0 ~ D7 8位数据线 A0 ~ A12 13位地址线 (2)控制: #WE 写控制 #OE 读控制 #CE 使能 #CS 片选(片选信号一般由高位地址产生) M/#IO 与 高电平使能端 相连,A19、A18、A17 经过 74LS15 与 低电平使能端 相连,3个选择输入端与地址线连接如下。

M/#IO 与 高电平使能端 相连,A19、A18、A17 经过 74LS15 与 低电平使能端 相连,3个选择输入端与地址线连接如下。