一种高精度过流保护电路的设计 |

您所在的位置:网站首页 › 考研政治多会儿准备 › 一种高精度过流保护电路的设计 |

一种高精度过流保护电路的设计

|

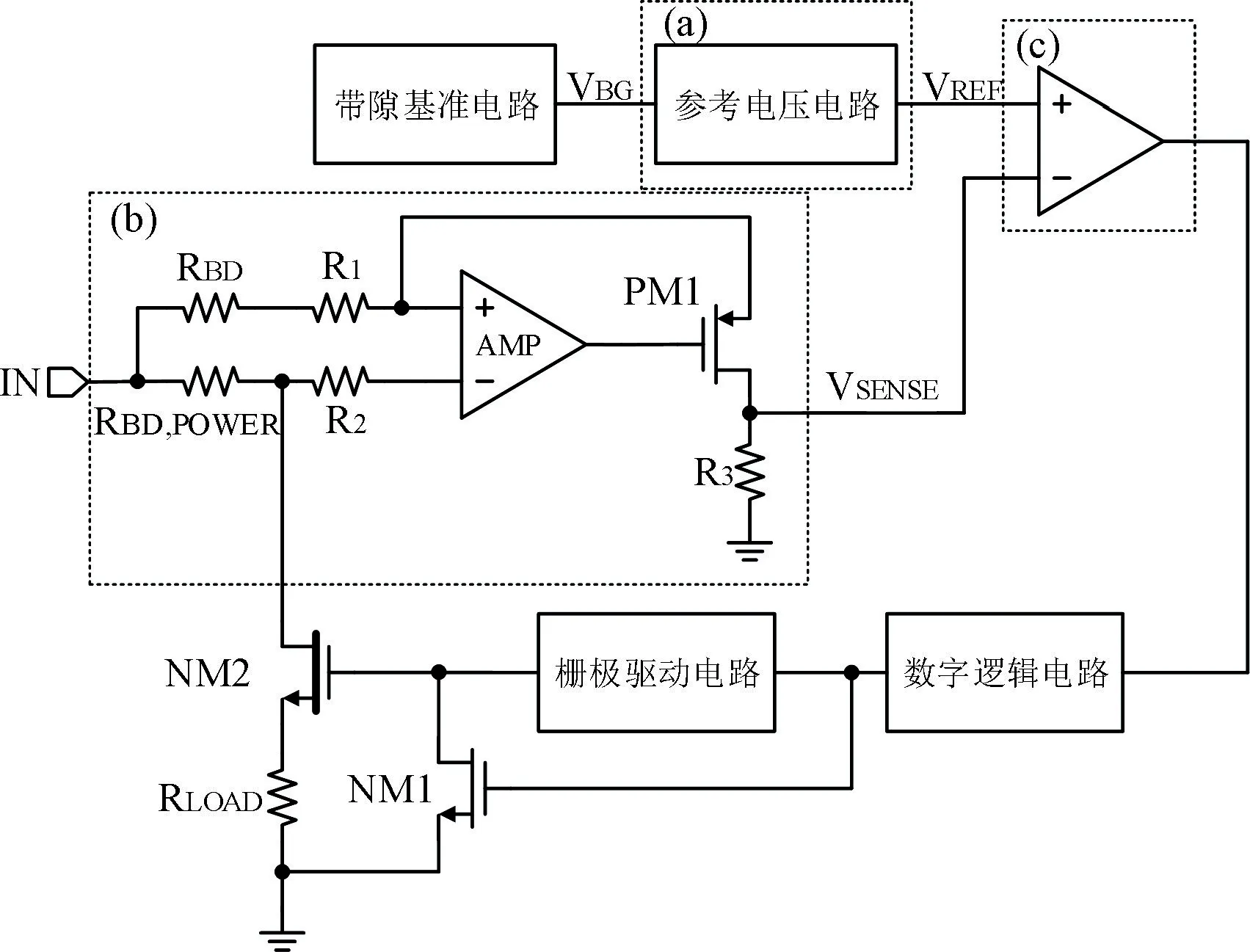

张金洋 ,汪西虎 ,董振斌 ,王江涛 ,徐佳豪 (1.西安邮电大学 电子工程学院,陕西 西安 710121;2.上海电子线路智能保护工程技术研究中心,上海 201202;3.上海维安电子有限公司,上海 201202) 随着便携式电子产品的迅速发展,锂电池相较于其他类型电池有着诸多优势,成为了多数电子产品的供电电源,然而锂电池对于工作环境较为敏感,当锂电池充电电流过大,会对电极材料结构产生较大的影响,造成电池极化严重。为此,锂电池在实际应用中一般都会有保护电路与其搭配使用[1-3]。在传统电流采样方式中,较为常见的有两种,分别为电阻采样和SenseFET 采样[4-7]。功率管串联电阻采样提供高精度电流采样的同时,引入了额外的导通电阻及功耗,而SenseFET 采样方式虽然能够避免额外导通电阻及功耗的产生,但是其受限于匹配误差,采样精度不高。文献[8]通过功率管导通电阻实现电流采样,避免了传统采样电阻进行电流采样带来的额外功耗,但功率管导通电阻随工艺及温度变化较大,精度不高,且过流值的设定较为复杂;文献[9]设计了一种参考电压由可调电流源在栅漏短接MOS 管得到的过流保护电路,用于使参考电压不受外界因素影响,虽然在一定程度上提高了精度,但是其利用SenseFET 进行电流采样,采样管与功率管在实际制造过程中会产生失配,同样会对精度造成较大的影响。 鉴于此,本文提出了一种适用于锂电池保护芯片的过流保护电路,当采样电流超过设定阈值电流时,关闭栅极驱动电路并拉低功率管栅端电压,从而切断充电电路与锂电池之间的连接通路,起到保护锂电池及后端设备的目的。芯片采用铜丝键合技术[10],直接利用键合丝实现高边电流采样,在保证高精度电流采样的同时又不引入额外的导通电阻;电路设计预留修调控制位,可用于过流阈值的调整以及键合丝工艺误差的校正;整体电路过流阈值设置简单,具有良好的线性关系。 1 电路结构及工作原理图1 为本文提出的过流保护电路,电路由三部分组成,分别为(a)参考电压电路、(b)采样及预放大电路和(c)比较器电路,其基本工作原理:参考电压电路借助带隙基准电路产生的受工艺及温度影响不大的基准电压[11-12],利用自身运算放大器所构成的负反馈结构产生参考电压;NM2、RLOAD分别为功率管及后端锂电池等效负载电阻,采样及预放大电路将功率管电流导致的键合丝压降微小变化放大;比较器电路对参考电压电路提供的参考电压与采样及预放大电路提供的采样电压进行比较,当触发过流保护时,通过数字逻辑电路关闭栅极驱动电路,同时MOS 管NM1 导通,将功率管栅端电压拉低,从而起到关闭功率管,限制电流、保护锂电池的目的。

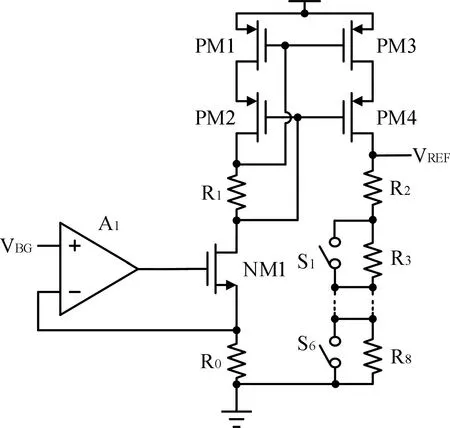

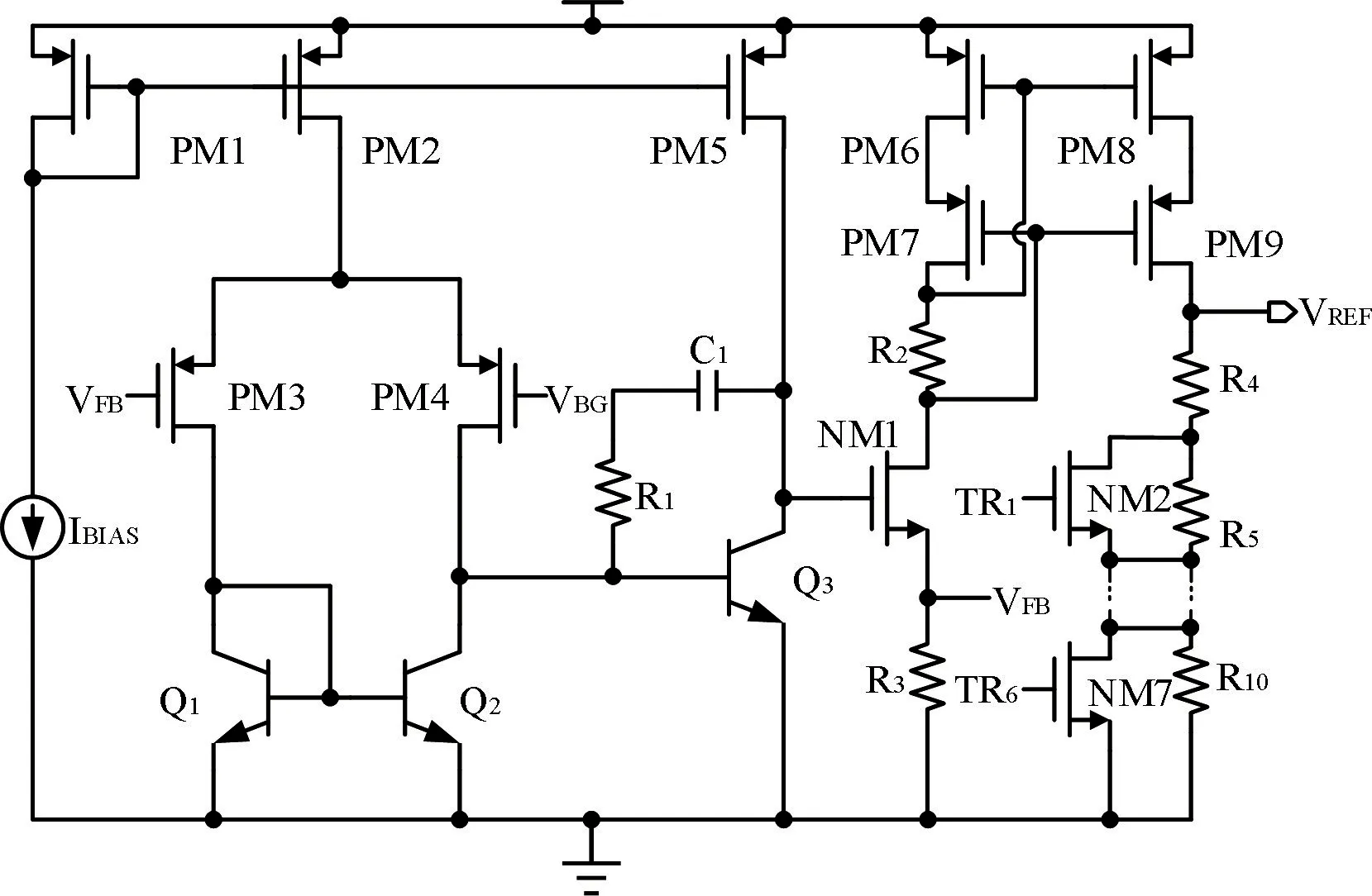

图1 过流保护电路原理图Fig.1 Schematic diagram of over-current protection circuit 参考电压电路简化结构如图2 所示。运算放大器A1与PM1、PM2、R1、NM1、R0构成负反馈环路,电阻R0上的电压等于基准电压,即:

图2 参考电压电路简化结构图Fig.2 Simplified diagram of reference voltage circuit

因此流经电阻R0的电流为:

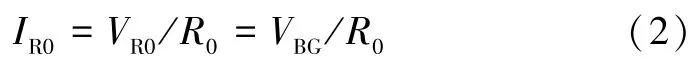

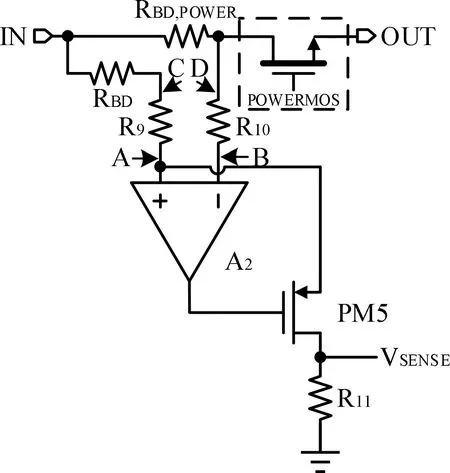

R0电流作为参考电流通过PM1~PM4、R1组成的自偏置低压共源共栅电流镜镜像复制到可调电阻网络R2~R8,即可得到参考电压。 采样及预放大电路简化结构如图3 所示。A2为预放大电路,R9=R10,RBD,POWER为连接芯片内部功率管输入端PAD 的键合丝等效电阻,其阻值为15 mΩ,RBD为连接C 点PAD 的键合丝等效电阻,阻值为50 mΩ,二者另一端均接芯片外部引脚IN。在电路正常工作或发生过流情况时,RBD所处支路电流均为μA 量级,因此C 点电压近似等于IN 端电压,即:

图3 采样电路简化结构图Fig.3 Simplified diagram of sensing circuit

当通过功率管的电流很小时,同理可视D 点电压近似等于IN 端电压。利用运算放大器“虚短”特性,A、B 两点电压相等,因此:

进而由“虚断”特性,可得:

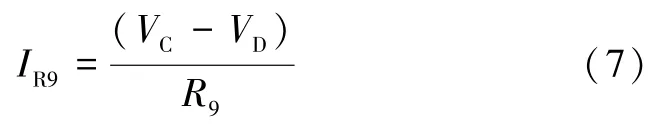

当通过功率管的电流增大时,RBD,POWER两端压降升高,D 点电位下降,由“虚断”原理可得D 点电压等于B 点电压,同时借助上述“虚短”特性,B 点电压等于A 点电压,则R9上的电流为:

因此流经功率管电流使得键合丝自身等效电阻在D 点形成的电压变化,经预放大电路可得:

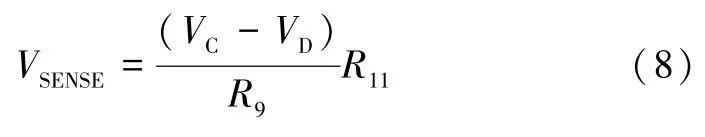

由式(8)可知,采样及预放大电路将C、D 两点之间的微小电压变化放大R11/R9倍,可通过调节R11与R9比例关系灵活调整预放大倍数,且同时能够实现电源轨范围内的任意放大倍数。 比较器电路简化结构如图4 所示。COMP 为比较器电路;SMT、INV 分别为用于整形的施密特电路及反相器电路;电容C′构成高频快速通路,提高响应速度;参考电压VREF与采样放大后的电压VSENSE进行比较,当VSENSE大于VREF时,输出高电平,此时代表过流保护触发,同理可得非过流情况下,比较器电路输出低电平。

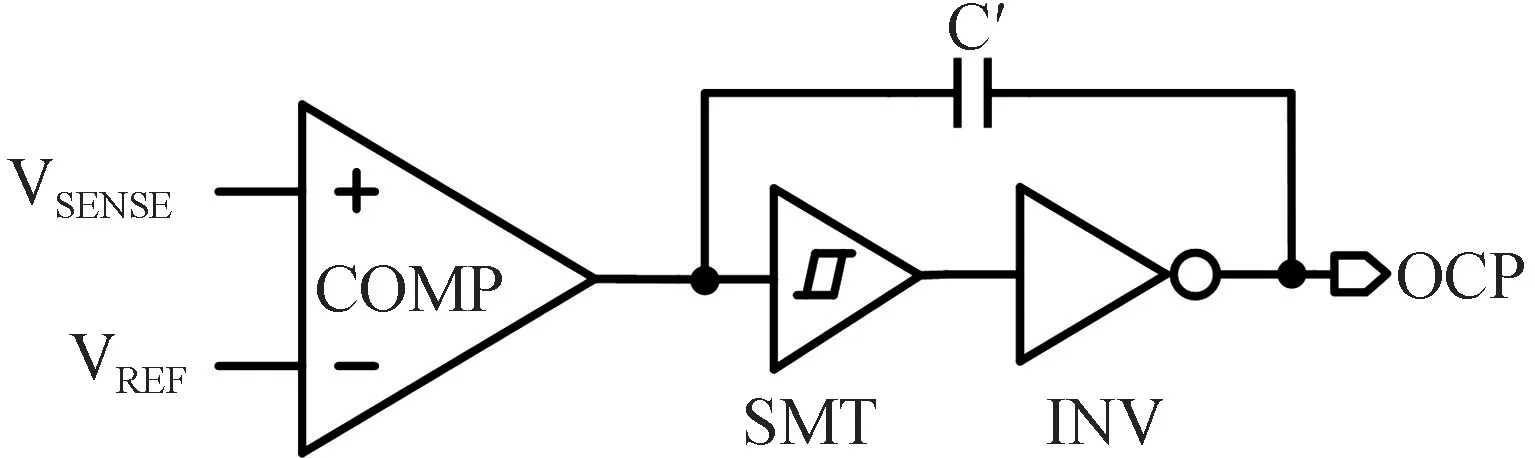

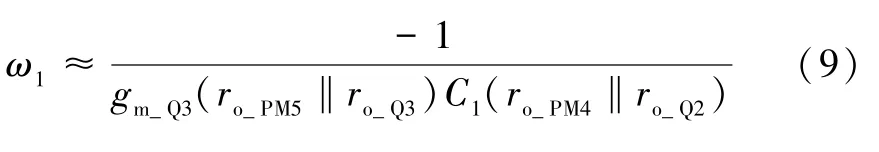

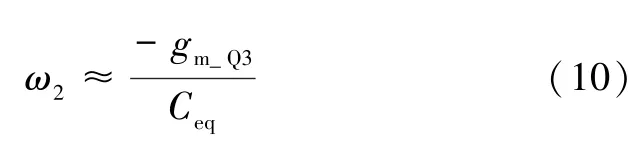

图4 比较器电路简化结构图Fig.4 Simplified diagram of comparator 2 电路设计2.1 参考电压电路图5 为本文参考电压电路具体设计。PMOS 管PM1、PM2、PM5 为电流镜结构,为运算放大器提供正常工作时所需要的偏置电流;PM3、PM4 为运算放大器输入对管,既能够拥有相比于NMOS 管更低的噪声和更高的转换速率,又能减小输入对管衬底偏压效应;三极管Q1、Q2组成电流镜结构作为运算放大器的有源负载,可以得到比MOS 管电流镜更大的等效交流阻抗,同时三极管结构相较于MOS 管有着更小的1/f噪声(闪烁噪声),其呈现在输入端的参考噪声电压要小得多;NPN 型三极管Q3构成了两级运算放大器第二级,得益于共射极结构,输出电压摆幅接近全摆幅,同时自身增益比MOS 管或PNP 型三极管要大得多,而第二级放大器产生的噪声对电路的影响可以等效为输入参考噪声电压,其大小等于第二级放大器输出噪声电压与一、二级运算放大器增益乘积的比值,由于第一级运算放大器的增益较大,因此第二级运算放大器等效输入噪声对电路的影响可以忽略不计;调零电阻R1、电容C1组成密勒补偿结构,引入左半平面零点提高环路相位裕度及频率稳定性。

图5 参考电压电路Fig.5 Reference voltage circuit 补偿后的主极点频率近似为:

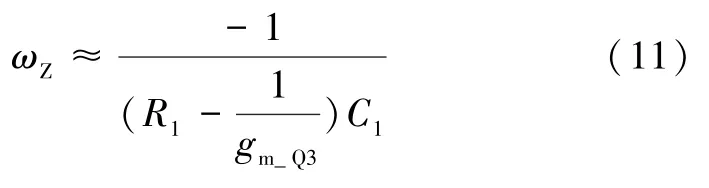

式中:gm_Q3为三极管Q3的等效跨导;ro_i为对应MOS管及三极管的等效输出阻抗。 次极点频率为:

式中,Ceq为MOS 管NM1 的栅端等效寄生电容。 调零电阻对零点补偿后,零点对应频率为:

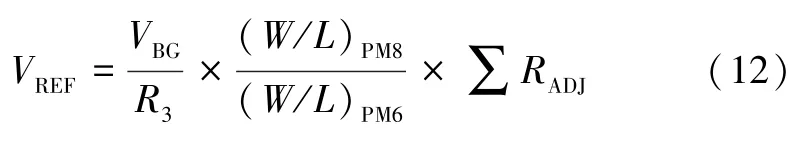

PM6、PM7、R2组成自偏置低压共源共栅电流镜结构,减少偏置电压的产生,同时抑制沟道长度调制效应影响;NM2~NM7 用于改变接入电阻数量;为保证电路良好的匹配性,减小失配误差,R2~R10为同种类型的多晶硅电阻,但对应的阻值大小存在差异;利用修调技术控制NM2~NM7 导通状态,以此实现阈值设定及键合丝误差校正功能,参考电压输出点到地等效电阻可用∑RADJ表示。 负反馈结构使得VFB等于VBG,R3电流通过电流镜结构镜像复制到可调电阻网络,从而使得VREF参考电压公式可表示为:

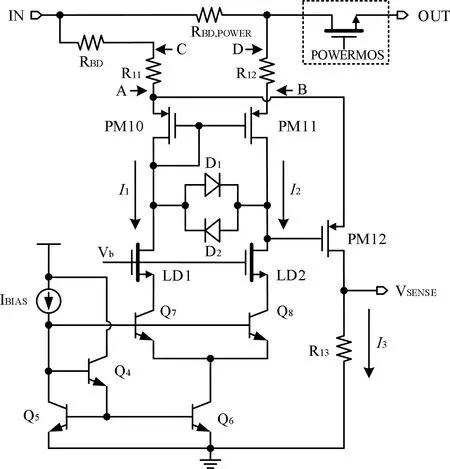

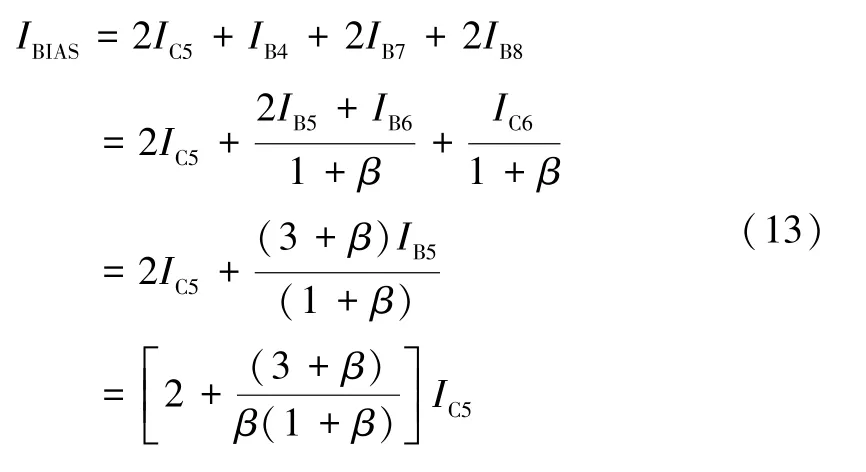

由式(12)可知,在实际应用中,调节R3与∑RADJ比例关系,即可得到不同的参考电压值,具有较强的灵活性。 2.2 采样及预放大电路采样及预放大电路具体电路设计如图6 所示。PM10~PM12、二极管D1~D2、DMOS 管LD1~LD2、Q6~Q8构成预放大电路;R11=R12,RBD,POWER为键合丝等效电阻,其作为采样电阻;三极管Q4、Q5、Q6为β-helper 电流镜结构[13],为预放大电路提供偏置电流,射极跟随器Q4的引入用于减小Q5、Q6基极电流对电流复制所造成的影响,提高镜像复制电流的精度,Q4~Q6发射区面积之比等于1 ∶2 ∶1,Q5集电极电流IC5与IBIAS关系式为:

图6 采样及预放大电路Fig.6 Sensing and preamplifier circuit

本文电路设计中,NPN 三极管采用纵向三极管,其β值约为20,因此:

Q5与Q6基极-发射极电压相等,即:

考虑Q5、Q6发射区面积比例关系,可得Q5、Q6集电极电流关系式:

同时三极管结构电流镜在一定程度上能够实现对温度的补偿,由Q4、Q5构成负反馈环路,抑制偏置电流随温度改变而改变;三极管Q7、Q8在直流条件下,保证I1、I2两路电流相等,交流情况下提供相较于MOS 管更大的交流输出阻抗;LD1、LD2 为高压N型DMOS,用于保证电路工作在高压情况下,低压器件能够工作在安全电压范围内,拓宽电路应用场景。Vb为大小合适的偏置电压,使得LD1、LD2 在电路工作时导通。 在实际芯片制造中,由于工艺偏差会造成PM10、PM11 失配现象的发生,使得预放大电路在C、D 两点电压相等时,VSENSE不为0,或者是对于输入端微小的电压变化,不能准确放大到指定倍数,影响电路精度[14]。为此,在电路设计过程中,预放大电路采用完全对称结构,引入共模负反馈环路,用于减少失配所造成的影响,确保A 点与B 点电压相等。R11、R13、PM10、PM11、PM12、Q6~Q8组成负反馈环路,当A点电压高于B 点电压时,PM10 电流增大,对应其栅端电压会有一定程度增加,因此PM11 电流减小,PM12 栅端电压减小,PM12 电流增大,R11上压降升高,从而使得A 点电压下降,缩小A、B 两点电压差,达到抑制失配对运算放大器带来的影响,保证A、B两点电压相等;同理,当B 点电压高于A 点电压时,PM12 栅端电压增大,进而其电流减小,R11上分配的电压减小,A 点电压抬升,实现同样的效果。二极管D1、D2构成钳位电路,当E 点电压与F 点电压差值等于二极管导通电压时,D1或D2导通,产生电流通路,平衡二者电压,以此防止预放大电路两条支路压差过大导致的精度下降。 A、B 两点电压可用公式表示为:

借助运算放大器“虚短”特性可得:

采样电压关系表达式为:

由于I1、I2电流量级为μA 级,且RBD、RBD,POWER等效电阻为mΩ 级,因此可将VSENSE表达式近似等价为:

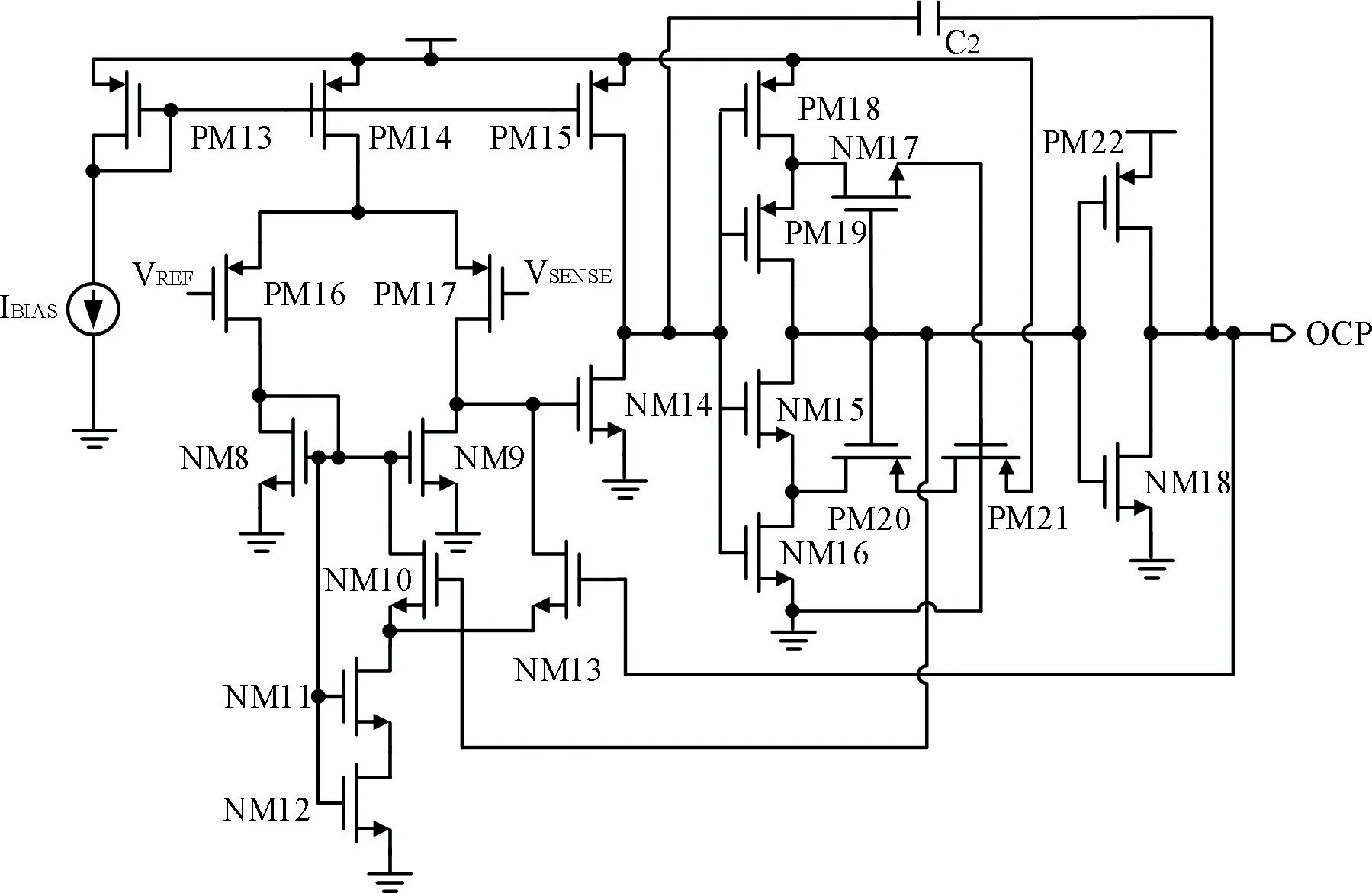

由式(21)可得,调节R11与R13电阻比例关系,可以实现电源轨范围内任意放大倍数,本文中R11、R13为匹配电阻,设定的R11与R13比例关系为0.5 ∶6,即预放大倍数为12 倍。 2.3 比较器电路为了判断芯片是否工作在过流情况下,本文借助比较器电路,对参考电压电路提供的可调节参考电压与采样预放大电路得到的采样电压进行比较,比较器具体电路设计如图7 所示。NM8~NM14,PM16~PM17 构成比较器电路,考虑到比较器两端输入电压较低,且为了减小噪声对精度的影响[15],本文比较器输入对管采用PMOS 管;PM13~PM15 为偏置电路,为比较器的正常工作提供偏置电流;NM15~NM17 及PM18~PM21 为施密特电路,对比较器输出信号进行整形;电容C2构成高频快速通路,提高响应速度。当流经功率管的电流大于设定电流指标时,VSENSE大于VREF,NM9 电流大于PM17 电流,此时NM14 栅极电压接近地电位,NM14 截止,施密特电路输入端信号为高电平,进而反相器输出高电平,代表此时发生过流。当流经功率管的电流小于设定电流指标时,NM14导通,反相器输出低电平。对于低频信号,施密特电路→反向器电路→(NM10/NM13)→NM14→施密特电路构成低频正反馈环路;对于高频信号,C2→NM13→NM14→C2构成高频正反馈环路。正反馈环路的存在提供了一定的迟滞范围,提高了电路的稳定性。

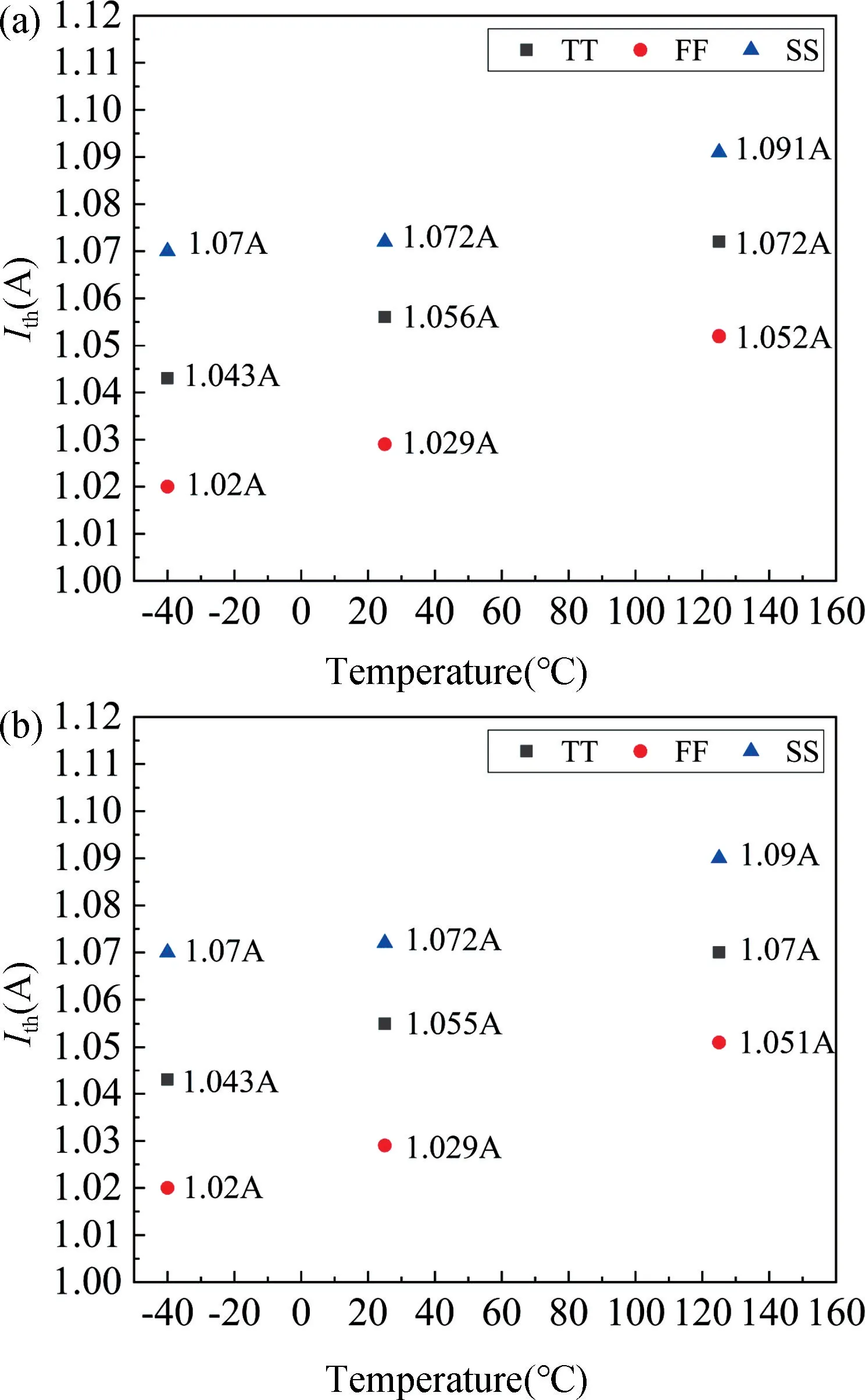

图7 比较器电路Fig.7 Comparator circuit 将参考电压表达式(12)与采样电压表达式(20)联立可得过流阈值设定表达式:

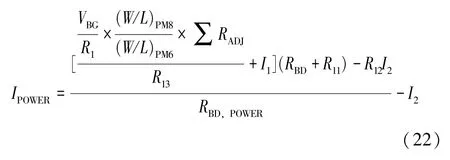

由式(22)可知,过流阈值设定可通过调节电阻网络RADJ来实现,具有良好的线性关系,同时提高了实际应用过程中的灵活性。 3 仿真验证本文采用0.18 μm BCD 工艺,借助Cadence Spice仿真工具,电路工作电压为5 V,对电路进行仿真验证。过流保护电路过流阈值预期设计目标在典型情况下为1 A。仿真结果包括参考电压电路运算放大器环路增益及相位裕度、功率管电流与采样电压关系、整体电路过流阈值随温度及工艺变化前仿真及版图后仿真。 图8 为参考电压电路运算放大器环路增益及相位裕度仿真图。由仿真结果可知,低频环路增益为69.818 dB,补偿后的相位裕度为80.674°,能够提供较好的环路增益及相位裕度,具有良好的精度和频率稳定性,满足电路设计要求。

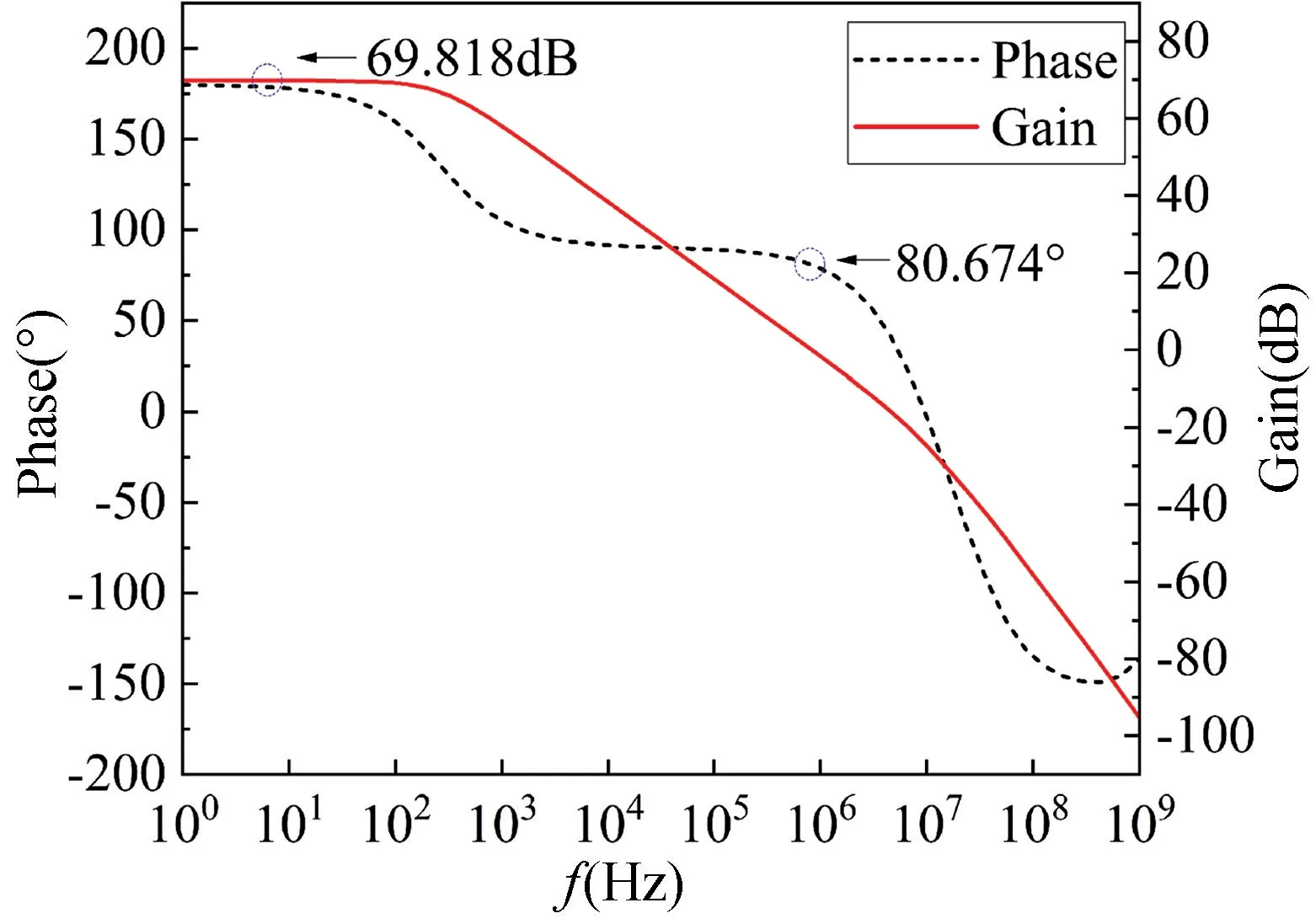

图8 参考电压电路运算放大器环路增益及相位裕度Fig.8 Reference voltage circuit operational amplifier loop gain and phase margin 图9 为功率管电流与采样电压关系图。由仿真结果可知,流经功率管电流范围在0.5~3 A,采样精度均为99.97%,流经功率管电流与采样电压具有良好的线性度,且能够实现较大电流范围的高精度检测及预放大。

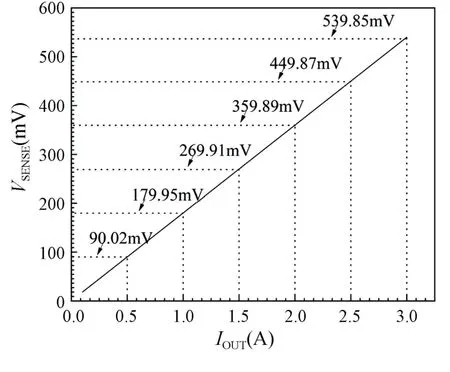

图9 IPOWERMOS与VSENSE关系图Fig.9 IPOWERMOS vs VSENSE diagram 图10 为整体电路过流阈值随温度及工艺变化前仿真及版图后仿真。后仿真结果表明,过流阈值在TT工艺、27 ℃典型情况下为1.055 A,精度为5.5%;FF工艺、-40 ℃情况下,精度最高可达到2%;最大电流误差在9%以内。

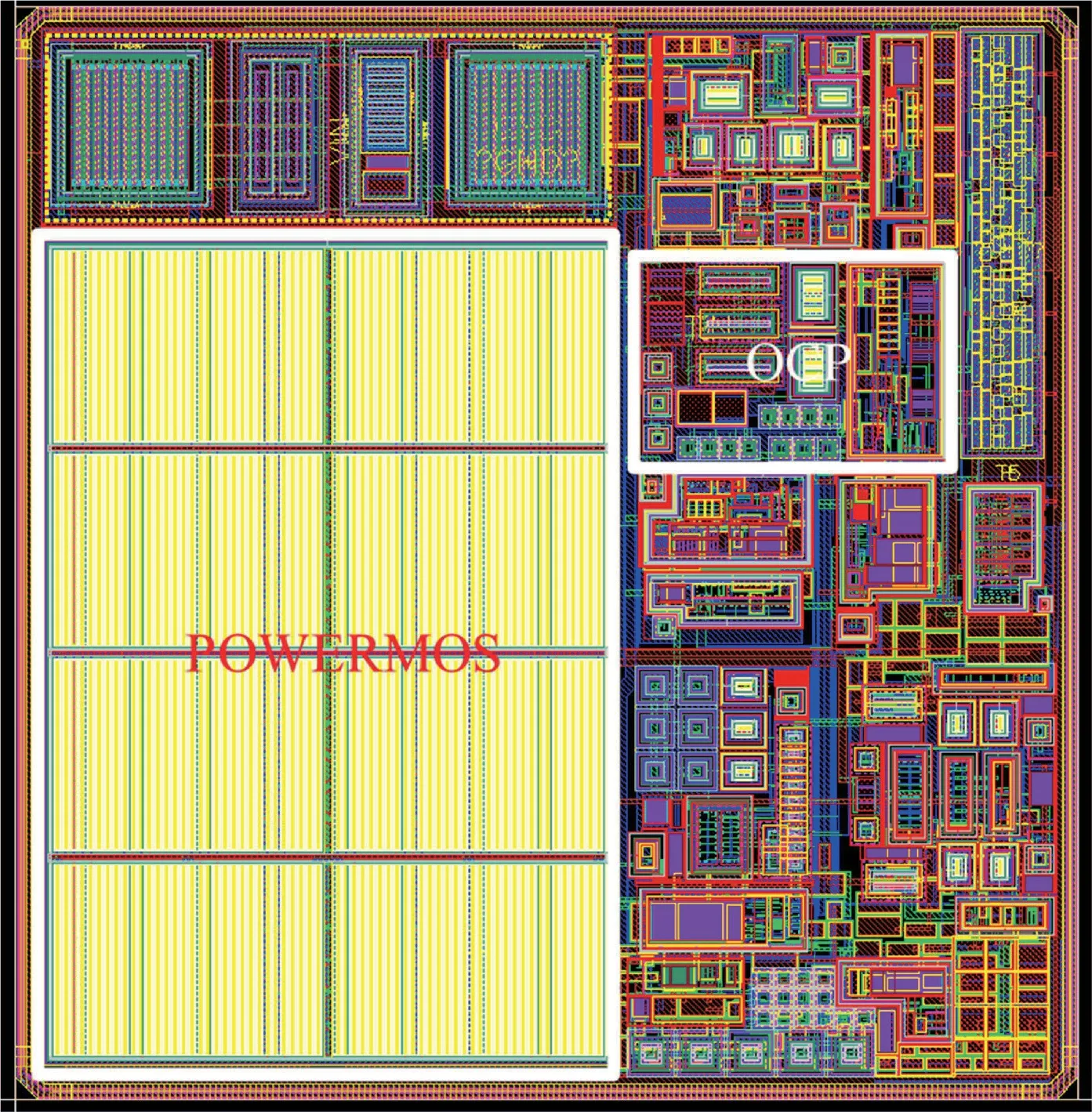

图10 过流阈值随温度及工艺变化仿真。(a)前仿真;(b)版图后仿真Fig.10 Simulation of over-current threshold varying with temperature and process.(a) Pre-simulation;(b) Post-layout simulation 图11 为应用本文提出的过流保护电路芯片版图,整个芯片面积为770 μm×740 μm,其中过流保护电路所占面积为93 μm×21 μm,占总芯片面积的0.34%;在版图设计中充分考虑了器件的对称匹配以及高压隔离结构设计;同时,为避免额外的电流波动对电路采样精度的影响,对RBD所处PAD 不引入电源线为其他模块供电。

图11 芯片版图Fig.11 Chip layout 将本文提出的过流保护电路与其他文献对比,相较于文献[8]采用功率管导通电阻采样结构,本文提出的键合丝采样方式克服了工艺制造所引起的非线性失配误差;本文过流阈值精度可达5.5%,优于文献[9]的10%精度。 4 结论本文基于0.18 μm BCD 工艺提出了一种应用于锂电池保护芯片的高精度过流保护电路,电流采样方式直接由键合丝实现,相较于传统结构避免了额外导通电阻及功耗的引入,其等效电阻阻值量级为mΩ,即使在负载电流达到1 A 的情况下,相较于典型5 W 功率输出,其能效损失仅为15 mW,占总体能效的0.3%;电路结构简洁、采样精度高、过流阈值设置灵活,高压管的引入拓宽了实际应用领域。通过仿真结果可知,电路设计符合预期目标要求。 猜你喜欢 过流导通环路 多输出反激式开关电源同步整流技术电子科技(2022年10期)2022-10-15隧洞明满流边界下滇中引水工程闸门过流特性农业工程学报(2022年7期)2022-07-09通过交换机检测解决网络环路的探索无线互联科技(2022年4期)2022-05-11高密度城市核心区地下环路功能及出入口设置研究城市道桥与防洪(2022年1期)2022-02-25外差式光锁相环延时对环路性能影响河北工业大学学报(2021年4期)2021-09-23基于SoC 的导航接收机闭环跟踪环路设计与实现全球定位系统(2021年3期)2021-08-07某型号产品电性能测试数据漏项问题分析科学与财富(2020年24期)2020-10-27串联晶闸管同步导通设计研究速读·下旬(2019年3期)2019-04-11浅谈电缆网电性能检查常见故障分析及预防科学与财富(2017年27期)2017-10-17TGA9型变流器电流反馈信号异常报模块故障分析科学与财富(2016年34期)2017-03-23

|

【本文地址】

电子元件与材料2022年4期

电子元件与材料2022年4期