|

14、ADS使用记录之功率放大器设计

基于ADS2022

参考的书籍是卢益锋老师的ADS射频电路设计与仿真学习笔记

前置教程: 01、ADS使用记录之新建工程 02、ADS使用记录之导入各类仿真模型导入 03、ADS使用记录之DC仿真控制器的使用 04、ADS使用记录之S仿真控制器的使用&椭圆低通滤波器设计 05、ADS使用记录之集总参数匹配 06、ADS使用记录之分布式参数匹配 07、ADS使用记录之匹配Q值-宽带与窄带 08、ADS使用记录之低通滤波器设计与优化 09、ADS使用记录之滤波器自动设计 10、ADS使用记录之设计高低阻抗滤波器(含版图仿真) 11、ADS使用记录之LNA设计 12、ADS使用记录之功分器设计 13、ADS使用记录之功率合成的失配仿真

此次设计采用MW6S004N晶体管。

-1、源文件下载

ADS功率放大器设计源文件

0、设计指标

中心频率1850Mhz 功率增益大于16db 效率PAE大于50% 输出功率大于4w

1、数据手册研读

参考:番外1:射频功放晶体管的重要参数

2、导入器件与直流扫描

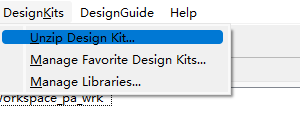

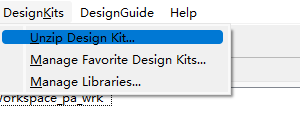

点击菜单栏的DesignKits,选择解压:  在弹出窗口选中飞思卡尔的ADS库文件,点击解压: 在弹出窗口选中飞思卡尔的ADS库文件,点击解压:  随后选择解压位置,一段时间后解压完成。 新建原理图,命名为Dc_test: 随后选择解压位置,一段时间后解压完成。 新建原理图,命名为Dc_test:  在工具栏选择插入,插入模板: 在工具栏选择插入,插入模板:  选择FET_curve_tracer: 选择FET_curve_tracer:  打开后在原理图中插入此次使用的器件和include: 打开后在原理图中插入此次使用的器件和include:   对器件进行连线: 对器件进行连线:  修改VGS扫描范围时2-4V,VDS的扫描范围时0-50V。(选择此数值的原因是数据手册中VGS导通电压约为2V,VDS的击穿电压为68V,取50V与之相近) 修改VGS扫描范围时2-4V,VDS的扫描范围时0-50V。(选择此数值的原因是数据手册中VGS导通电压约为2V,VDS的击穿电压为68V,取50V与之相近)

点击仿真得到结果,可见在Vds=28V时漏极电流为58mA,此时Vgs为2.8V,较为符合设计要求:  由数据手册得到此时输出1W时的功率增益约为18.5db: 由数据手册得到此时输出1W时的功率增益约为18.5db:

3、稳定性测试

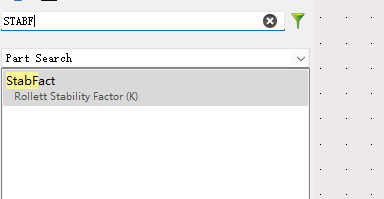

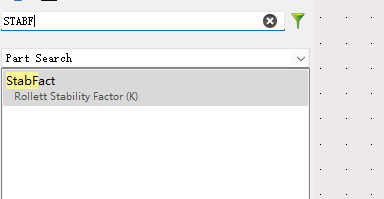

新建原理图,命名为stab_test:  添加晶体管器件和相应的include: 添加晶体管器件和相应的include:  添加相应的外围器件和仿真S扫描控件,修改合理的扫描范围(不知道控件在哪儿的参考11、ADS使用记录之LNA设计中的稳定性分析): 添加相应的外围器件和仿真S扫描控件,修改合理的扫描范围(不知道控件在哪儿的参考11、ADS使用记录之LNA设计中的稳定性分析):  添加StabFact控件: 添加StabFact控件:   点击仿真查看数据,可以看到晶体管在200M-2000M范围内保持绝对稳定,稳定性较好: 点击仿真查看数据,可以看到晶体管在200M-2000M范围内保持绝对稳定,稳定性较好:

4、提高稳定性的方法

在此简单介绍一些常用的提高稳定性的方法。 第一种方法是在栅极串接电阻吗,如下所示:

修改后在此进行仿真,得到结果对比图(红色为修改之后的),由此系统更加稳定了:  第二种方法是在栅极电阻电容反馈到地: 第二种方法是在栅极电阻电容反馈到地:  得到结果如下所示,其中红色为修改后的结果,显而易见修改之后系统低频稳定性显著提升: 得到结果如下所示,其中红色为修改后的结果,显而易见修改之后系统低频稳定性显著提升:

5、负载牵引LoadPull

负载牵引的主要目的是找出输入输出的阻抗,以便于之后进行匹配,新建原理图,在designguide中找到放大器选项:  选择如下的负载牵引选项(第二个LoadPull会计算功率压缩从而耗费大量时间,除非特别需要否则不建议使用第二个): 选择如下的负载牵引选项(第二个LoadPull会计算功率压缩从而耗费大量时间,除非特别需要否则不建议使用第二个):  点击确定打开,打开后如下所示: 点击确定打开,打开后如下所示:  修改图中原有的晶体管,换成本次设计实际使用的: 修改图中原有的晶体管,换成本次设计实际使用的:  下面对一些数值进行设置,包括漏极电压和栅极电压和频率与功率等等,由于之前的分析,漏极电压应该为28V,而理想的栅极电压应该为2.8V: 下面对一些数值进行设置,包括漏极电压和栅极电压和频率与功率等等,由于之前的分析,漏极电压应该为28V,而理想的栅极电压应该为2.8V:  设置特性阻抗为10,其他保持默认: 设置特性阻抗为10,其他保持默认:  设置特性阻抗为10的原因是数据手册中给出的圆图的特性阻抗就是10,保持一致有助于之后的设计: 设置特性阻抗为10的原因是数据手册中给出的圆图的特性阻抗就是10,保持一致有助于之后的设计:  点击仿真得到结果,负载牵引的主要目的是找出合适的负载阻抗,可以看到图中有红色和蓝色两个圆圈,其中红色为效率圆图,蓝色为功率圆图。在效率圆图的圆心选取负载阻抗 Z0(0.567+j0.827)* 可以获得最高的效率,在功率圆图中心选取负载阻抗 Z0(0.847+j0.749),也就是8.47+j7.49欧姆* 可以获得最佳的输出功率,此处使用最佳输出功率时的阻抗(在设计高效功放时往往需要负载牵引和源牵引需要交替反复进行,此处简化就不进行这样的步骤了): 点击仿真得到结果,负载牵引的主要目的是找出合适的负载阻抗,可以看到图中有红色和蓝色两个圆圈,其中红色为效率圆图,蓝色为功率圆图。在效率圆图的圆心选取负载阻抗 Z0(0.567+j0.827)* 可以获得最高的效率,在功率圆图中心选取负载阻抗 Z0(0.847+j0.749),也就是8.47+j7.49欧姆* 可以获得最佳的输出功率,此处使用最佳输出功率时的阻抗(在设计高效功放时往往需要负载牵引和源牵引需要交替反复进行,此处简化就不进行这样的步骤了):

6、源牵引

在完成负载牵引后,可以先进行输出匹配,在输出匹配完成后将输出匹配电路和原电路一起带入进行源牵。但是在晶体管隔离特性较好的情况下,也可以先进行源牵引再进行输出匹配。同样找到designguide,打开放大器选项找到Source Pull选项:  更换晶体管为此次设计所使用的(不要忘记添加include): 更换晶体管为此次设计所使用的(不要忘记添加include):  修改变量值和负载牵引时一致,不要忘记设置特性阻抗为10: 修改变量值和负载牵引时一致,不要忘记设置特性阻抗为10:   修改完成后进行仿真,可得此时最佳输出功率时的源阻抗为2.1-j5.39欧姆(m2处): 修改完成后进行仿真,可得此时最佳输出功率时的源阻抗为2.1-j5.39欧姆(m2处):

7、负载阻抗匹配

由负载牵引得出的负载阻抗(功率最佳)为8.47+j7.49,创建原理图命名为Load_Match,插入相关元器件(不知道器件哪里找可以参考 05、ADS使用记录之集总参数匹配 06、ADS使用记录之分布式参数匹配11、ADS使用记录之LNA设计):  设置Smith匹配参数如下所示: 设置Smith匹配参数如下所示:  打开Smith圆图匹配界面,手动进行匹配: 打开Smith圆图匹配界面,手动进行匹配:  各个元件数值如下所示: 各个元件数值如下所示:     点击生成电路,得到匹配原理图: 点击生成电路,得到匹配原理图:  进行仿真,发现匹配效果较好: 进行仿真,发现匹配效果较好:  此时使用的是理想微带线,将其换位实际的微带线,此处使用板材罗杰斯4350B,参数如下所示: 此时使用的是理想微带线,将其换位实际的微带线,此处使用板材罗杰斯4350B,参数如下所示:

使用LineCalc工具进行计算,不会可以参考 06、ADS使用记录之分布式参数匹配,最终使用实际参数的微带线如下所示:

再次进行仿真,效果略微下降: 再次进行仿真,效果略微下降:

8、源阻抗匹配

源阻抗为2.1-j5.39欧姆,新建原理图,合理设置各种参数:   进入smith匹配界面,加入电容和传输线: 进入smith匹配界面,加入电容和传输线:    点击生成电路,随后进行仿真: 点击生成电路,随后进行仿真:  上述的仿真都是使用的理想微带线,使用微带线计算工具将其转化为实际微带线: 上述的仿真都是使用的理想微带线,使用微带线计算工具将其转化为实际微带线:  再次进行仿真,得到结果: 再次进行仿真,得到结果:

9、偏置电路设计

在一般电路中,偏置电路中往往需要加入电感以抑制交流分量,但是在射频电路中,电感往往具有较大的寄生电容(尤其在高频时)。 在射频电路设计时,往往不能使用电感作为遏制交流的手段。在此次设计中,可以预测到的偏置电路的主要交流分量为1850Mhz,由此可以使用四分之一波长短路线抑制此高频分量。 四分之一波长线具有阻抗变换特性,对于特定频率而言,可以将短路点变换为开路点,由此可以抑制特定频率的波。 计算得出四分之一波长线路的宽约为1mm,长24.15mm。  首先进行输出偏置匹配设计,也就是漏极的匹配,绘制原理图如下所示,其中微带线总长度约为24mm: 首先进行输出偏置匹配设计,也就是漏极的匹配,绘制原理图如下所示,其中微带线总长度约为24mm:  进行仿真,发现在1.85Ghz时阻抗最大,由此该偏置电路可以有效隔离1850Mhz的波,符合设计要求: 进行仿真,发现在1.85Ghz时阻抗最大,由此该偏置电路可以有效隔离1850Mhz的波,符合设计要求:

如果波形不谐振在1.85Ghz,可以使用Tuning来对微带线长度进行调谐。对于带宽不是很大的宽带匹配需要使用高频的频率去计算四分之一波长线。 回到之前的输出匹配界面,插入设计好的偏置电路,再次进行仿真: 如果波形不谐振在1.85Ghz,可以使用Tuning来对微带线长度进行调谐。对于带宽不是很大的宽带匹配需要使用高频的频率去计算四分之一波长线。 回到之前的输出匹配界面,插入设计好的偏置电路,再次进行仿真:  使用tuning微调TL2的长度,使其达到最佳状态(此时TL2长为10.43mm): 使用tuning微调TL2的长度,使其达到最佳状态(此时TL2长为10.43mm):  对该原理图进行修改,给电容添加焊盘,在交界处添加节(将Sminth匹配的图放入主原理图): 对该原理图进行修改,给电容添加焊盘,在交界处添加节(将Sminth匹配的图放入主原理图):  对此原理图进行tuning,根据仿真结果修改参数,发现在如下参数时效果较好: 对此原理图进行tuning,根据仿真结果修改参数,发现在如下参数时效果较好:   随后进行输入匹配,按照同样步骤添加偏置电路: 随后进行输入匹配,按照同样步骤添加偏置电路:  添加微带STEP台阶,减小阻抗突变造成的影响: 添加微带STEP台阶,减小阻抗突变造成的影响:

之间进行仿真,效果如下:  进行tuning,寻找合适的参数: 进行tuning,寻找合适的参数:

最终输入匹配电路图如下所示:

10、小信号仿真

新建原理图,命名为PA_S,将所有的电路图复制进去并连接:  进行tuning,寻找最佳S11: 进行tuning,寻找最佳S11:  此时小信号仿真的S参数如下所示,性能较好: 此时小信号仿真的S参数如下所示,性能较好:

11、谐波平衡仿真

插入port,失效Term和电源:  在此原理图同级别目录新建Symbol,插入相关端口点击保存: 在此原理图同级别目录新建Symbol,插入相关端口点击保存:  点击designguide: 点击designguide:  选择Spectrum…,如下所示: 选择Spectrum…,如下所示:  在打开的模板中插入刚刚生成的symbol: 在打开的模板中插入刚刚生成的symbol:  设置相关参数: 设置相关参数:  设置谐波平衡控件最高分析三次谐波: 设置谐波平衡控件最高分析三次谐波:  进行仿真查看效果: 进行仿真查看效果:

12、版图仿真设置

新建原理图,命名为PCB,将之前S参数仿真时候的原理图复制进去:  删除对地端口和电源、Term,随后点击生成PCB,如下所示: 删除对地端口和电源、Term,随后点击生成PCB,如下所示:  删除所有端口与地线,修改移动相关的部分,使其符合功放芯片的封装图: 删除所有端口与地线,修改移动相关的部分,使其符合功放芯片的封装图:  给所有连线部分添加端口: 给所有连线部分添加端口:  打开EM设置,设置板材为Rogers4350B,其参数如下所示(包括板厚、铜厚、和介质板参数等等): 打开EM设置,设置板材为Rogers4350B,其参数如下所示(包括板厚、铜厚、和介质板参数等等):   设置扫频参数如下所示(一定要添加0HZ的分量): 设置扫频参数如下所示(一定要添加0HZ的分量):

设置输出选项使其输出所有的产生的频率:  设置model参数使其产生EMmodel以便之后的版图联合仿真,设置完成后点击仿真按钮进行仿真: 设置model参数使其产生EMmodel以便之后的版图联合仿真,设置完成后点击仿真按钮进行仿真:  一段时间后弹出窗口,仿真完成: 一段时间后弹出窗口,仿真完成:  在EM设置界面点击symbol图标,在symbol产生界面选择looklike选项并点击ok: 在EM设置界面点击symbol图标,在symbol产生界面选择looklike选项并点击ok:  得到Symbol如下所示: 得到Symbol如下所示:

13、小信号的版图原理图联合仿真

新建原理图,将产生的symbol插入到新的原理图中去,按照原来的方式连线,并添加相关的仿真控件:  点击仿真按钮左侧的choose view for simulation按钮,点击生成的版图symbol,选择为emmodel: 点击仿真按钮左侧的choose view for simulation按钮,点击生成的版图symbol,选择为emmodel:  点击仿真查看结果,由此可以看到系统稳定,小信号仿真时S11约为-16db,小信号增益约为19.8db: 点击仿真查看结果,由此可以看到系统稳定,小信号仿真时S11约为-16db,小信号增益约为19.8db:

14、大信号的版图原理图联合仿真

新建原理图,命名为bigsingle,将之前的图纸复制进去,删除电源和Term,插入port:

按照步骤建立symbol:  将新建立的symbol插入之前大信号仿真的原理图中(11、谐波平衡仿真中的): 将新建立的symbol插入之前大信号仿真的原理图中(11、谐波平衡仿真中的):  重新进行仿真,观察结果对比: 重新进行仿真,观察结果对比:  由此可见版图仿真时PAE最高约为52.6db,与原理图仿真相比略有恶化,但在可接受范围内。 由此可见版图仿真时PAE最高约为52.6db,与原理图仿真相比略有恶化,但在可接受范围内。

|  在弹出窗口选中飞思卡尔的ADS库文件,点击解压:

在弹出窗口选中飞思卡尔的ADS库文件,点击解压:  随后选择解压位置,一段时间后解压完成。 新建原理图,命名为Dc_test:

随后选择解压位置,一段时间后解压完成。 新建原理图,命名为Dc_test:  在工具栏选择插入,插入模板:

在工具栏选择插入,插入模板:  选择FET_curve_tracer:

选择FET_curve_tracer:  打开后在原理图中插入此次使用的器件和include:

打开后在原理图中插入此次使用的器件和include:

对器件进行连线:

对器件进行连线:  修改VGS扫描范围时2-4V,VDS的扫描范围时0-50V。(选择此数值的原因是数据手册中VGS导通电压约为2V,VDS的击穿电压为68V,取50V与之相近)

修改VGS扫描范围时2-4V,VDS的扫描范围时0-50V。(选择此数值的原因是数据手册中VGS导通电压约为2V,VDS的击穿电压为68V,取50V与之相近)

由数据手册得到此时输出1W时的功率增益约为18.5db:

由数据手册得到此时输出1W时的功率增益约为18.5db:

添加晶体管器件和相应的include:

添加晶体管器件和相应的include:  添加相应的外围器件和仿真S扫描控件,修改合理的扫描范围(不知道控件在哪儿的参考11、ADS使用记录之LNA设计中的稳定性分析):

添加相应的外围器件和仿真S扫描控件,修改合理的扫描范围(不知道控件在哪儿的参考11、ADS使用记录之LNA设计中的稳定性分析):  添加StabFact控件:

添加StabFact控件:

点击仿真查看数据,可以看到晶体管在200M-2000M范围内保持绝对稳定,稳定性较好:

点击仿真查看数据,可以看到晶体管在200M-2000M范围内保持绝对稳定,稳定性较好:

第二种方法是在栅极电阻电容反馈到地:

第二种方法是在栅极电阻电容反馈到地:  得到结果如下所示,其中红色为修改后的结果,显而易见修改之后系统低频稳定性显著提升:

得到结果如下所示,其中红色为修改后的结果,显而易见修改之后系统低频稳定性显著提升:

选择如下的负载牵引选项(第二个LoadPull会计算功率压缩从而耗费大量时间,除非特别需要否则不建议使用第二个):

选择如下的负载牵引选项(第二个LoadPull会计算功率压缩从而耗费大量时间,除非特别需要否则不建议使用第二个):  点击确定打开,打开后如下所示:

点击确定打开,打开后如下所示:  修改图中原有的晶体管,换成本次设计实际使用的:

修改图中原有的晶体管,换成本次设计实际使用的:  下面对一些数值进行设置,包括漏极电压和栅极电压和频率与功率等等,由于之前的分析,漏极电压应该为28V,而理想的栅极电压应该为2.8V:

下面对一些数值进行设置,包括漏极电压和栅极电压和频率与功率等等,由于之前的分析,漏极电压应该为28V,而理想的栅极电压应该为2.8V:  设置特性阻抗为10,其他保持默认:

设置特性阻抗为10,其他保持默认:  设置特性阻抗为10的原因是数据手册中给出的圆图的特性阻抗就是10,保持一致有助于之后的设计:

设置特性阻抗为10的原因是数据手册中给出的圆图的特性阻抗就是10,保持一致有助于之后的设计:  点击仿真得到结果,负载牵引的主要目的是找出合适的负载阻抗,可以看到图中有红色和蓝色两个圆圈,其中红色为效率圆图,蓝色为功率圆图。在效率圆图的圆心选取负载阻抗 Z0(0.567+j0.827)* 可以获得最高的效率,在功率圆图中心选取负载阻抗 Z0(0.847+j0.749),也就是8.47+j7.49欧姆* 可以获得最佳的输出功率,此处使用最佳输出功率时的阻抗(在设计高效功放时往往需要负载牵引和源牵引需要交替反复进行,此处简化就不进行这样的步骤了):

点击仿真得到结果,负载牵引的主要目的是找出合适的负载阻抗,可以看到图中有红色和蓝色两个圆圈,其中红色为效率圆图,蓝色为功率圆图。在效率圆图的圆心选取负载阻抗 Z0(0.567+j0.827)* 可以获得最高的效率,在功率圆图中心选取负载阻抗 Z0(0.847+j0.749),也就是8.47+j7.49欧姆* 可以获得最佳的输出功率,此处使用最佳输出功率时的阻抗(在设计高效功放时往往需要负载牵引和源牵引需要交替反复进行,此处简化就不进行这样的步骤了):

更换晶体管为此次设计所使用的(不要忘记添加include):

更换晶体管为此次设计所使用的(不要忘记添加include):  修改变量值和负载牵引时一致,不要忘记设置特性阻抗为10:

修改变量值和负载牵引时一致,不要忘记设置特性阻抗为10:

修改完成后进行仿真,可得此时最佳输出功率时的源阻抗为2.1-j5.39欧姆(m2处):

修改完成后进行仿真,可得此时最佳输出功率时的源阻抗为2.1-j5.39欧姆(m2处):

设置Smith匹配参数如下所示:

设置Smith匹配参数如下所示:  打开Smith圆图匹配界面,手动进行匹配:

打开Smith圆图匹配界面,手动进行匹配:  各个元件数值如下所示:

各个元件数值如下所示:

点击生成电路,得到匹配原理图:

点击生成电路,得到匹配原理图:  进行仿真,发现匹配效果较好:

进行仿真,发现匹配效果较好:  此时使用的是理想微带线,将其换位实际的微带线,此处使用板材罗杰斯4350B,参数如下所示:

此时使用的是理想微带线,将其换位实际的微带线,此处使用板材罗杰斯4350B,参数如下所示:

再次进行仿真,效果略微下降:

再次进行仿真,效果略微下降:

进入smith匹配界面,加入电容和传输线:

进入smith匹配界面,加入电容和传输线:

点击生成电路,随后进行仿真:

点击生成电路,随后进行仿真:  上述的仿真都是使用的理想微带线,使用微带线计算工具将其转化为实际微带线:

上述的仿真都是使用的理想微带线,使用微带线计算工具将其转化为实际微带线:  再次进行仿真,得到结果:

再次进行仿真,得到结果:

首先进行输出偏置匹配设计,也就是漏极的匹配,绘制原理图如下所示,其中微带线总长度约为24mm:

首先进行输出偏置匹配设计,也就是漏极的匹配,绘制原理图如下所示,其中微带线总长度约为24mm:  进行仿真,发现在1.85Ghz时阻抗最大,由此该偏置电路可以有效隔离1850Mhz的波,符合设计要求:

进行仿真,发现在1.85Ghz时阻抗最大,由此该偏置电路可以有效隔离1850Mhz的波,符合设计要求: 如果波形不谐振在1.85Ghz,可以使用Tuning来对微带线长度进行调谐。对于带宽不是很大的宽带匹配需要使用高频的频率去计算四分之一波长线。 回到之前的输出匹配界面,插入设计好的偏置电路,再次进行仿真:

如果波形不谐振在1.85Ghz,可以使用Tuning来对微带线长度进行调谐。对于带宽不是很大的宽带匹配需要使用高频的频率去计算四分之一波长线。 回到之前的输出匹配界面,插入设计好的偏置电路,再次进行仿真:  使用tuning微调TL2的长度,使其达到最佳状态(此时TL2长为10.43mm):

使用tuning微调TL2的长度,使其达到最佳状态(此时TL2长为10.43mm):  对该原理图进行修改,给电容添加焊盘,在交界处添加节(将Sminth匹配的图放入主原理图):

对该原理图进行修改,给电容添加焊盘,在交界处添加节(将Sminth匹配的图放入主原理图):  对此原理图进行tuning,根据仿真结果修改参数,发现在如下参数时效果较好:

对此原理图进行tuning,根据仿真结果修改参数,发现在如下参数时效果较好:

随后进行输入匹配,按照同样步骤添加偏置电路:

随后进行输入匹配,按照同样步骤添加偏置电路:  添加微带STEP台阶,减小阻抗突变造成的影响:

添加微带STEP台阶,减小阻抗突变造成的影响:

进行tuning,寻找合适的参数:

进行tuning,寻找合适的参数:

进行tuning,寻找最佳S11:

进行tuning,寻找最佳S11:  此时小信号仿真的S参数如下所示,性能较好:

此时小信号仿真的S参数如下所示,性能较好:

在此原理图同级别目录新建Symbol,插入相关端口点击保存:

在此原理图同级别目录新建Symbol,插入相关端口点击保存:  点击designguide:

点击designguide:  选择Spectrum…,如下所示:

选择Spectrum…,如下所示:  在打开的模板中插入刚刚生成的symbol:

在打开的模板中插入刚刚生成的symbol:  设置相关参数:

设置相关参数:  设置谐波平衡控件最高分析三次谐波:

设置谐波平衡控件最高分析三次谐波:  进行仿真查看效果:

进行仿真查看效果:

删除对地端口和电源、Term,随后点击生成PCB,如下所示:

删除对地端口和电源、Term,随后点击生成PCB,如下所示:  删除所有端口与地线,修改移动相关的部分,使其符合功放芯片的封装图:

删除所有端口与地线,修改移动相关的部分,使其符合功放芯片的封装图:  给所有连线部分添加端口:

给所有连线部分添加端口:  打开EM设置,设置板材为Rogers4350B,其参数如下所示(包括板厚、铜厚、和介质板参数等等):

打开EM设置,设置板材为Rogers4350B,其参数如下所示(包括板厚、铜厚、和介质板参数等等):

设置扫频参数如下所示(一定要添加0HZ的分量):

设置扫频参数如下所示(一定要添加0HZ的分量):

设置model参数使其产生EMmodel以便之后的版图联合仿真,设置完成后点击仿真按钮进行仿真:

设置model参数使其产生EMmodel以便之后的版图联合仿真,设置完成后点击仿真按钮进行仿真:  一段时间后弹出窗口,仿真完成:

一段时间后弹出窗口,仿真完成:  在EM设置界面点击symbol图标,在symbol产生界面选择looklike选项并点击ok:

在EM设置界面点击symbol图标,在symbol产生界面选择looklike选项并点击ok:  得到Symbol如下所示:

得到Symbol如下所示:

点击仿真按钮左侧的choose view for simulation按钮,点击生成的版图symbol,选择为emmodel:

点击仿真按钮左侧的choose view for simulation按钮,点击生成的版图symbol,选择为emmodel:  点击仿真查看结果,由此可以看到系统稳定,小信号仿真时S11约为-16db,小信号增益约为19.8db:

点击仿真查看结果,由此可以看到系统稳定,小信号仿真时S11约为-16db,小信号增益约为19.8db:

将新建立的symbol插入之前大信号仿真的原理图中(11、谐波平衡仿真中的):

将新建立的symbol插入之前大信号仿真的原理图中(11、谐波平衡仿真中的):  重新进行仿真,观察结果对比:

重新进行仿真,观察结果对比:  由此可见版图仿真时PAE最高约为52.6db,与原理图仿真相比略有恶化,但在可接受范围内。

由此可见版图仿真时PAE最高约为52.6db,与原理图仿真相比略有恶化,但在可接受范围内。