秒表设计(Verilog) |

您所在的位置:网站首页 › 秒表的使用方法 › 秒表设计(Verilog) |

秒表设计(Verilog)

|

秒表设计(Verilog)–quartus13

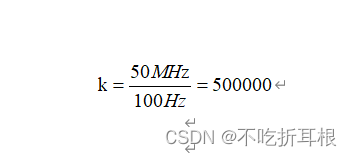

本次实验的目的在于: (1) 掌握利用硬件描述语言设计计数器、分频电路、译码电路的方法; (2) 掌握利用例化语句设计顶层电路的方法。 实验内容 秒表设计:要求: (1)数码管显示; (2)能清零、暂停; (3)精确到1/100秒。 实验设备 (1)DE2-115实验板一块 (2)高配置计算机一台 实验原理电路框图 1、分频电路设计、编译; 设计方案:该模块有三个端口,分别是原始时钟输入端口、时钟清零信号输入端口、分频时钟输出端口。设置时钟清零信号为高电平时时钟清零,即输出的时钟为低电平。由于开发板提供的时钟信号频率为50MHz,而我们需要的为100Hz的时钟输入,所以分频系数k为: |

【本文地址】

今日新闻 |

推荐新闻 |

设置一个计数器,当计数器计数小于k-1时,计数器加1,时钟输出为0;当计数器计数到k-1的时,计数器清零,时钟输出为1。

设置一个计数器,当计数器计数小于k-1时,计数器加1,时钟输出为0;当计数器计数到k-1的时,计数器清零,时钟输出为1。