|

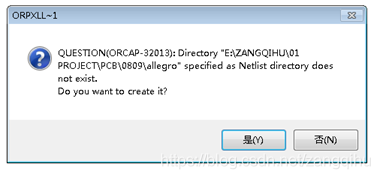

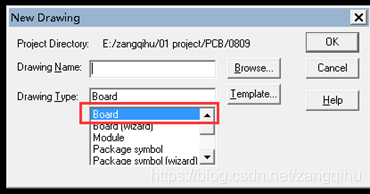

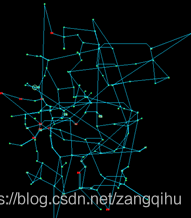

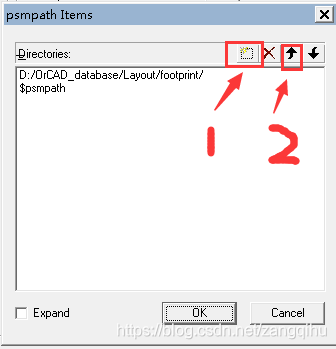

一、原理图部分 1、 首先打开画好的原理图,打开后如下   2、 进行生成网表 选择项目,点击Tools >>>Create Netlist 按照下图方式进行选择,然后点击确认 2、 进行生成网表 选择项目,点击Tools >>>Create Netlist 按照下图方式进行选择,然后点击确认  再次点击 是 再次点击 是 3、 这时候根目录下面会生成两个文件夹,如下图,后面导入PCB会用到。 3、 这时候根目录下面会生成两个文件夹,如下图,后面导入PCB会用到。  二、PCB部分 1、打开allegro工具 二、PCB部分 1、打开allegro工具  2、 新建一个PCB(如果有老的PCB直接打开也是可以的) 2、 新建一个PCB(如果有老的PCB直接打开也是可以的)  3、导入原理图File >>>Import>>>Logic,如下图的地方的打勾 3、导入原理图File >>>Import>>>Logic,如下图的地方的打勾  4、点击红色箭头的地方,通过路径找到,原理图部分3生成的allegro文件夹,需要选择allegro这个文件夹后,然后确认。 4、点击红色箭头的地方,通过路径找到,原理图部分3生成的allegro文件夹,需要选择allegro这个文件夹后,然后确认。  5、点击Import Cadence 5、点击Import Cadence  6、完成后点击 Place>>>Manully…,选中后就可以放置器件了 6、完成后点击 Place>>>Manully…,选中后就可以放置器件了   三、如果按照上述方式还是无法导入,请检查PCB库设置是否有问题,PCB库设置如下 1、PCB库设置 打开Setup>>>User preferences 三、如果按照上述方式还是无法导入,请检查PCB库设置是否有问题,PCB库设置如下 1、PCB库设置 打开Setup>>>User preferences  2、 点击打开Paths>>>Library的子文件夹,打开padpth、psmpth选项对应的Value栏 2、 点击打开Paths>>>Library的子文件夹,打开padpth、psmpth选项对应的Value栏  3、padpath点开后1)新增库路径,2)将新增的库置顶 3、padpath点开后1)新增库路径,2)将新增的库置顶  4、psmpath点开后1)新增库路径,2)将新增的库置顶 4、psmpath点开后1)新增库路径,2)将新增的库置顶

|