基于FPGA的多路SPI接口并行数据采集系统 |

您所在的位置:网站首页 › 电脑网络连接配置无法修复 › 基于FPGA的多路SPI接口并行数据采集系统 |

基于FPGA的多路SPI接口并行数据采集系统

|

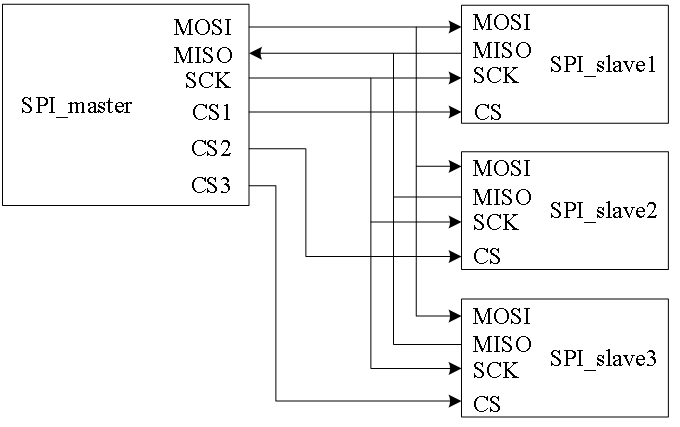

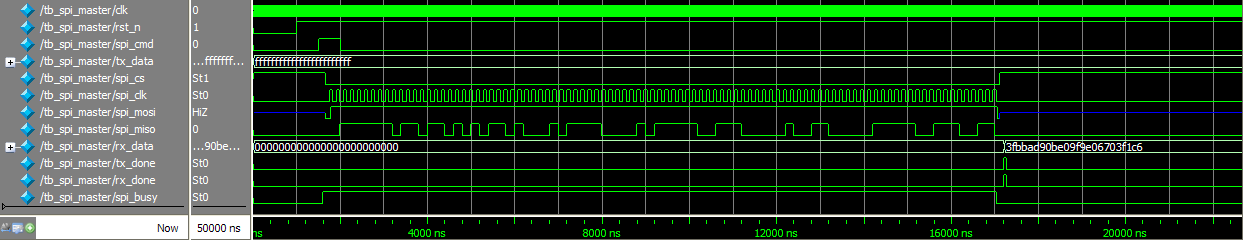

0 引言 随着数字技术发展与应用,越来越多的芯片被用于数据采集与数字交换。在这些芯片中,SPI (Serial Peripheral Interface)作为电路接口应用非常普遍,因而也成为了很多单片机的标准配置。然而很多单片机的SPI接口硬件资源非常有限,在需要同时使用较大数目SPI接口的数据采集系统中,只能对SPI接口扩展并分时复用,这样势必造成数据采集速度下降。FPGA具有高度并行的特点[1],笔者根据实际应用,设计了基于FPGA的多路SPI接口并行系统,应用于需多个SPI接口同步运行的数据采集系统中。 1 SPI总线接口 SPI(串行外围设备接口)是Motorola公司推出的一种同步串行接口,具有传送速率高、连接线少等特点,常用于MCU与外设数据交换[2]。SPI只需要4条线就能完成主、从与外围器件全双工同步通信,这4条线分别为:串行时钟线(SCK)、主机输出从机输入线(MOSI)、主机输入从机输出线(MISO)、从机选择线(CS)。 SPI系统分为主机和从机两类,其中主机提供SPI时钟信号和片选信号,作为从机的输入;从机是接收SPI信号的任何集成电路,包括简单的TTL移位寄存器或其他MCU等。时钟极性(CPOL)和时钟相位(CPHA)的配合完成一次数据传输。其中,CPOL表示时钟在空闲状态的电平,CPHA决定数据在时钟的上升沿传送还是下降沿传送。CPOL与CPHA的不同,可以使SPI总线工作在4种模式下。 (1) CPOL=0,CPHA=0:SCK的空闲电平为低电平,数据在SCK的第一个跳变沿被采集; (2) CPOL=0,CPHA=1:SCK的空闲电平为低电平,数据在SCK的第二个跳变沿被采集; (3) CPOL=1,CPHA=0:SCK的空闲电平为高电平,数据在SCK的第一个跳变沿被采集; (4) CPOL=1,CPHA=1:SCK的空闲电平为高电平,数据在SCK的第二个跳变沿被采集。 当SPI工作时,发送和接收操作都受控于SPI主机的时钟信号(SCK)和片选信号(CS),从而保证通信同步。通常情况下,使用一个主机控制多个从机,典型的系统连接如图1。  图1 SPI总线系统连接方式 图1 SPI总线系统连接方式2 主机端SPI接口模块设计 在笔者设计的数据采集系统中,使用了芯片级传感器——磁性旋转编码器AS5048A[3],用来测量关节点位置,该芯片具备标准SPI输出。在本数据采集系统中需要同时用到10个SPI接口,设计采用FPGA为主机模式,AS5048A为从机模式。 本数据采集系统,在控制命令作用下通过10个SPI接口完成对10组AS5048A测量值读取并保存。因此,为实现数据采集目标需要使用硬件描述语言建立SPI总线接口模块,并设计主状态机控制系统运行状态。整个系统在FPGA上实现。 通过对SPI接口建立电路模型,最终生成一个如图2所示的模块。模块的各引脚定义如下:clk为外部输入时钟信号,由FPGA提供;rst_n为复位信号,当其为低电平时,系统恢复初始状态;spi_cmd为SPI接口数据发送控制信号;tx_data为待发送数据;spi_clk、spi_cs、spi_mosi和spi_miso分别为串行时钟信号、片选信号、主机输出从机输入和主机输入从机输出信号;rx_data为spi_miso信号经串并转换得到接收到的数据;tx_done与rx_done分别为数据发送完成与数据接收完成指示信号。  图2 SPI接口封装图 图2 SPI接口封装图FPGA主状态机控制整个数据采集的运行状态。当主状态机发出读取控制信号,同时将AS5048A读取指令存入寄存器tx_data。FPGA作为主机为从机提供时钟信号和片选信号。当从机AS5048A被选中,并有时钟信号到来时,开始接收读取指令。在下一次接收读取指令的同时,AS5048A在串行时钟信号的下降沿把测量数据按位依次存入SPI接口模块缓冲器,直到时钟停止,等待下一次读取命令到来。接收完成以后将串并转换后的测量值存入寄存器rx_data。 3 SPI接口与并行数据采集的Verilog实现与验证 Verilog HDL是一种用于数字电子系统设计的硬件描述语言,以文本的形式描述数字系统硬件结构和行为。在FPGA开发中,设计者常用它来进行逻辑设计,完成数字逻辑系统的仿真验证、时序分析和逻辑综合。 本文中的设计包括SPI接口电路建模和主状态机,程序均采用Verilog HDL编写,在Mentor公司的HDL语言仿真软件ModelSim中成功编译,运行可以得到仿真波形进行时序分析。SPI接口电路仿真时序如图3所示,10个SPI接口在主状态机控制下并行数据采集时序如图4所示。  图3 FPGA主机模式下SPI接口电路时序 图3 FPGA主机模式下SPI接口电路时序从图3可以看出SPI时钟信号spi_clk空闲电平为低电平,接收数据在其下降沿,上升沿发送数据,与设计一致。读取AS5048A测量值的控制信号spi_cmd上升沿到来后SPI接口开始发送读取指令,片选信号使能。在SPI时钟第一个周期上升沿,主机通过spi_mosi发送最高位至从机,移位寄存器tx_data左移一位;在第一个周期下降沿,主机通过spi_miso接收从机发送的数据最高位,移位寄存器rx_data左移一位。依次类推,值至96位二进制数发送/接收完成,片选信号恢复至高电平,SPI接口电路回到空闲状态。综合以上分析,SPI接口电路时序功能正确。  图4 主状态机控制10个SPI接口并行数据采集 图4 主状态机控制10个SPI接口并行数据采集从图4可以看出10个SPI接口在主状态机的控制信号下并行运行,完成AS5048A的测量值读取,时序功能正确。 通过Altera公司的FPGA开发软件Quartus II将程序综合成电路网表,下载到FPGA芯片为Cyclone EP1C12Q240C8的开发板上进行验证,10路SPI接口可并行完成数据采集,通信功能与预期目标一致。 4 结语 本文简单介绍了SPI接口,包括SPI协议与SPI输入输出端口,建立了基于Verilog的SPI接口电路模型并仿真,并说明了其发送和接收数据的过程。而且,10个SPI接口在主状态机的控制信号下并行运行,稳定高效,解决了SPI接口资源有限时造成的通信速率下降的问题。随着技术的进步,FPGA速度越来越快,资源越来越丰富,基于FPGA的高速数据采集系统应用会更加广泛。 5 推荐 采用航天器的自主导航技术—惯性导航技术研发生产的地下管线惯性定位仪(管道惯性陀螺仪)是零偏科技具有自主知识产权的地下管道定位设备,其利用组合导航以及基于IMU/里程/运动特征/环境特征的多传感器信息融合和误差在线补偿技术,能够精准可靠地获取城市复杂环境下的地下管线三维信息。全自主知识产权、厘米级测量精度、全口径测量范围40mm-1500mm,地下管线惯性定位仪解决了传统技术存在的受埋深、地质条件、电磁干扰等因素影响造成测试结果不可靠的问题。 |

【本文地址】

今日新闻 |

推荐新闻 |