cmos电路多余输入端能否悬空 |

您所在的位置:网站首页 › 电磁加热驱动电路板 › cmos电路多余输入端能否悬空 |

cmos电路多余输入端能否悬空

|

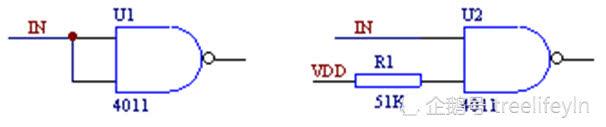

PCB设计过程中必须严格遵守设计规范: (1)当使用CMOS器件时,如果负载驱动能力不够,可将多个器件并联使用。能大大提高CMOS集成电路的输出供给电流与输出吸收电流。如果所驱动的负载电容不大,还可提高速度。 (2)在使用CMOS器件时,不用的输入端不能悬空。如果悬空,作为输入端的引脚会将感应的静电引入电路,造成器件永久损坏。也可能受到外界的干扰而使电路不稳定。处理的办法是:对于CMOS的与非门而言,不使用的引脚可用一个几百kΩ的电阻连接到电源正端VDD;在电源的稳定性较好时也可直接与电源连接;也可以将同一个门电路的输入端连接在一起。

CMOS多余输入端的处理 (3)当连接线较长时,在输入与输出端都会因引线的分布电容与电感给电路带来影响。特别是在CMOS电路中,这种分布电容与电感可能产生振荡,将影响电路的可靠性,并可能使器件永久损坏。所以一般要在输入端串联一个1kΩ左右的电阻来防止可能出现的振荡情况。 4)在使用TTL器件时,由于其电源工作范围较窄,标称值为5V,范围为4.5V~5.5V。使用时需要注意以下事项: l 电源使用标准5V,不能使用负电压,更不能将电源反接。 l 在每个器件的电源与地之间接一个0.1μF的电容,以消除可能的尖脉冲影响。

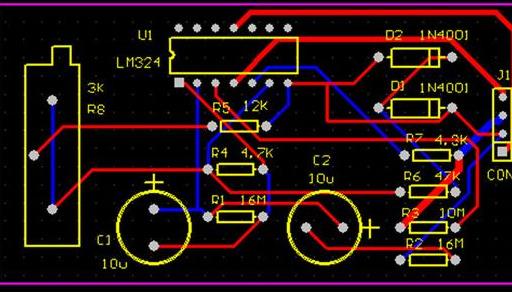

青岛海越 l 对于悬空端的处理,与CMOS的方法基本相同。如果多余的输入端与已经 使用的输入端属于同一个门电路,则多余的输入端应根据逻辑关系分别连 接高电平或低电平,也可以与已使用的输入端连接在一起,如图5-5。如果 悬空可能引起系统不稳定。 l 由于TTL电路中的容性负载能使下一级输入波形边沿变缓,而缓慢变化的 边沿能引起数字电路在状态变换过程中产生幅度较大的振荡,又是一个干 扰源,影响电路的稳定性与可靠性。解决的办法是先使用施密特触发器整 形之后再输出至下一级电路。同样在使用感性负载时,在电流关断的瞬间 会产生较高的电压。这个电压对整个系统非常危险,可使得元器件被击穿 ,也会产生干扰。通常的解决办法是在感性负载上并联一个保护二极管或 电阻电容。 青岛海越机电科技有限公司中频感应电源内部器件电路板PCB根据功能需求设计独特,安全稳定性极高。 |

【本文地址】

今日新闻 |

推荐新闻 |