电源设计中电源输出端到底需要放多少电容? |

您所在的位置:网站首页 › 电容做电源 › 电源设计中电源输出端到底需要放多少电容? |

电源设计中电源输出端到底需要放多少电容?

|

电源设计中电源输出端到底需要放多少电容?

目标阻抗电容与电流的关系实例计算负载角度目标阻抗角度

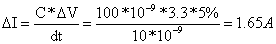

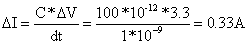

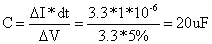

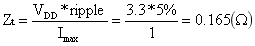

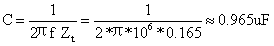

大部分的硬件设计都是存在较大冗余的。其实和软件类似,随着版本的迭代,新人换旧人,你已经不知道这个硬件的最初设计者是怎么想的了。众所周知,硬件有时候理论和实际差的会有点大,这不是说理论存在问题,而是硬件的干扰因素太多了,导致你从理论角度非常难分析,加上硬件成本比较高,一般人也不会去挑战成熟应用,旧的不敢改,新的还得加,导致设计越来越冗余,恶性循环。就好比电源模块输出端到底要放多少电容,可以计算,可以仿真,但是往往做完这些后人家还是会给你补一句,能多放就多放点吧,仿真也不是很准。。。。。 现实归现实,理论分析能力我们还是得有的,不然以后新人问你为啥我们电源得放这么多电容,你就只能来一句,经验来看,这么大电压,这么大电流,就得这么多电容,加可以,反正不能减,瞬间就没了逼格。至少可以来句,因为XXX,所以XXX,综上,还是参考历史经验吧,这就有(hu)理(shuo)有(ba)据(dao)。 。了  ̄□ ̄|| 目标阻抗目标阻抗是PDN分析中一个非常重要的参数。它确定了器件电源端PDN最大阻抗的上限,只要PDN阻抗低于目标阻抗,那么器件的电压噪声肯定能够满足器件要求,如下所示: 一般设计的时候都考虑最恶劣情况,那么我们把上式变一下,不用平均电流了,用最大电流,即在最大电流变化条件下,电压噪声也要满足要求,如下所示: 首先,容值与电流、电压换算关系如下: 如果说目标阻抗是从电源端的角度进行分析的话,把除了负载外的电源与去耦电容看做整体,因为电源电压是不变的,电源与去耦电容的等效电路上的电压变化即代表了负载端电压的变化;而电容与电流的关系则是从负载的角度来分析。 负载角度假定电源电压3.3V,电压抖动要求±5%,电源响应时间要求1ns,负载容值为100pF,则负载需要的瞬态电流为: 同样假定电源电压3.3V,电压抖动要求±5%,最大瞬态电流为1A,目标阻抗为: 假定电源芯片能达到1us的响应时间,即1MHz,也就是在1MHz的频率之下的瞬态电流,电源都能很好的做出反应,但是高于1MHz的频率响应电源可能就搞不定了,这个时候就需要电容来进行补偿,如果该频率在谐振点以下,则陶瓷电容工作在容性条件下,由于ESR和ESL都比较小,所以电容最大值可以近似如下计算: 而实际上这种分析方法只考虑到了在不同频率下电压抖动不超标,而忽略了电容是否能在这个时间内提供足够的能量并且保证电压值不会降低超过VDD的5%。所以该方法依旧存在较大的误差,不过总体来讲分清楚瞬态以及持续时间是非常便于理解这个过程的。 |

【本文地址】

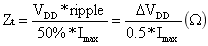

该式中是假定开关电路中流出的平均电流为最大值的50%,VDD为电源电压,Imax为最大电流。

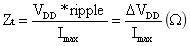

该式中是假定开关电路中流出的平均电流为最大值的50%,VDD为电源电压,Imax为最大电流。 假定电源电压为3.3V,一般器件电压精度要求(±5%),电流最大1A,则最恶劣条件下目标阻抗计算为:

假定电源电压为3.3V,一般器件电压精度要求(±5%),电流最大1A,则最恶劣条件下目标阻抗计算为:

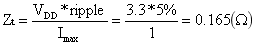

在电源电路中,电容作为储能电容,需要在电源电路动态变化时补偿能量。提供假定电源电路上有个100nF电容,电源电压为3.3V,电压波动范围±5%,电源响应时间要求是10ns,则为了在10ns内,保持VDD在±5%的范围内,该电容所能提供的电流大小为:

在电源电路中,电容作为储能电容,需要在电源电路动态变化时补偿能量。提供假定电源电路上有个100nF电容,电源电压为3.3V,电压波动范围±5%,电源响应时间要求是10ns,则为了在10ns内,保持VDD在±5%的范围内,该电容所能提供的电流大小为:  假如一个这样的IO管脚需要0.1A的电流,那么一个100nF的电容在10ns内可以为16个IO管脚提供电流。但是实际上电容还有有效去耦半径,谐振频率等限制,所以实际也不能这么简单等效。

假如一个这样的IO管脚需要0.1A的电流,那么一个100nF的电容在10ns内可以为16个IO管脚提供电流。但是实际上电容还有有效去耦半径,谐振频率等限制,所以实际也不能这么简单等效。 如果有10个这样的负载,那就需要3.3A电流,由于电压抖动要求±5%,如果电源的响应时间为1us,则所需去耦电容容值为:

如果有10个这样的负载,那就需要3.3A电流,由于电压抖动要求±5%,如果电源的响应时间为1us,则所需去耦电容容值为:  不过由于电容随着放电其电压值也会降低,并且随着频率增加,电路上寄生效应也开始变得明显,所以上式其实并不成立,只是用于理解。这里两个式子也用到了不同的时间,一个是1ns,这是负载端动态变化时要求的响应时间;一个是1us,这个是电源端所能达到的响应时间,这之中存在一个时间差,而这个时间差内的能量,就是我们电容需要补足的能量。

不过由于电容随着放电其电压值也会降低,并且随着频率增加,电路上寄生效应也开始变得明显,所以上式其实并不成立,只是用于理解。这里两个式子也用到了不同的时间,一个是1ns,这是负载端动态变化时要求的响应时间;一个是1us,这个是电源端所能达到的响应时间,这之中存在一个时间差,而这个时间差内的能量,就是我们电容需要补足的能量。 我们知道,对于电容来说,随着频率的增加,电容的等效阻抗会减小,在一定频率下会达到最小值,即电容的ESR(该频率为电容的谐振频率),当频率继续增加的时候,电容会呈感性,此时随着频率的继续增加,电容的等效阻抗会增加。因为电容存在该特性,所以电路当中的频率特性是需要特别考虑的。

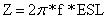

我们知道,对于电容来说,随着频率的增加,电容的等效阻抗会减小,在一定频率下会达到最小值,即电容的ESR(该频率为电容的谐振频率),当频率继续增加的时候,电容会呈感性,此时随着频率的继续增加,电容的等效阻抗会增加。因为电容存在该特性,所以电路当中的频率特性是需要特别考虑的。 如果频率处于谐振点以上,电容呈现感性,此时电容阻抗近似为:

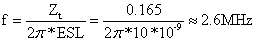

如果频率处于谐振点以上,电容呈现感性,此时电容阻抗近似为:  假定ESL为10nH(有些器件手册里面会写这个),则目标阻抗条件下,该电容能够看护到的最高频率为:

假定ESL为10nH(有些器件手册里面会写这个),则目标阻抗条件下,该电容能够看护到的最高频率为:  想要再保证更高频率的动态响应,就需要其他的电容来保证。从上式也可以看出,f想要足够大,要么ESL得足够小,要么C得足够小。ESL要想小,那得并联电容,同时还得保证电容并联后阻抗小于目标阻抗;如果想减小电容,那会降低低频下的性能。

想要再保证更高频率的动态响应,就需要其他的电容来保证。从上式也可以看出,f想要足够大,要么ESL得足够小,要么C得足够小。ESL要想小,那得并联电容,同时还得保证电容并联后阻抗小于目标阻抗;如果想减小电容,那会降低低频下的性能。