数字电子钟逻辑电路设计 |

您所在的位置:网站首页 › 电子钟维修技巧 › 数字电子钟逻辑电路设计 |

数字电子钟逻辑电路设计

|

课题一 数字电子钟逻辑电路设计

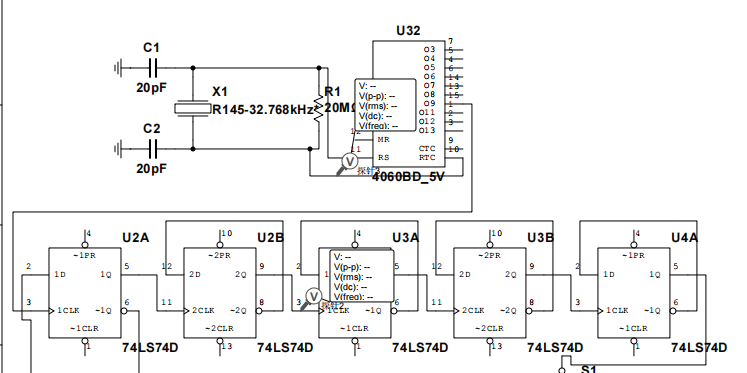

author:AzulaFire 一、简述数字电子钟是一种用数字显示秒、分、时、日的计时装置,与传统的机械钟相比,它具有走时准确,显示直观、无机械传动装置等优点,因而得到了广泛的应用。小到人们日常生活中的电子手表,大到车站、码头、机场等公共场所的大型数显电子钟。 数字电子钟由以下几部分组成:石英晶体振荡器和分频器组成的秒脉冲发生器;校时电路;六十进制秒、分计数器,二十四进制(或十二进制)计时计数器;秒、分、时的译码显示部分等。 二、设计任务和要求用中、小规模集成电路设计一台能显示日、时、分、秒的数字电子钟,要求如下: 由晶振电路产生1Hz标准秒信号。秒、分为00~59六十进制计数器。时为00~23二十四进制计数器。周显示从1~日为七进制计数器。可手动校时:能分别进行秒、分、时、日的校时。只要将开关置于手动位置,可分别对秒、分、时、日进行手动脉冲输入调整或连续脉冲输入的校正。整点报时。整点报时电路要求在每个整点前呜叫五次低音(500Hz),整点时再呜叫一次高音(1000Hz)。 三、总体设计方案方框图及各部分电路设计 时钟脉冲发生电路这部分电路由下面几部分构成: 时钟信号发生器:该部分产生时钟脉冲信号,可以使用555定时器或其他时钟发生器来实现。分频器:该部分将时钟信号分频,以便更好地控制电路的运行速度。可以使用二进制计数器或其他分频器来实现。控制逻辑:该部分根据时钟信号和其他输入信号控制锁存型D触发器的状态。可以使用逻辑门电路或微控制器来实现。锁存型D触发器:该部分用于存储和保持输入信号的状态,以便在下一个时钟脉冲到达时输出。可以使用74LS74D等锁存型D触发器来实现。这部分电路的作用是将为整个系统提供稳定的1hz脉冲时钟信号,当POL输入为低电平,STORE输入也为低电平时,输入到D端的数据会在每个输出端以真值形式出现。当STORE输入电位升高时,输入的数据会在正过度时储存在触发器内部,并以真值形式出现在Q输出端和其互补输出端。CD4012是一个双4输入端与非门,两组正逻辑皆可单独使用。当任一闸之一或一个以上之输入端电位低时,将使输出端电位升高。如果四个输入端皆为高电平,则输出端的电位会降低。在没有任何电平输入时,CD4042的4个输入端经过电阻上拉为高电平,根据其功能表,其四个Q输出端为高电平,Q输出端为低电平,此时LED不显示。此时,与非门CD4012的输出为低电平,使多谐振荡电路停振,从而控制整个电路处于稳定状态

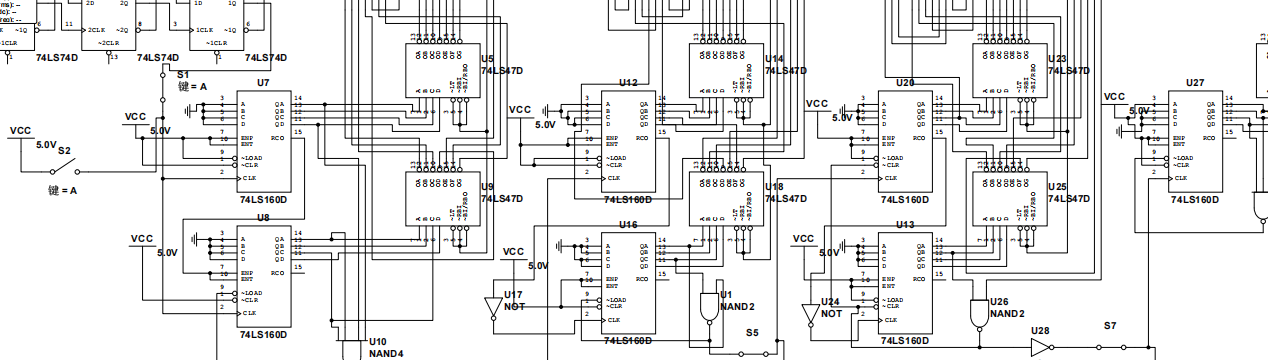

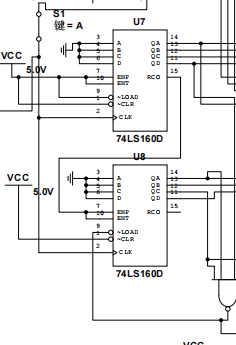

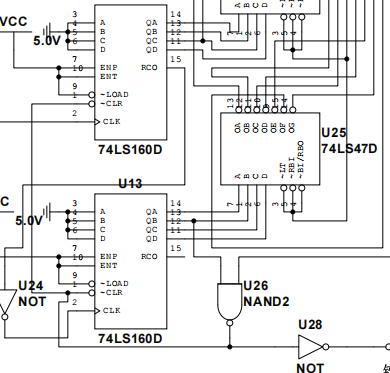

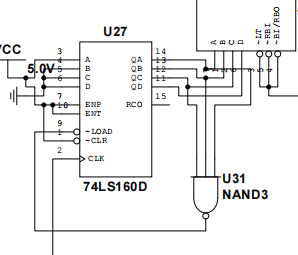

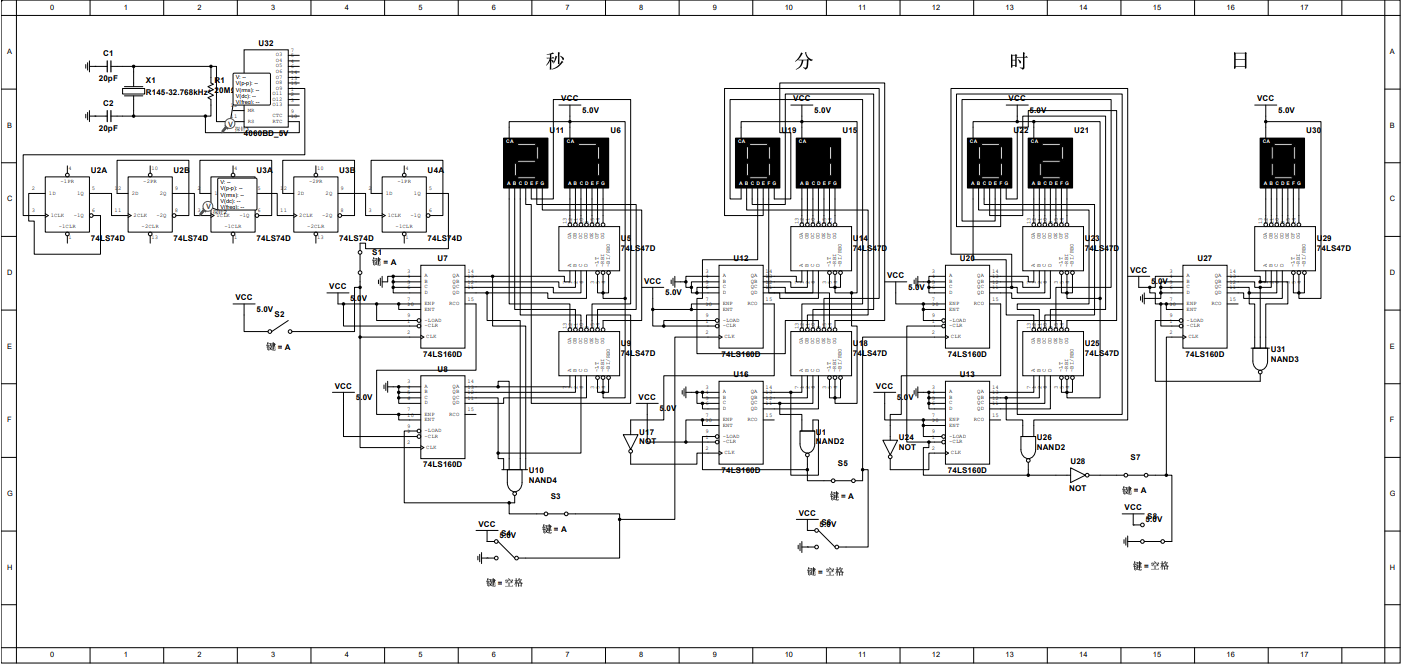

这部分电路由下面几部分构成: 60进制计数器24进制计数器7进制计数器使用60进制计数器、24进制计数器和7进制计数器来实现一个计数电路。这三种计数器都是数字计数器,可以实现数字的累加和显示。其中,60进制计数器可以用于计算秒、分和小时的计数,24进制计数器可以用于计算小时的计数,而7进制计数器则可以用于计算星期的计数。 设计思路如下: 选择合适的计数器。常见的60进制计数器有CD4060和CD4518,常见的24进制计数器有CD4020和CD4060,常见的7进制计数器有CD4514和CD4518。这些计数器都可以实现数字累加和显示,而且比较容易获取。在这里我们选择用74LS160十进制计数器来实现60进制计数器、24进制计数器和7进制计数器。 连接计数器。您需要将60进制计数器的输出连接到24进制计数器的时钟输入,将24进制计数器的输出连接到7进制计数器的时钟输入。这样就可以实现秒、分、小时和星期的计数。 提供时钟信号。您可以使用晶振或其他时钟源来提供时钟信号,以确保计数器的计数准确。 连接显示器。您需要将计数器的输出连接到显示器上,以显示当前的计数。您可以使用LED数码管或LCD显示器来显示计数。

74LS160是一种可重置的同步计数器,可以实现数字的累加和显示。以下是具体的思路和电路设计: 60进制计数器设计思路: 使用74LS160计数器来实现60进制计数器,需要将计数器的时钟输入连接到一个60 Hz的时钟源,然后将计数器的输出连接到一个分频器。分频器可以将计数器的输出分频60倍,以实现60进制计数器。最后,将分频器的输出连接到数码管显示器,以显示当前的计数值。

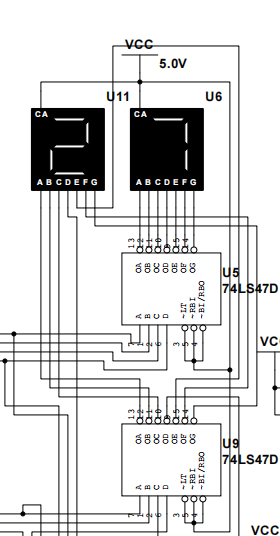

这部分电路由下面几部分构成: BCD-7位数码管译码器74LS47D7位数码管BCD-7位数码管译码器74LS47D是一种常用的数字译码器,可以将二进制代码转换为7位数码管的输出信号,以实现数字的显示。以下是具体的思路和电路设计: 确定输入信号: 首先,需要确定需要显示的数字,然后将其转换为二进制代码。例如,如果需要显示数字5,则其对应的二进制代码为0101。连接74LS47D译码器: 将74LS47D译码器的VCC引脚连接到电源正极,将GND引脚连接到电源负极。然后,将译码器的A、B、C和D输入引脚连接到二进制代码的对应引脚。例如,如果您需要显示数字5,则将A、B、C和D引脚连接到对应的引脚,即A引脚连接到第2个引脚,B引脚连接到第3个引脚,C引脚连接到第4个引脚,D引脚连接到第5个引脚。连接数码管: 将74LS47D译码器的a、b、c、d、e、f和g输出引脚连接到7位数码管的对应引脚。例如,将a引脚连接到数码管的a引脚,将b引脚连接到数码管的b引脚,以此类推。连接限流电阻: 为了保护数码管和译码器,需要在其之间连接合适的限流电阻。通常,限流电阻的阻值为220欧姆,可以有效限制电流,避免数码管和译码器受到损坏。 四、整机电路图

四、整机电路图

整机电路图如下:

设计实验的过程是一个从无到有的过程,从开始完全没有思路,到了解大体的设计, 从不理解与按键功能到熟知元件用法,最终设计出完整的实验设计图。在这个过程中,需 要我们查找相关书籍或上网查找相关资料获得实验器材的功能及用途,并且讨论分析电路 连接及各部分电路功能。很好的锻炼了我们的动手能力,并且获得更多的知识。这次设计 培养了我运用所学理论知识和技能,分析解决计算机应用实际问题能力。以及掌握设计计 算机课题地思想和方法,树立严肃认真工作作风和调查研究、查阅技术文献、资料、手册 及编写技术文献地能力。同时在生产实践中所涉及地一些实践问题,又促使我带着疑问积 极地探索。进行设计从知识技能地准备到心理地充分认识都具备了较好地基础。设计实验 是辛苦的,但在辛苦的同时我们获得了更多更多的知识,一分耕耘一分收获,我们付出了 努力,也收到了回报 |

【本文地址】