FPGA基础实验:驱动ADC0809芯片并显示十六进制数据;另外扩展sm101状态机检测。 |

您所在的位置:网站首页 › 灰色16进制代码 › FPGA基础实验:驱动ADC0809芯片并显示十六进制数据;另外扩展sm101状态机检测。 |

FPGA基础实验:驱动ADC0809芯片并显示十六进制数据;另外扩展sm101状态机检测。

|

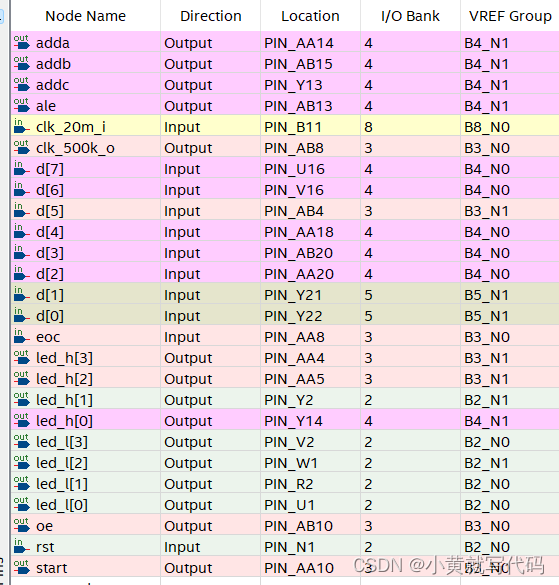

1.贴上cyclone 10 LP上的芯片引脚绑定: 首先是ADC芯片的:

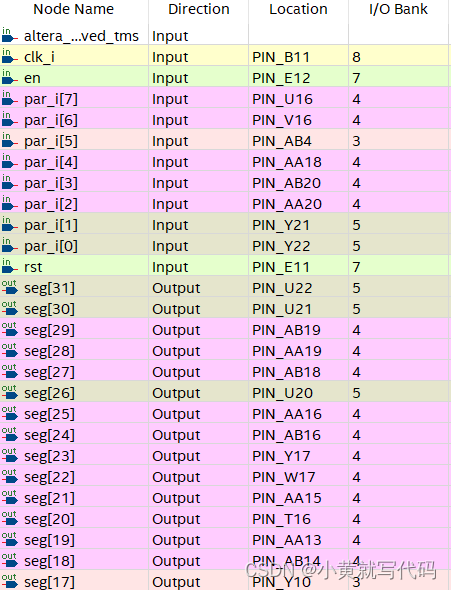

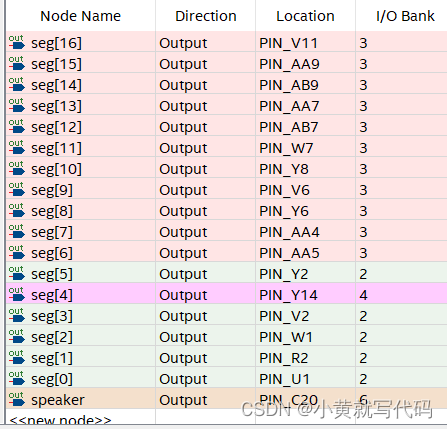

其次是sm状态机的:

2.贴上代码:内涵注释: 首先是ADC: module ADC_top(clk_20m_i,clk_500k_o,rst,eoc,d,adda,addb,addc,led_h,led_l,ale,start,oe); input clk_20m_i,rst,eoc; //clk20mi是指fpga本身的20mhz时钟,rst是复位信号 //eoc是查询忙标志,为0是忙 input [7:0]d;//表示adc转换结果 output ale,start,oe; //fpga控制线,ale是允许地址线信号发送标志,1为真 //start是启动转换信号,理论上ale和start可以用一个信号表示; //oe是允许转换结果输出;以上三个为1时为真 output clk_500k_o; //adc的工作时钟信号 output adda,addb,addc;//输出控制线 output [3:0] led_h;//高四位数字 output [3:0] led_l;//低四位 wire[7:0]q; wire clk_5m_o;//状态机时钟 wire lock_t; PLL PLL_U1(.inclk0(clk_20m_i), .c0(clk_500k_o), .c1(clk_5m_o)); ADC0809 ADC0809_U1( .d(d), .clk(clk_5m_o), .eoc(eoc), .rst(rst), .ale(ale), .start(start), .oe(oe), .adda(adda), .addb(addb), .addc(addc), .q(q), .lock_t(lock_t) ); seg7 SEG7_U2( .a(q[7:4]), .led7s(led_h) ); seg7 SEG7_U1( .a(q[3:0]), .led7s(led_l) ); endmodule module seg7(a,led7s);//控制数码管模块 input [3:0]a; output reg[3:0] led7s; always@(a) case(a) 4'b0000:led7s=4'b0000; 4'b0001:led7s=4'b0001; 4'b0010:led7s=4'b0010; 4'b0011:led7s=4'b0011; 4'b0100:led7s=4'b0100; 4'b0101:led7s=4'b0101; 4'b0110:led7s=4'b0110; 4'b0111:led7s=4'b0111; 4'b1000:led7s=4'b1000; 4'b1001:led7s=4'b1001; 4'b1010:led7s=4'b1010; 4'b1011:led7s=4'b1011; 4'b1100:led7s=4'b1100; 4'b1101:led7s=4'b1101; 4'b1110:led7s=4'b1110; 4'b1111:led7s=4'b1111; default :led7s=4'b0000; endcase endmodule module ADC0809( d, clk, eoc, rst, ale, start, oe, adda, addb, addc, q, lock_t );//adc模块驱动程序,也是一个状态机程序 parameter s0=5'b00001, s1=5'b00010, s2=5'b00100, s3=5'b01000, s4=5'b10000; input [7:0]d;//通过0809转换好的8位数据 input clk,rst,eoc;//输入时状态机时钟,也就是系统时钟, //rst复位,eoc是转换状态指示,高电平转换完毕,低电平正在转换 output ale,start,oe; output lock_t; reg ale,start,oe; // reg lock_t; //ale和start是允许和开始标识, //oe是允许输出信号; //lock_t是所处测试信号 output adda,addb,addc;//地址线 output [7:0]q; reg lock;//数据输出时钟信号 reg[4:0] state,next_state; reg[7:0] regl;//保存数据 assign lock_t=lock; assign adda=0; assign addb=0; assign addc=0; always@(posedge clk or posedge rst)//状态方程 begin if(rst) state |

【本文地址】

今日新闻 |

推荐新闻 |