AArch32中thumb指令的IT block 解释,IF‐THEN 块由 IT 指令定义,IT指令类似MOV的一条汇编指令的助记符号 |

您所在的位置:网站首页 › 汇编if › AArch32中thumb指令的IT block 解释,IF‐THEN 块由 IT 指令定义,IT指令类似MOV的一条汇编指令的助记符号 |

AArch32中thumb指令的IT block 解释,IF‐THEN 块由 IT 指令定义,IT指令类似MOV的一条汇编指令的助记符号

|

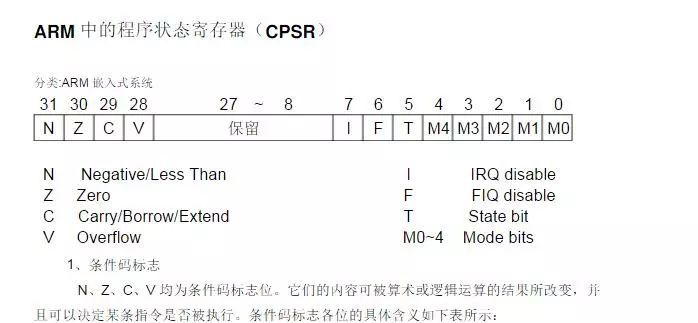

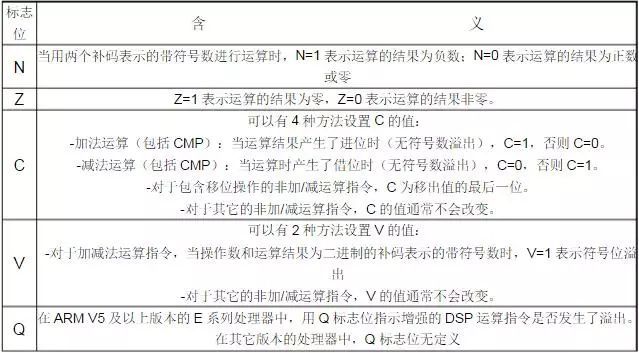

2018-11-09 17:29 IT block是thumb指令集中引出来的东西,用来解决thumb指令不能条件执行的缺点。可以通过IT指令,给后续的1到4条指令,决定其执行条件。 IT block的信息,存放在PSTATE中,在thumb指令集中,也就是存在CPSR中。存放在CPSR的IT域。( 过去,对中断的使能和除能是通过修改 CPSR 的,在 CM3 中没有 CPSR,而是使用 PRIMASK 或 FAULTMASK 来实现全局中断的开关。 )

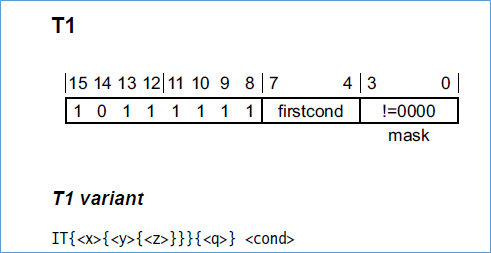

IT指令的指令编码如下:

其汇编描述:

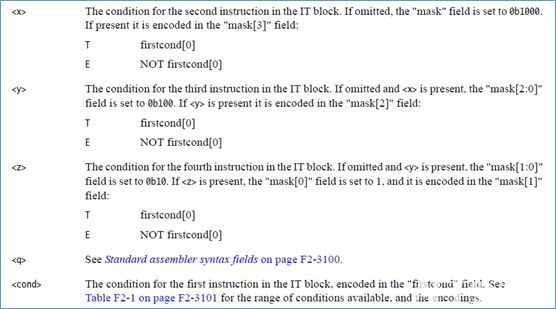

一、IT域的初始值 那CPSR中的IT域是如何记录IT block的状态的。 IT域在初始的时候,是如下记录IT block状态的。

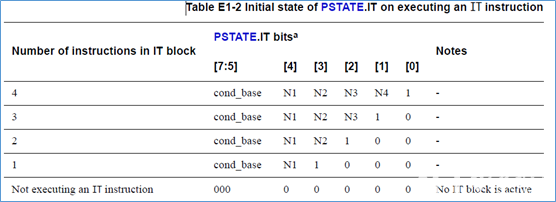

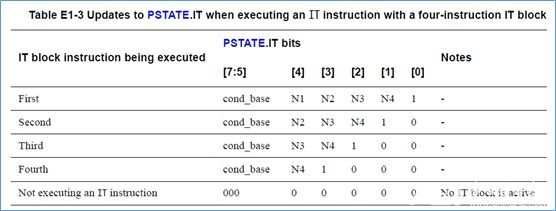

图中的N1,N2,N3,N4,对应IT指令之后的4条指令。 IT指令,在译码的时候,根据firstcond和mask域,就可以知道,后续有几条指令,会在IT block中,以及每条指令执行的条件。然后根据有几条指令,将对应的值,填充到CPSR的IT域中。 比如如下指令 ITTET EQ(EQ的编码是0000) 根据ITTET,确定出之后的IT block,有4条指令。并且第0条,第1条,第3条和EQ条件一致,第2条和EQ条件相反。此时CPSR中的IT域填充如下值 [7:5] [4] [3] [2] [1] [0] 3'b000 0 0 1 0 1 比如如下指令 ITEE PL(PL的编码是0101) 根据ITTE,确定出之后的IT block,有3条指令。并且第0条,和PL条件一致,第1条,第2条和PL条件相反。此时CPSR中的IT域填充如下值: [7:5] [4] [3] [2] [1] [0] 3'b010 1 0 0 1 0 二、IT域的变化 以上只是CPSR的IT域的初始值,那么在执行IT block中指令过程中,IT域又是如何变化的呢? 下图是IT域随着IT block中4条指令的执行情况的变化表。可以看出,IT[7:5]不变,IT[4:0]在执行完一条指令之后,就左移一位。IT[7:4]组成新的条件码,来决定指令的运行条件。

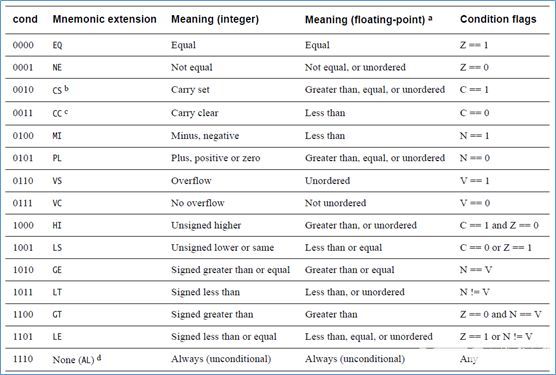

三、IT block的局限 处于IT block中的指令,其条件,要不就是和IT指令限定的条件相同,要不就是相反,不能有其他情况,不能像A32那样,可以灵活的为每条指令,设定执行条件。 下图是arm定义的条件码的编码,可以看出2个条件码一个组合,且最后一个bit是相反的关系。这也是为什么条件码的高3个bit,要存放在IT[7:5]中,剩下一个bit,依赖于IT[4]即可。

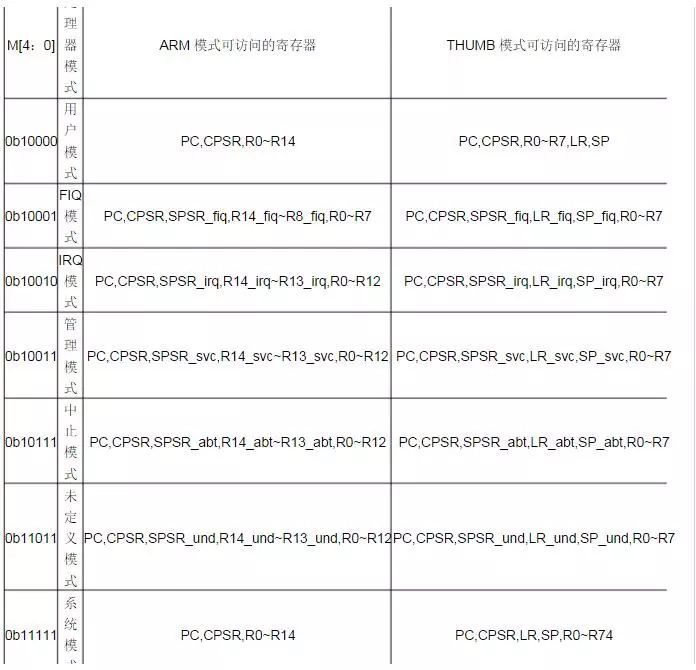

https://www.sohu.com/a/274296837_781333 ARM寄存器与汇编指令详解2018-04-08 11:23 介绍ARM寄存器之前,先来介绍一下ARM处理的模式 用户模式(User):ARM处理器正常的程序执行状态快速中断模式(FIQ):用于高速数据传输或通道处理外部中断模式(IRQ):用于通用的中断处理管理模式(Svc):操作系统使用的保护模式数据访问中止模式(Abort):数据或指令预取终止时进入该模式,用于虚拟存储及存储保护系统模式(System):运行具有特权的操作系统任务未定义指令中止模式(Undifined):当未定义指令运行时进入该模式,可用于支持硬件协处理器的软件仿真 然后再来介绍下ARM寄存器组 ,ARM共有37个32bit的寄存器,其中31个为通用寄存器,6个为状态寄存器,这些寄存器不能被同时访问,但是在任何时候,通用寄存器R0-R14,程序计数器PC,一个或者两个状态寄存器是可以访问的。

通用寄存器分为3类 1.未分组寄存器R0-R7 在上面所指的运行模式下,未分组寄存器都指向同一个物理寄存器,它们未被系统用作特殊用途,因此在中断或者异常处理进行模式转换时,由于不同的处理模式受用相同的物理寄存器,所以会造成寄存器中数据的破坏。 2.分组寄存器R8-R14 对分组寄存器来说,每一次访问的物理寄存器都与当前的运行模式有关,R8-R12每个寄存器对应两种不同的物理寄存器,当使用FIQ(快速中断模式)时,访问寄存器R8_fiq–R12_fiq,当访问除FIQ模式以外的其它模式时,访问R8_usr–R12_usr. R13,R14每个寄存器对应6个不同的物理寄存器,其中一个是用户模式与系统模式共用,另外5个物理寄存器对应其它5中不同的运行模式R13_XXX 与R14_XXX(XXX = usr,fiq,irq,svc,abt,und) 。 R13在ARM指令集中常用作堆栈指针SP,R14称为链接寄存器(LR),当执行子程序调用BL指令时,R14可以得到R15(程序计数器PC)的备份,在每一种运行模式下,都可用R14保存子程序的返回地址,当用BL或BLX指令调用子程序时,将PC的当前值复制给R14,执行完子程序后,又将R14的值复制给PC,即完成子程序的调用返回。 3.程序计数器PC(R15) ARM状态下bit[1:0]为0,bit[31:2]用于保存PCThumb状态下bit[0]为0,bit[31:1]用于保存PC由于ARM体系结构采用多级流水线技术,对应ARM指令集而言,PC总是指向当前指令的下两条指令的地址,及PC的值为当前指令的地址增加8个字节(两条指令*32bit)4.R16也称为CPSR(Current Program Status Register当前程序状态寄存器) CPSR可在任何模式下被访问,它包括条件控制位、中断禁止位、当前处理器模式标志位,每一种模式下都有一个专用的物理状态寄存器,称为SPSR(Saved Program Status Register,备份的程序状态寄存器),当异常发生时,SPSR用于保存CPSR的当前值,从异常退出时则可由SPSR恢复CPSR,由于用户模式和系统模式不属于异常模式,它们没有SPSR。 CPSR详解如下:

ARM指令的寻址方式 1.立即寻址 ADD R0, R0, #0x1 ;R0 |

【本文地址】

今日新闻 |

推荐新闻 |