使用Proteus 8.4仿真数字钟,提供源文件 |

您所在的位置:网站首页 › 整点报时哪个软件好用 › 使用Proteus 8.4仿真数字钟,提供源文件 |

使用Proteus 8.4仿真数字钟,提供源文件

|

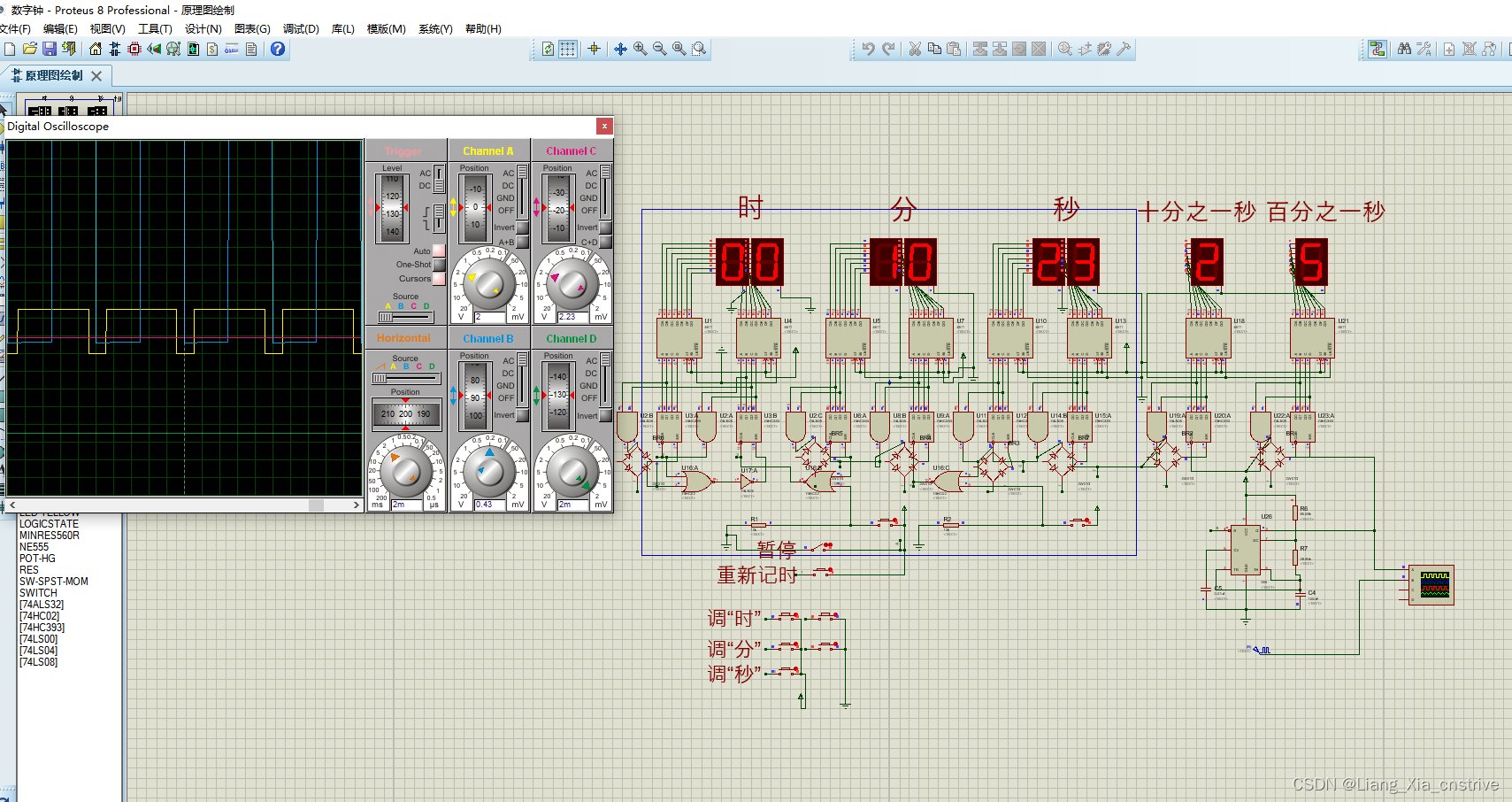

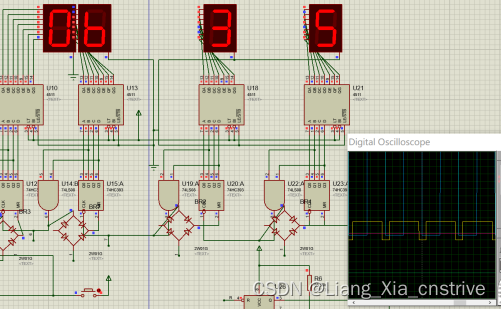

效果图:

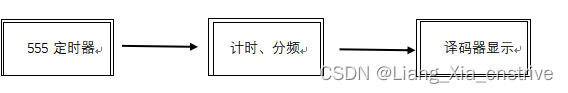

初始条件利用集成译码器、计数器、定时器、脉冲发生器和必要的门电路等器件设计实现数字秒表的功能。用数码管显示时间计数值,计数范围为时、分、秒、十分之一秒、百分之一秒。 2、多功能数字秒表方案设计与论证电子秒表的工作原理就是不断输出连续脉冲给加法计数器,而计数器通过译码器来显示它所记忆的脉冲周期个数。 1.时钟发生器:利用电子元器件555定时器构成的多谐振荡器做时钟源,产生脉冲。 2.记数器:对时钟信号进行记数并进位,百分之一秒和十分之一秒以及个位秒之间10进制,十位秒为六进制,十位分为六进制,十位时为二进制;本设计采用可预置的十进制同步加法计数器CD4511构成电子秒表的计数单元。 3.译码器:对脉冲记数进行译码输出到显示单元中。 4.显示器: 采用8片LED显示器把各位的数值显示出来,是数字钟最终的输出。共有8位,精确到百分之一秒;CD4511是BCD码到七段码的显示译码器。 5.控制器:控制电路是对秒表的工作状态(记时开始/暂停/调时,分,秒)进行控制的单元。属于电平直接通过控制触发器来实现。 3、多功能数字秒表总体设计

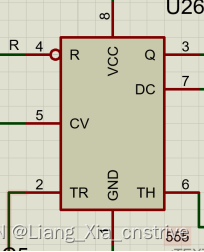

用555实现多谐振荡产生频率为100Hz的方波(即周期为0.01秒的方波) (1)555 电路的工作原理

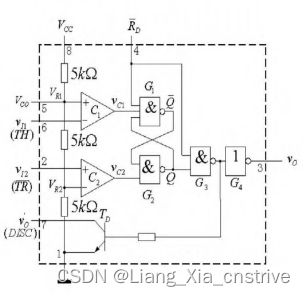

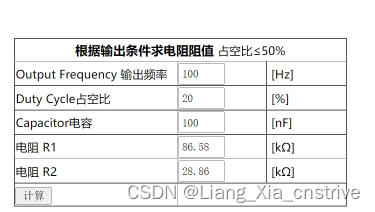

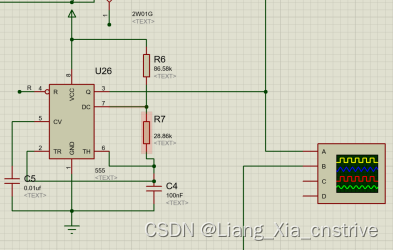

图4.1 555管脚图 图4.2 555内部原理图 555电路的内部电路方框图如图4-2所示。它含有两个电压比较器,一个基本RS触发器,一个放电开关管T,比较器的参考电压由三只5KQ的电阻器构成的分压器提供。它们分别使高电平比较器C1的同相输入端和低电平比较器C2的反相输入端的参考电平为2/3Vcc和上 1/3Vcc。C1与C2的输出端控制RS触发器状态和放电管T的开关状态。当输入信号自6脚即高电平触发输入并超过参考电平2/3Vcc时,触发器复位,555的输出端3脚输出低电平,同时放电开关管T导通:当输入信号自2脚输入并低于1/3Vcc时,触发器置位,555的3脚输出高电平,同时放电开关管截止。4脚是复位端R,当R=0,555的3脚输出低电平。平时R,端开路或接Vcc,5脚Vco是控制电压端,平时输出2/3Vcc作为比较器C1的参考电平,当5脚外接一个输人电压,即改变了比较器的参考电平,从而实现对输出的另一种控制,在不接外加电压时,通常接一个0.047uf的电容器接地,起滤波作用,以消除外来的干扰,确保参考电平的稳定。T为放电管,当T导通时,将给接于脚7的电容器提供低阻值的放电通路。 555定时器主要是与电阻、电容构成充放电电路,并由两个比较器来检测电容器上的电压,以确定输出电平的高低和放电开关管的通断。这就很方便地构成从微秒到数十分钟的延时电路,可方便地构成单稳态触发器,多谐振荡器,施密特触发器等脉冲产生或波形变换电路。 (2)构成多谐振荡器 如图4-3(a),由555定时器和外接元件R、R,、C,构成多谐振荡器,脚2与脚6直接相连。电路没有稳态,仅存在两个暂稳态,电路亦不需要外加触发信号,利用电源通过电阻向C充电,以及C通过R向7脚放电端C放电,其波形如图4-3(b)所示。计数公式: 脉冲的高电平宽度 tH=0.693(R1+R6+R7)C1 低电平宽度 tL=0.693(R6+R7)C1 脉冲周期 T=tH+tL=0.693(R1+2R6+2R7)C1 脉冲频率 f=1/T=1.44 /[0.693(R1+2R6+2R7)C1] 占空比为 (R1+R6+R7)/(R1+2R6+2R7)。 根据计算公式,本次课程设计的电阻R6=86.58kΩ,R7=28.86 kΩ,C4=100nF,占空比为20%。具体计算结果如下。

图 4-3(a)

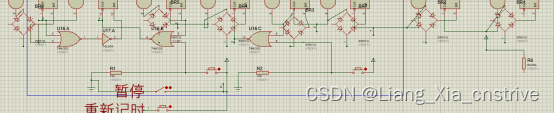

图 4-3(b) 外部元件的稳定性决定了多谐振荡器的稳定性,555定时器配以少量的元件即可获得较高精度的振荡频率和具有较强的功率输出能力。因此这种形式的多谐振荡器应用很广。 4.2总清零控制电路如图4-4为电路的总清零控制电路,该电路在开关合上之后会输出高电平,作用于各个74HC393的MR端,实现清零功能;开关断开之后输出低电平,电路处于计时状态。总清零控制电路便于实现电路的总的清零控制,同时也对时钟脉冲起到控制作用。

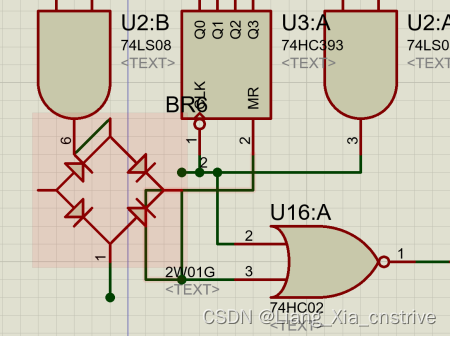

图4-4 清零电路 4.3时间计数单元555元器件的脉冲信号通过CLK端输入74HC393,脉冲信号频率设置为100hz,即一个脉冲信号代表0.01s,输入一次交变的信号,393进入一次计数,输出一次状态。通过数据手册观察到Q1,Q3第次同时 为高电平时为第十次计数,即计数0.01s,向前进位1。电路上通过连接Q13的一个与门来判断是否进位。当进位后,分出两个支路,一个连向控制下一位数码管的74HC393CLK端,通过信号的变化从而使其计数加一;另-端连向自身的MR端,当MR接收到变化的信号后,将数码管重新置零。 时分秒的进位与百分秒和十分秒的进位类似,区别是进位标志从10变为60或24。且在分与时的下方存在一个或非门,正常不进位状态输入端低电位。当按下按钮或产生信号变动时,输出高电平,CK接收到交变的信号,计数加一。小时位满后置0与分秒位不同,当进位到24后,两个与1门输入高电平,或非输出低电平,经过非门输出高电平,信号产生变化后使小时位归零。

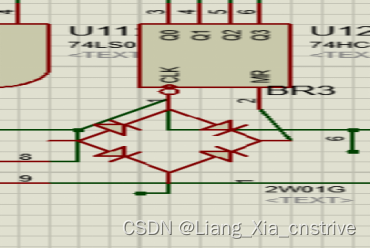

图4-5 时计数 4.4调时功能模块本实验用到的调时主要模块是电流桥,通过电流桥的特效和数字进位特点,可使调时过程不影响进位功能的正常使用。以便于每次给予高频信号都能使MR触发功能都能独立准确的收到。如图4-6所示。

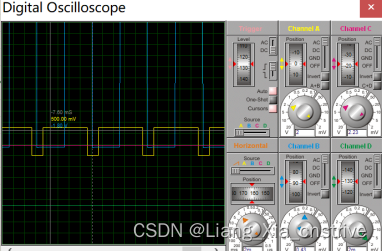

图4-6 调时功能 5、对比测试通过系统加入的时钟模拟信号与555元器件发出的脉冲信号进行对比,进行精度校准。系统加入的时钟模拟信号的频率为100HZ 0.01s。通过图5-1(a)、图5-1(b)对比发现,555元器件与系统加入的时钟模拟信号周期完全一致,即频率相等,因此本实验设计合理。

图5-1(a) 对比校准(6s时的波形图)

图5-1(b) 对比校准(14s时的波形图) |

【本文地址】

今日新闻 |

推荐新闻 |