浅聊数字后端中的 时序减免(timing derate) |

您所在的位置:网站首页 › 数字后端uncertain如何设置 › 浅聊数字后端中的 时序减免(timing derate) |

浅聊数字后端中的 时序减免(timing derate)

|

"引文:当芯片进入深亚微米设计时,工艺制造的偏差对芯片时序的影响越来越大。实际分析时,通常不会同时读入最好和最坏两个时序库。最好和最坏时序库之间的分析结果差距太大。如果检查setup,launch path的时钟用最坏的时序库,capture path的时钟用最好的时序库。那么在ocv模式分析下的时序结果会过于悲观。反过来当分析hold的时候,用最好的和最坏的时序库,那么结果也会过于悲观。" ——以上内容大部分引用 刘峰 编著的《集成电路静态时序分析与建模》 因此在实际的时序分析中,一次只读入一套时序库,然后采用 时序减免 的方法,就可以使最后的结果没有那么的悲观。 关于ocv,全称on-chip variation,简单来说就是 比如两个相同的BUFFER,在其他条件相同的情况下,当他们处在芯片的不同位置,他们实际的delay却是不同的。详细的可以再百度看看,这里就不另做说明了。

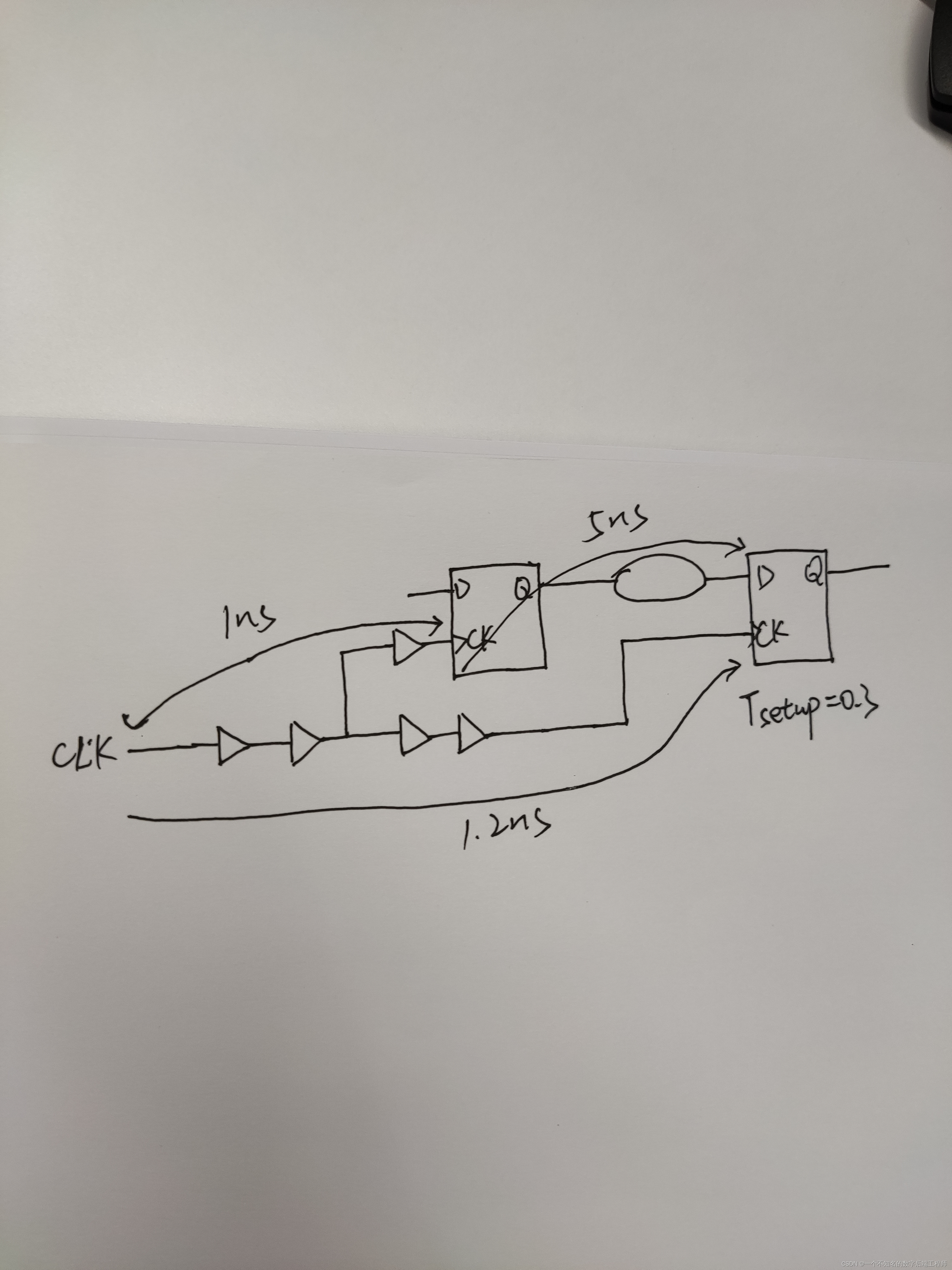

那么首先有以下几个问题: 1.时序减免的目的是什么? 2.如何实现这一过程? 答: 1.目的是使时序分析的结果更加趋向于实际情况。 2.静态时序分析工具(PT)使用set_timing_derate来定义时序减免值。 举个例子。如下图所示,这是一条典型的时序路径

上图中: ①launch path的delay为1+5=6ns,这个6ns是launch path的最慢路径延迟,下文简称T_launch;②capture path的delay为1.2ns,而这个1.2是capture path的最快路径延迟,下文简称T_cap; ③setup的值为0.3ns,下文简称T_setup。 当没有设置 时序减免 值的时候,在ocv模式下,为满足时序要求的时钟周期为: T_launch+T_setup≤T_cap+T T≥T_launch+T_setup-T_cap T≥6+0.3-1.2=5.1ns 当设置 时序减免 值的时候,如下设置 set_timing_derate -early 0.9 set_timing_derate -late 1.2 这两条命令表示:①将最快路径延迟,也就是T_cap的延迟乘以0.9;②将最慢的路径延迟,也就是T_launch的延迟乘以1.2; T_cap=1.2×0.9=1.08ns T_launch=6×1.2=7.2ns T≥7.2+0.3-1.08=6.42ns 从上面的表达式可以看出T_cap变的更小了,T_launch变的更大了。那么T的最小周期也需要变大。(也就是频率要降低) 当不考虑 时序减免 的情况下,也就是趋向于理想的情况下,周期要≥5.1ns才满足时序要求。 当考虑到 时序减免 的情况下,也就是考虑到实际情况下,周期要≥6.42ns才满足时序要求。(相对于不考虑 时序减免 的那种情况,这样情况下,频率需要降低,这也就符合我们预期的想法) 就是这 就回答了上文中的第一个问题,设置时序减免的目的是 使时序分析的结果更加趋向于实际情况。 最后,以上内容皆是个人见解,如有哪里不对的地方,还请告知。

|

【本文地址】

今日新闻 |

推荐新闻 |