FPGA历险记 |

您所在的位置:网站首页 › 带宽是怎么计算的 › FPGA历险记 |

FPGA历险记

|

FPGA历险记——DDR3之带宽、位宽和频率使用

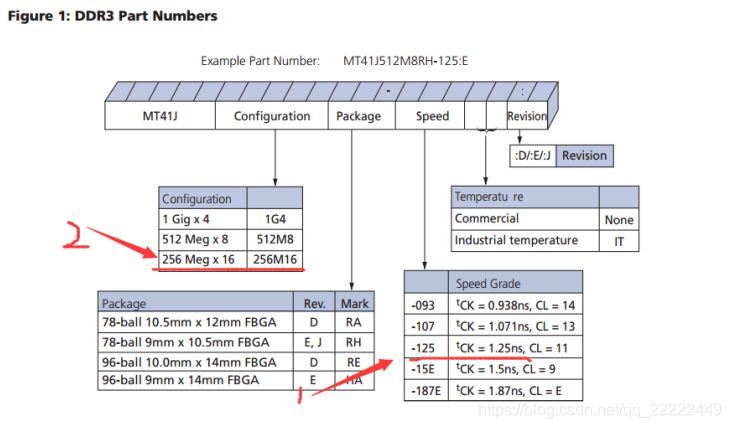

本节主要介绍如何从DDR3的芯片选型和FPGA芯片选型来确定MIG的一些参数, 一、如何确定DDR3芯片的带宽、位宽和最大IO时钟频率这里以芯片Part Number :MT41J256M16RH-125:E为例,打开芯片的数据手册,会找到如下所示的介绍:

IO时钟频率: 根据Part Number 中的“-125”我们就可以找到图中的“1”,根据这里tCK = 1.25ns,就可以算出芯片支持的最大IO时钟频率:1/1.25ns = 800Mhz; 位宽: 根据Part Number 中的“256M16”我们可以找到图中2所指出的地方,这里的16是代表芯片的数据位宽是16位(也就是16根数据线)。 带宽: 由于是DDR方式传输数据(上升和下降沿都传输),所以芯片的一根数据线上的传输速率 = 2*800Mhz = 1600MT/s。其实就是1600Mbit/s; 带宽就是16根数据线同时传输的数据速率 = 1600Mbit/s x 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s 关于DDR3跟详细的介绍,请看本系列的其他文章 二、如何确定MIG最大支持的时钟频率这里以xilinx Artix-7系列的FPGA为例,具体型号为xc7a100tfgg484-2。打开对应的datasheet(ds181),找到如下图所示的介绍(第15页):

从上图中红线标出的地方可以看出,此FPAG芯片的MIG支持最大PHY速率是800Mb/s(注意,这是数据传输速率)。因为是使用DDR模式传输数据,所以最大时钟频率 = 800/2 = 400Mhz。(还记得刚刚DDR3 芯片支持的最大IO时钟频率吗?800Mhz,在下面的MIG参数设置中,就会用到这两个参数)。 三、MIG IP 中如何根据以上信息来设置时钟参数在说具体的时钟参数设置之前,我们先来看一张图 MIG 的 Clocking Architecture

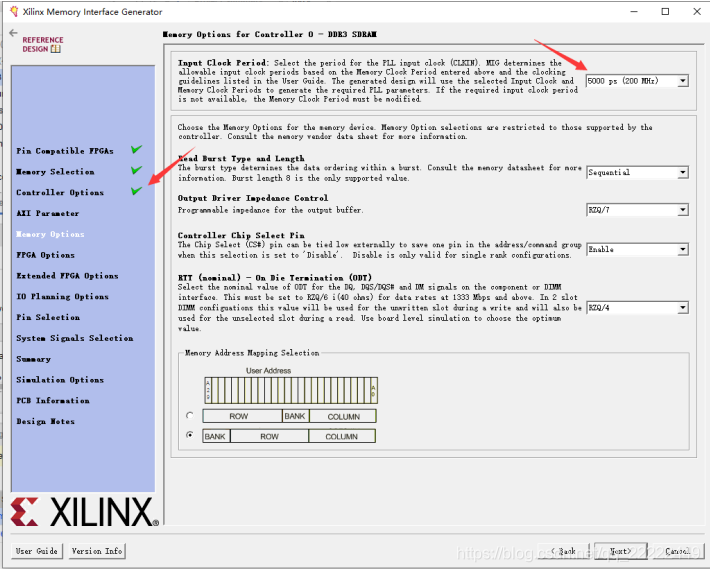

根据本图很明显的告诉了我们,需要给MIG提供两个时钟,一个叫system clock(主时钟),一个叫reference clock(参考时钟)。 但是在MIG中,如何对这些时钟参数进行设置(描述)呢?看好了,接下来开始画重点了!!!!! 在MIG中,涉及到对时钟参数进行设置(描述)的地方有四处,接下来我们一个一个的看: 第一处,如下图所示

这里设置的参数就是 MIG 的PHY 接口对DDR3的时钟,也就是DDR3芯片实际跑的IO时钟频率,它由system clock(主时钟)倍频而来,最大频率不能超过DDR3 和MIG支持的最大频率中的最小值,如:虽然我们的DDR3芯片最高支持800Mhz的IO时钟,但是由于我们使用的FPGA芯片的MIG最高只支持400Mhz的时钟,所以这里我们选择400Mhz(当然也可以选择比这个小)。下面有个4:1,说明MIG 输出到app接口上的时钟ui_clk 是 400M/4=100M ,即到时我们在写RTL逻辑代码时操作MIG核时,用的就是这个100M时钟。 第二处、还是如图所示

这里就是设置system clock(主时钟)的输入频率,实际是多少就写多少。 第三、四处,继续如下图所示

图中的“3”是设置(描述)system clock (主时钟)是差分输入还是单端等其他形式的输入,这里我们选择差分输入 同理,图中的“4”是对reference clock(参考时钟)进行描述。主意:如果system clock 频率设置为200Mhz(看第二处),这里就可以直接选“Use System Clock”,否则就没有“Use System Clock”这个选项,要是选其他选项,后面还需要对reference clock进行设置,如下图所示

关于MIG其他详细介绍,以后会持续更新 因能力所限,难免有理解不到位之处,欢迎大家批评指正 更多分享,请关注微信公众号:FPGA历险记

|

【本文地址】