计组期末模拟(补充) |

您所在的位置:网站首页 › 字扩展和位扩展原理 › 计组期末模拟(补充) |

计组期末模拟(补充)

|

单选题

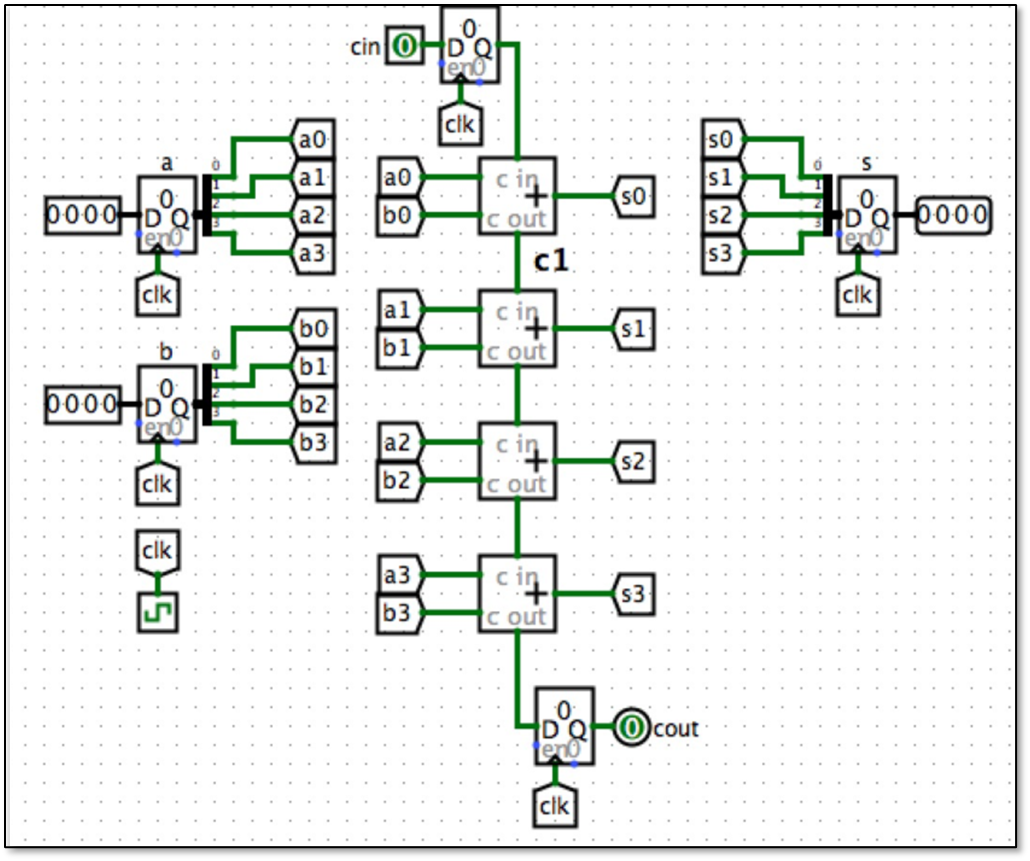

2-1(本题考查课程目标2) 某计算机有 16 个通用寄存器,采用 32 位定长指令字,操作码字段(含寻址方式位)为 8 位,Store 指令的源操作数和目的操作数分别采用寄存器直接寻址和基址寻址方式。若基址寄存器可使用任一通用寄存器,且偏移量用补码表示,则 Store 指令中偏移量的取值范围是( )。 A.-32767 ~ +32768 B.-32768 ~ +32767 C.-65535 ~ +65536 D.-65536 ~ +65535 2-2(本题考查课程目标2) 一个 16K*32位的SRAM存储芯片,其内部采用位数相同的行列地址译码器,则其内部译码输出线的总量为( )。 A. 2 7 2^7 27 B. 2 8 2^8 28 C. 2 14 2^{14} 214 D. 2 16 2^{16} 216 2-3(本题考查课程目标2) 一个 16K*32位的SRAM存储芯片,其数据线和地址线之和为( )。 A.46 B.48 C.36 D.39 2-4(本题考查课程目标2) 按字节编址的计算机中,某 double 型数组 A 的首地址为 2000H,使用变址寻址和循环 结构访问数组 A,保存数组下标的变址寄存器初值为 0,每次循环取一个数组元素,其偏移地 址为变址值乘以 sizeof(double),取完后变址寄存器内容自动加 1。若某次循环所取元素的地址 为 2100H,则进入该次循环时变址寄存器的内容是( )。 A.25 B.32 C.64 D.100 填空题4-3(本题考查课程目标2) 某计算机系统采用32位单字长定长指令,最多具有3个地址码字段,每个地址码字段位宽为8位。假设扩展操作码指令系统中有三地址指令254条、双地址指令511条、单地址指令245条,则该指令系统最多可以设计 2816 (3分) 条零地址指令(仅填数字即可)。 4-4(本题考查课程目标2) 某计算机采用大端方式,按字节编址。某指令中操作数的机器数为1234FF00H,该操作数采用基址寻址方式,形式地址(用补码表示)为FF12H,基址寄存器的内容为F0000000H, 则该操作数的 LSB(最低有效字节)所在的地址是0x EFFFFF15 (4分)(限填大写字母、阿拉伯数字)。 4-5(本题考查课程目标2) 某计算机字长64位,采用三地址指令,支持8种寻址操作,完成112种操作,各寻址方式均可在64K主存范围内取得操作数,并可在32K范围内保存运算结果。则该计算机指令字长最少应为 63 (3分) 位;执行一条指令最多要访问 4 (3分)次主存(限填阿拉伯数字)。 4-6(本题考查课程目标2) 已知某系统如下图所示,Setup Time=3ns,Hold Time=3ns,Clk_to_Q =3ns,Adder Delay=5ns。则该系统的关键路径延迟为 26 (2分)ns,输出寄存器最大Hold Time为 8 (2分)ns。

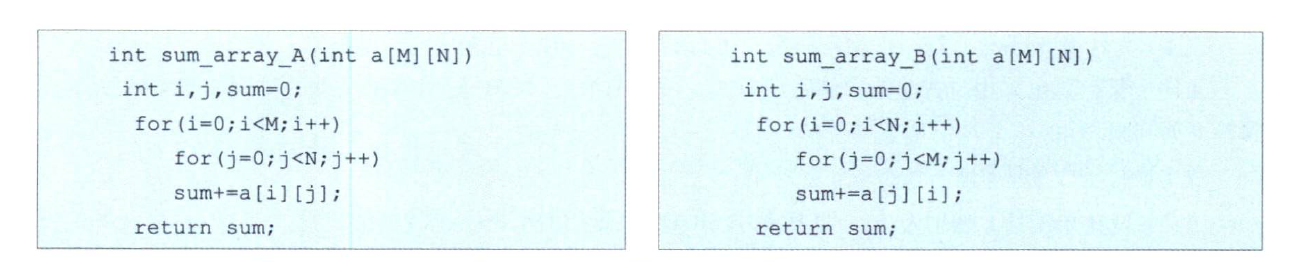

4-7(本题考查课程目标2) 某计算机存储器按字节编址,采用小端方式存放数据。假定编译器规定int 型和 short型长度分别为32 位和16 位,并且数据按边界对齐存储。某C 语言程序段如下: struct{ int a; char b; short c; } record; record.a=273;若record变量的首地址为0xC008,则地址0xC008 中内容为0x 11 (3分),record.c的地址为0x C00E (3分)(限填大写字母、阿拉伯数字)。 主观题8-1【期末模考】假定某数组元素按行优先顺序存放在主存中,试从局部性角度分析A、B程序。 (7分) (本题考查课程目标3) (1)假定某数组元素按行优先顺序存放在主存中,试从局部性角度分析A、B程序。 (2)变量 sum 的时间局部性和空间性。 (3)for 循环体对指令访问的时间局部性和空间局部性。

解: (1)程序 A 中具有很好的空间局部性,不存在时间局部性; 而程序 B 空间局部性不佳,同样也不存在时间局部性; (2)变量 sum 在循环中被多次使用,故具有良好的时间局部性。 (3)for 循环中的指令会被反复循环执行,因此具有较好的时间局部性,另外循环体中 的机器指令序列通常会顺序执行,因此也具有一定的空间局部性。 |

【本文地址】

今日新闻 |

推荐新闻 |