模型机设计(VERILOG) |

您所在的位置:网站首页 › 多路复用器电路图 › 模型机设计(VERILOG) |

模型机设计(VERILOG)

|

一.多路复用器

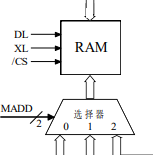

1.功能 从指令计数器PC,寄存器组的S,D口选择一个数据输出给存储器RAM,对应的选择信号MADD分别为00,01,10,y为输出。 2.功能描述代码 always@(a,b,c,MADD) begin case(MADD) 2'b00: y[7:0]=a[7:0]; 2'b01: y[7:0]=b[7:0]; 2'b10: y[7:0]=c[7:0]; default: y="XXXXXXXX"; //由于选择信号只有三种,default的情况可以不写 endcase end 二.移位逻辑1.总线与高阻态 总线是能够传输多位数据的公共数据通路,总线可连接多个部件,完成定向的数据传输。当数据传输时,不需要向总线传输数据的部件处于高阻态,相当于断路,此时数据在部件之间定向传输。使用硬件描述语言中用zz表示高阻态,8'hZZ表示8位数据端口的高阻态。 2.模型机的高阻态 对于模型机,连接在总线上的部件为:指令计数器,通用寄存器组,RAM,移位逻辑,指令寄存器。其中,需要向总线上传输数据的只有移位逻辑,RAM。当RAM或移位逻辑不需要向总线输出数据时,他们的输出应该为高阻态。

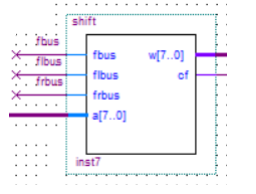

3.移位逻辑功能 移位操作(示例为右移),多余位输出给Cf,将移位后的数据输出。 除了移位操作,还有数据不移位的直接输出,根据模型机结构,函数发生器ALU的输出会给到移位逻辑,当ADD,SUB等运算指令执行时,需要将ALU的结果不移位直接输出到总线,再让通用寄存器组接收总线上的数据,完成运算类指令的执行。 控制移位操作的信号分别为frbus,flbus,fbus,,当三个信号都为0时,输出高阻态,即此时数据不需要输出到总线上,a为输入,w为输出,端口如下:

4.功能描述代码 always@(fbus,flbus,frbus,a) begin cf=1'b0; if(fbus==1'b1) w[7:0]=a[7:0]; else if(frbus==1'b1) begin w[7:0]={a[0],a[7:1]};cf=a[0]; end else if(flbus==1'b1) begin w[7:0]={a[6:0],a[7]};cf=a[7]; end else w[7:0]=8'hZZ; end |

【本文地址】