Vivado使用心得(三)FANOUT解决办法 |

您所在的位置:网站首页 › 复制是啥 › Vivado使用心得(三)FANOUT解决办法 |

Vivado使用心得(三)FANOUT解决办法

|

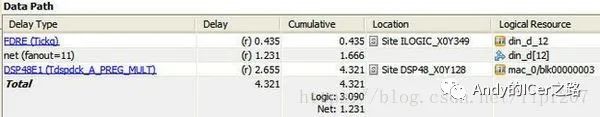

目录 1. 寄存器复制 2. max_fanout属性 3. BUFG 微信公众号 Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化手段解决高扇出带来的问题。以下就介绍三个这样的方法: 首先来看下面这个实例,如图1所示为转置型FIR滤波器中的关键路径时序报告,在DSP in FPGA的FIR专题中有介绍转置型结构FIR滤波器输入数据的扇出较大,在下图中所示为11,因此net delay高达1.231ns,输入数据驱动了11个DSP48E1。 在没有优化情况下,该设计的fmax:206.016MHz

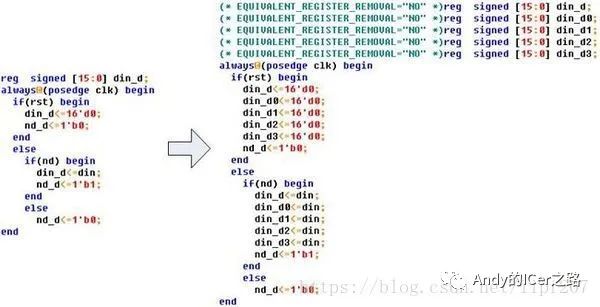

寄存器复制是解决高扇出问题最常用的方法之一,通过复制几个相同的寄存器来分担由原先一个寄存器驱动所有模块的任务,继而达到减小扇出的目的。通过简单修改代码,如图所示,复制了4个寄存器:din_d0、din_d1、din_d2、din_d3,din_d、din_d0、din_d1、din_d2分别驱动2个DSP48E1,din_d3驱动3个DSP48E1。其中在代码中为防止综合器优化相同寄存器,在对应信号上加入了(* EQUIVALENT_REGISTER_REMOVAL="NO" *)属性避免被优化。

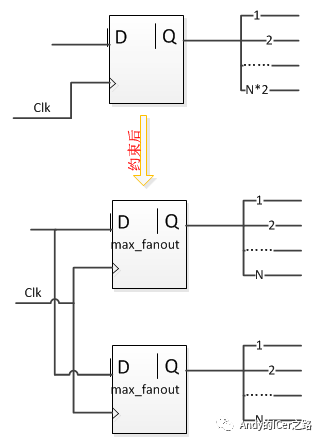

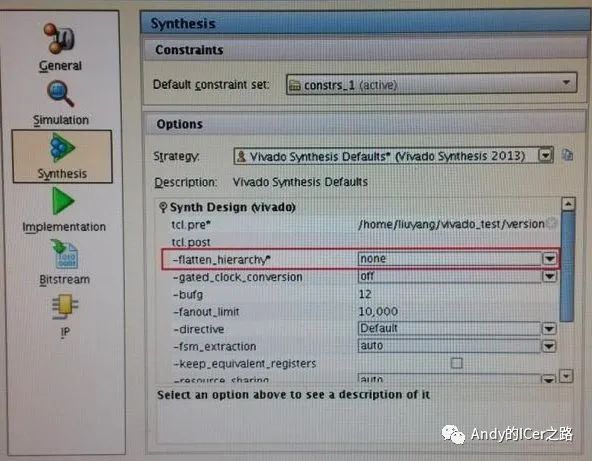

综合实现后得到,该数据路径上输入数据fanout减为2,对应net delay也减小到了0.57ns。得到设计如图5所示,与期望的相同,复制了4个寄存器来分担fanout。经过寄存器优化后得到fmax:252.143MHz 2. max_fanout属性在代码中可以设置信号属性,将对应信号的max_fanout属性设置成一个合理的值,当实际的设计中该信号的fanout超过了这个值,综合器就会自动对该信号采用优化手段,常用的手段其实就是寄存器复制。属性设置如下代码所示: (* max_fanout = "3" *)reg signed [15:0] din_d; 将din_d信号的max_fanout属性设置成3,经过综合实现后,得到fanout只有2,相应的net delay也只有0.61ns,自动优化效果还不错。其中din_d_12_1、din_d_12_2、din_d_12_3是综合器优化后自动添加,即实现了寄存器复制功能。经过设置max_fanout属性优化后得到fmax:257.135MHz vivado中的max_fanout 打算降低扇出的网络必须是reg驱动。因为降低扇出的原理就是reg驱动超过N(设置参数)条网络的时候,就复制一个同样的reg驱动其他N条网络,如果复制2个还不够就一直复制到足够为止,见图1。 -flatten_hierarchy不能设置为none。图形界面设置位置见图2。 如果需要优化的信号在IP核内部那么在布局完成后使用下面的命令phys_opt_design -force_replication_on_nets [get_nets net_name]来保证IP核取消对内部网络的保护,能够正常复制高扇出网络。

图1.寄存器复制示意图

图2. flatten_hierarchy设置位置 max_fanout的使用形式 verilog综合属性设置:(*MAX_FANOUT = 50 *) reg test; 这里的综合属性必须设置在要降低扇出的寄存器前面,否则一定不会按照设计者意图综合。这种方法缺点是不能作用于IP核内部的某个信号。

max_fanout的参数意义 (*MAX_FANOUT = 50 *) reg test;里面的参数就只有一个——50,网络扇出超过50就会复制一个,保证每个复制的寄存器下面的扇出都不超过此参数。xdc约束也一样,不再赘述。 注意,图1的综合设置里面有-fanout_limit这个参数,并且默认是10000。这里是约束全局扇出的,但是max_fanout命令的优先级会高于这里的设置参数。所以编译器会优先按照你的综合属性或者XDC约束来进行优化。 3. BUFG 通常BUFG是用于全局时钟的资源,可以解决信号因为高扇出产生的问题。但是其一般用于时钟或者复位之类扇出超级大的信号,此类信号涉及的逻辑遍布整个芯片,而BUFG可以从全局的角度优化布线。而且一块FPGA芯片中BUFG资源也有限,在7k325tffg900上也仅有32个,如果用于普通信号的高扇出优化也不大现实。因此,在时钟上使用BUFG是必须的,但是如果设计中遇到某些复位信号因高扇出产生的时序问题时,可以在此信号上使用BUFG来优化。

微信公众号 建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,文章主要在公众号上发,csdn会尽量同步更新,有兴趣的朋友可以关注一下!

|

【本文地址】

今日新闻 |

推荐新闻 |