[FPGA/VerilogHDL/Xilinx]SerDes接口设计 |

您所在的位置:网站首页 › 增加总线带宽的方法有 › [FPGA/VerilogHDL/Xilinx]SerDes接口设计 |

[FPGA/VerilogHDL/Xilinx]SerDes接口设计

|

1. SerDes接口说明

1.1 SerDes接口内部硬件架构

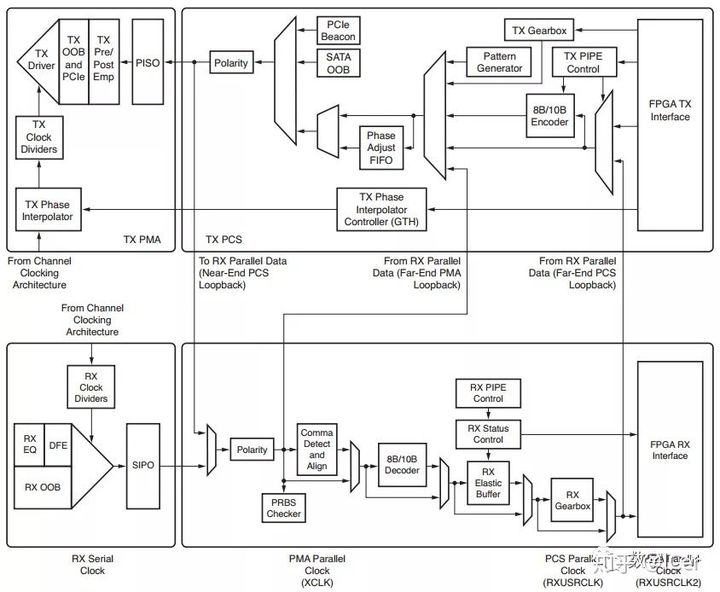

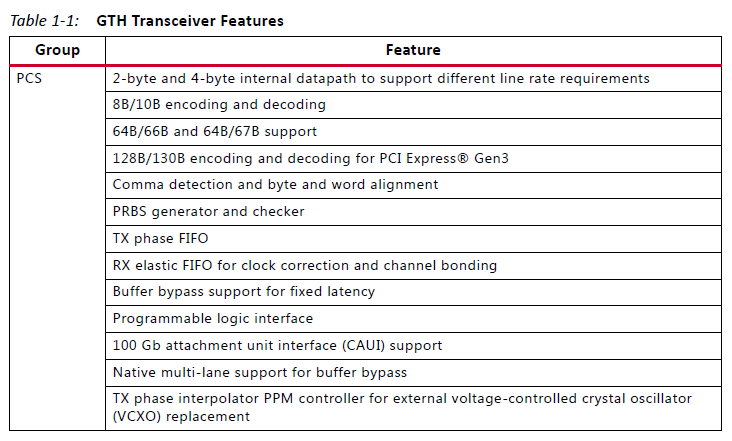

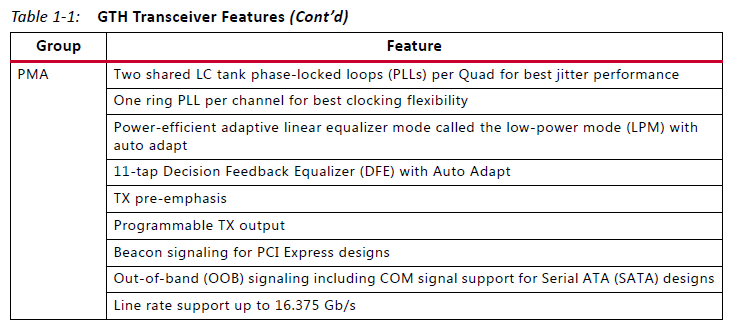

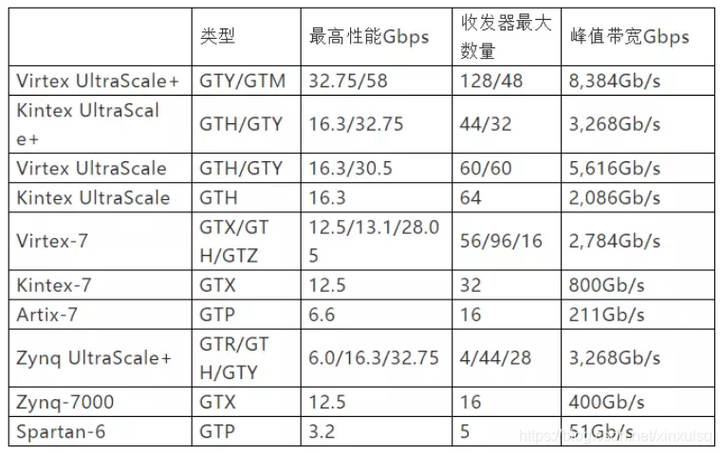

随着大数据的兴起以及信息技术的快速发展,数据传输对总线带宽的要求越来越高,并行传输技术的发展受到了时序同步困难、信号偏移严重,抗干扰能力弱以及设计复杂度高等一系列问题的阻碍。与并行传输技术相比,串行传输技术的引脚数量少、扩展能力强、采用点对点的连接方式,而且能提供比并行传输更高带宽,因此现已广泛用于嵌入式高速传输领域。 Xilinx公司的许多FPGA已经内置了一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做SerDes(Multi-Gigabit Serializer/Deserializer)。MGT收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路,为各种高速串行数据传输协议提供了物理层基础。MGT收发器的TX发送端和RX接收端功能独立,而且均由物理媒介适配层(Physical Media Attachment,PMA)和物理编码子层(Physical Coding Sublayer,PCS)两个子层组成,结构如下图所示。

基于PMA与PCS的SerDes电路结构 PMA子层内部集成了高速串并转换电路,预加重电路、接收均衡电路、时钟发生电路和时钟恢复电路。串并转换电路的作用是把FPGA内部的并行数据转化为MGT接口的串行数据。预加重电路是对物理连接系统中的高频部分进行补偿,在发送端增加一个高通滤波器来放大信号中的高频分量进而提高信号质量,但预加重电路会导致功耗和电磁兼容增加,所以如非必要一般情况下都把它屏蔽掉。接收均衡电路主要用来补偿由频率不同引起的阻抗差异。时钟发生电路与时钟恢复电路在发送端把时钟和数据绑定后发送,在接收端再从接收到的数据流中恢复出时钟,这样可以有效地避免在高速串行传输的条件下时钟与数据分开传输带来的时钟抖动问题。 PCS子层内部集成了8B/10B编/解码电路、弹性缓冲电路、通道绑定电路和时钟修正电路。8B/10B编/解码电路可以有效的避免数据流中出现连续的‘0’或者‘1’,以保证数据传输的平衡性。通道绑定电路的作用是通过在发送数据流中加入K码字符,把多个物理上独立的MGT通道绑定成一个时序逻辑上同步的并行通道进而提高传输的吞吐率。弹性缓冲电路用来解决恢复的时钟与本地时钟不一致的问题并可以通过对缓冲区中的K码进行匹配对齐来实现通道绑定功能。 1.2 SerDes接口关键技术简化的SerDes结构图如下图所示。

简化的SerDes结构 SerDes的优势在于其带宽很高,引脚数目较少而且支持目前多种主流的工业标准,比如Serial RapidIO ,FiberChannel(FC),PCI-Express(PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-Gb Ethernet(XAUI),Infiniband 1X,4X,12X等。它的线速度能达到10Gb/s甚至更高。 1.2.1 物理结构发送端和接收端功能独立,均由PMA(Physical Media Attachment,物理媒介适配层)和PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中PMA子层包含高速串并转换(SerDes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。

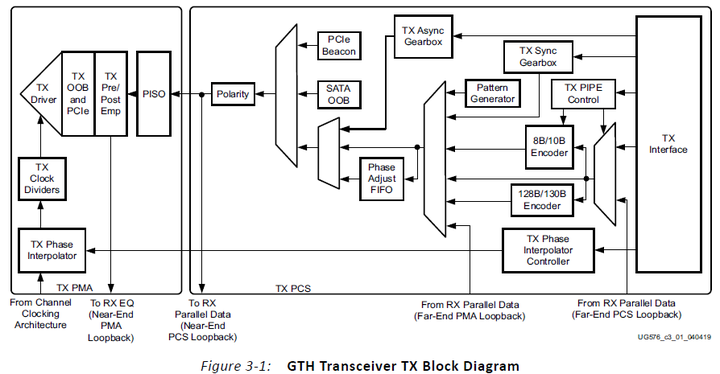

GTX发送端处理流程:首先用户逻辑数据经过8B/10B编码后,进入一个发送缓存区,该缓冲区主要是PMA子层和PCS子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速SerDes进行并串转换,有必要的话,可以进行预加重、后加重。值得一提的是,如果在PCB设计时不慎将TXP和TXN差分引脚交叉连接,则可以通过极性控制来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是RX接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。

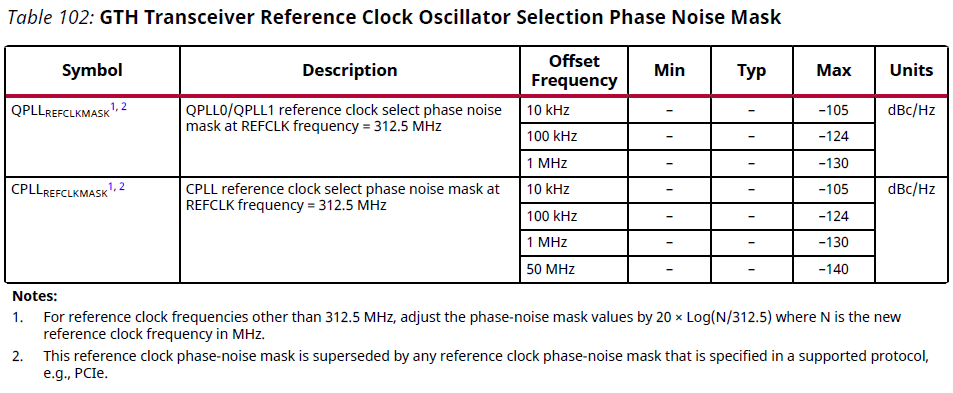

时钟选择是整个GTX使用的重点,通常调试出现问题很多原因都是出现在时钟方面。CPLL通常用于低速率传输通常在3.125G以下,QPLL通常用于高速率传输,QPLL的时钟更加精确,原则是能用QPLL就不用CPLL。如果用户需要使用其他Quad的参考时钟源来作为当前Quad的参考时钟,在满足下面三个条件的情况下可以使用: 只能使用当前Quad上方的Quad的参考时钟; 只能使用当前Quad下方的Quad的参考时钟; 一个Quad的参考时钟源不能驱动超过3个Quad的收发器(只能驱动当前Quad和上下方相邻两个Quad)

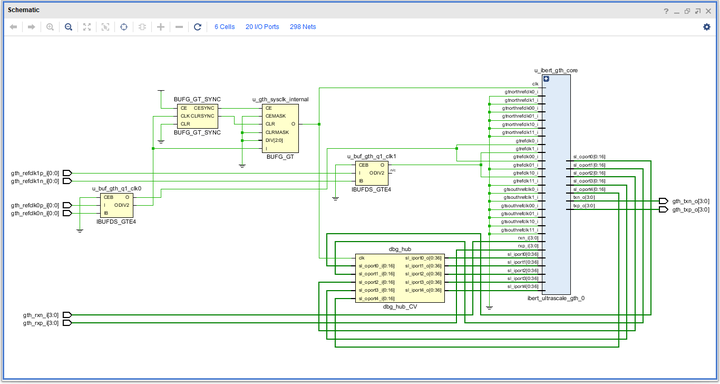

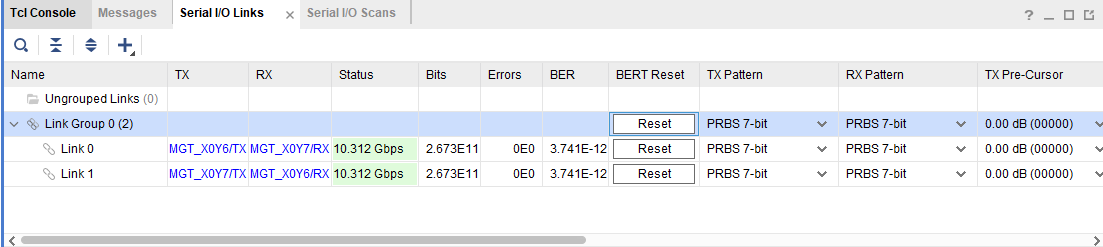

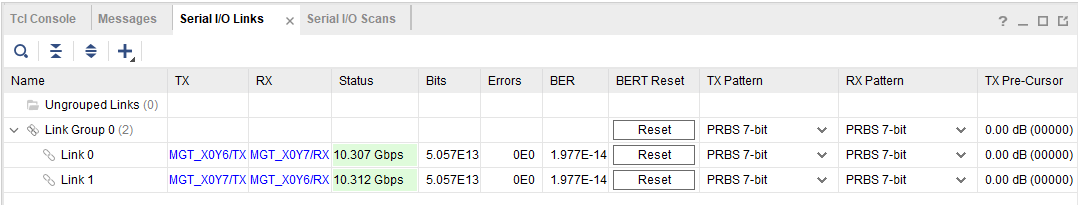

基于IBERT的GTH验证方法原理 Vivado中提供了1种IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT我们可以获取误码率,观察眼图,调节串行收发器的参数,从而有助于判断可能存在的问题,便于验证硬件的稳定性和信号完整性。IBERT中的BERT是Bit Error Ratio Test的缩写,指比特出错概率测试,简而言之就是误码率测试。Vivado中IBERT工具的测试原理是通过收发器由外部回环进行自收自发而实现。就是将同一组收发器的TX和RX进行短接,TX发送端通过发送某种特定序列的数据流,在RX接收端接收后,通过比对发送和接收的数据,从而得出接收端误码的统计值 。 在开发板中,将光模块插入SFP屏蔽笼内,然后通过单根光纤将光模块的TX和RX短接,便可以通过IBERT工具对GTX进行测试。 验证结果

速率与丢包率验证:10.312Gbps(受限于SFP+接口,2.67*10^11bit丢包率为0)

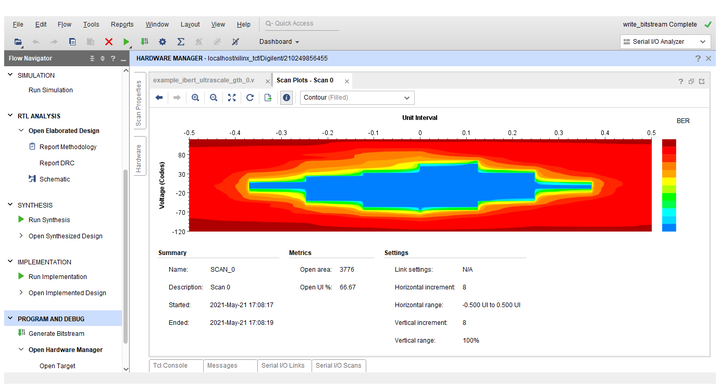

2D眼图:我们可以通过修改收发器串行I/O参数,优化连接链路信号质量(眼图张开大小),从信号完整性角度来看,眼图中间蓝色区域越大,表明PCB板信号完整性越好。

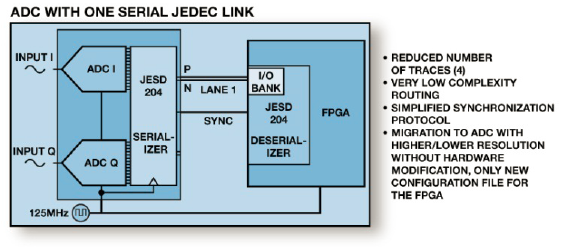

眼图说明:眼图扫描的过程就是依次遍历眼图的二位矩阵区域,并和眼图扫描的正中间区域做对比,记录错误值,然后依据错误值,用不同的颜色来绘制当前二位矩阵中某个点,最终组成一个眼图。用更通俗的话来解释,就是眼图被划分为一个分辨率是N*M的图片。测量眼图的时候会依次遍历N*M个点,并和中心点的数据做对比。多次对比后记录值不一样的次数,即误码率。当遍历完N*M个点之后,依据每个点记录的误码率来用不同的颜色绘制一副图,即为眼图。从上图的左边可以看到,每一个点相对中心点都有一个水平偏移量和垂直偏移量,这就等价于每个点的坐标值(至于0,0点在左下角还是在中心点都只是简单的坐标变换而已)。从图中的右边可以看到,最终眼图的颜色是依据误码率绘制的,结合前文来自UG908的截图,可以清楚的看到当误码率越低,颜色越偏向蓝色(深蓝色);当误码率越高,颜色越偏向红色。理论上,越接近中心的点,误码率越低,所以越偏蓝色,而越接近外围的点,误码率越高,所以越偏红色。所以实际获取的眼图样子,是中心蓝色,四周红色的眼图。所以从原理上说,2D眼图的测量步骤其实是遍历整个N*M的点阵,计算每一个点与中心点数据值的误码率。当得到点阵误码率的数据之后,后面仅仅是绘图以便美观显示的事情。具体的测量细节可以参考UG476的第四章。这里直接给出结论,内置的2D eye scan是逐个点进行测量的,所以每次测量只需一组坐标值。从微观看来,逐点测量由于是串行的,所以是比较慢的。但是从宏观来看,整体测量速度是比较快速的。另外一个优点就是,眼图的测量不需要特殊的配置和数据,也不会对数据链路带来任何负面影响。由于是和中心点数据的对比,所以无论GT跑的是什么数据流,都可以进行测量,也没有影响。这就扩展了这一功能的使用范围。例如ibert的误码率只能统计PRBS,无法用于实际数据的统计/测试。而这一功能可以实时测试,不影响GT正常业务的运行。将这一功能集成到最终版本中,可以作为实时监控高速链路质量的一个参考标准。如果GT无法正确回复出数据,则中心点的数据不会稳定。这样统计出来的结果也不会稳定的显示为一个眼睛的图案,而是一个奇怪的图案。如果GT能正确恢复出数据,那么中心点一定是稳定的数据,所以无论眼图是否睁开,张开多大,大体的形状还是一个眼睛的图案。进而,眼图张开的大小就代表信号质量的好坏。所以2D eye scan的结果可以用于评价链路信号质量。 2.2 基于SerDes的JESD204B实现 2.2.1 JESD204B接口接口说明:JEDEC Standard No. 204B (JESD204B)—A standardized serial interface between data converters (ADCs and DACs) and logic devices (FPGAs or ASICs),也就是说这是一个高速模数信号转换芯片与逻辑器件芯片之间的标准接口。

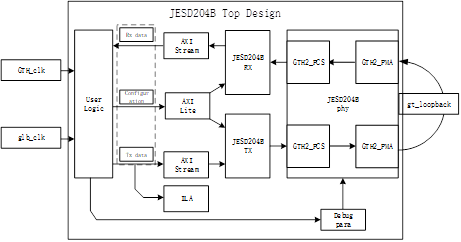

优点:具有所有高速串行接口的优点(减小芯片封装大小、引脚数量;减小电路板PCB面积;功率一定时提供更大的吞吐量。);

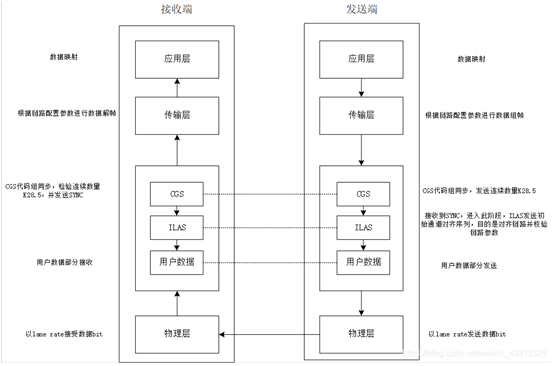

速度:对于ZU4EV一般速度等级的芯片来说,每个Lane/通道可以达到12.5 Gbps(12.5 * 10 ^ 9 bits per second = 12.5 * 10 ^ 8 Bytes per second(8b/10b编码) ~= 1192.0929 MBytes per second(除以1024 ^ 2))。 子类:JESD204B接口共有三个子类:Subclass 0 Subclass 1 Subclass 2(常见Subclass 1,不同子类的区别主要跟信号SYSREF和SYNC~的有无有关): Subclass 0 uses device clock, lanes, and SYNC~(子类0只有SYNC~信号); Subclass 1 uses device clock, lanes, SYNC~, and SYSREF(子类1有SYNC~和SYSREF信号); Subclass 2 uses device clock, lanes, and SYNC~(子类2只有SYNC~信号)。 2.2.2 设计验证方案 基于AXI-Lite总线进行寄存器访问和配置,分别将JESD204B的TX-core和RX-Core启动、加载、配置为预期的工作模式与参数;基于AXI-Lite总线进行寄存器访问和轮询,根据AXI-Lite总线返回的寄存器值,判断其是否处于有效工作状态; 基于JESD204B提供的Debug接口,将其配置为预期的工作模式,本次设计中为Near-PMA-loopback模式; 使用用户逻辑搭建JESD204B的应用层与传输层,根据JESD204B接口标准创建CGS阶段数据流、ILA阶段数据流、以及数据传输阶段具备一定特征的用户数据; 在顶层文件中,例化上述各个模块,如下图所示,完成相关接口的连接关系,并使用ILA分别监测AXI总线的传输情况、经JESD204B-phy处理前后的数据对比情况、以及关键信号比如SYNC、TX_READY等信号的变化情况。

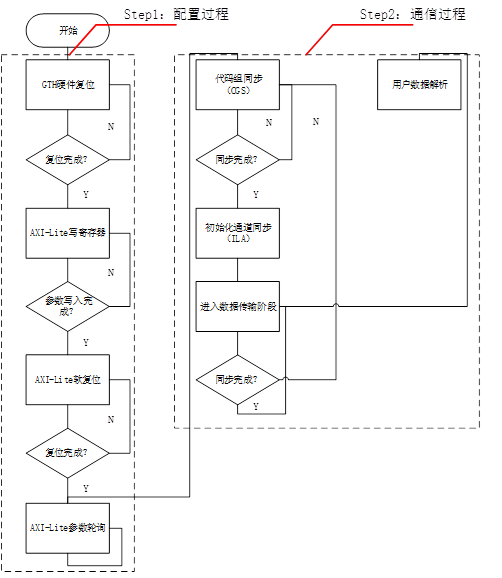

JESD204B验证方案

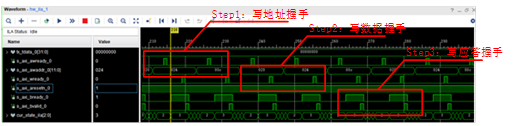

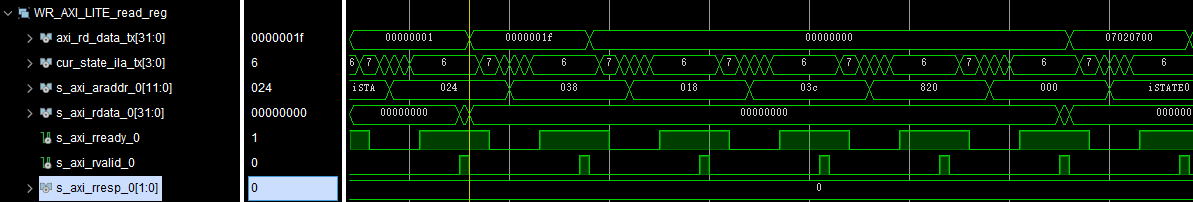

JESD204B驱动程序工作流程图 JESD204B IP关键寄存器说明:全部说明详见PG066-JESD204B与PG198-JESD204B-phy AXI-Lite地址 寄存器说明 R/W Value 0X00 Version JESD-IP版本号说明 RO 32’h07020700 0X04 软复位操作寄存器 R/W 复位:32'h0001_0003释放:32'h0001_0000 0X08 ILA配置寄存器 R/W 失效:32'h0000_0000 0X18 GTH测试模式配置寄存器 R/W 正常工作模式:32'h 0000_0000 0X20 JESD204B-F参数 R/W 32'h 0000_0003 0X24 JESD204B-K参数 R/W 32'h 0000_001f 0X28 LANES通道配置寄存器 R/W 使用LANE2:32'h0000_0004 0X2C JESD子类配置寄存器 R/W 使用子类0:32'h 0000_0000 0X38 同步状态 RO 完成同步:32'h 0000_0001 0X3C 通道调试状态 RO 详见PG066 0X820 测试模式下的错误统计 RO 详见PG066 AXI-LITE交互过程: ZU系列的AXI-Lite总线时钟最高频率为200Mhz,设计中采用100Mhz,与Drp时钟同源。需要注意的是,AXI-Lite回复的有效信号与有效数据只持续1个时钟周期,因此对以上两个信号进行处理时,不要做缓存和延时处理。 配置过程

轮询过程

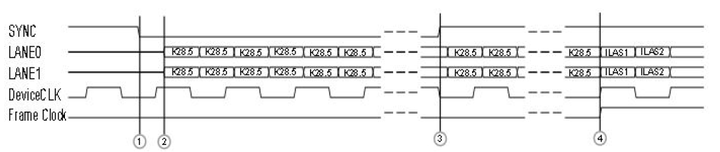

具体交互过程细节详见JESD204B-Survival-Guide。 2.2.4.1 代码组同步(CGS) 1. 接收端拉低SYNC等待同步; 2. 发送端发送连续的K码(K28.5)至接收端; 3. 接收端接收到连续无误的至少4组K码后,将SYNC拉高; 4. 接收端需要接收连续无误的至少四种8B/10B编码的特征值后,进入ILA阶段,否则将停滞在CGS阶段。

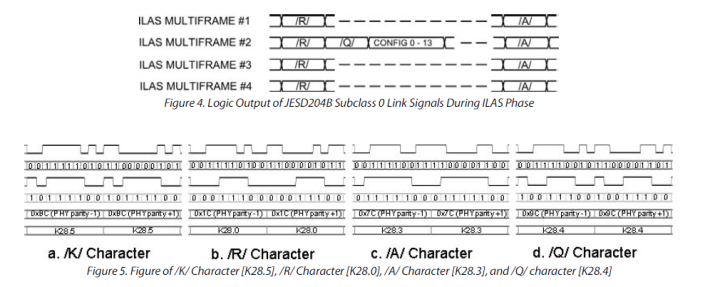

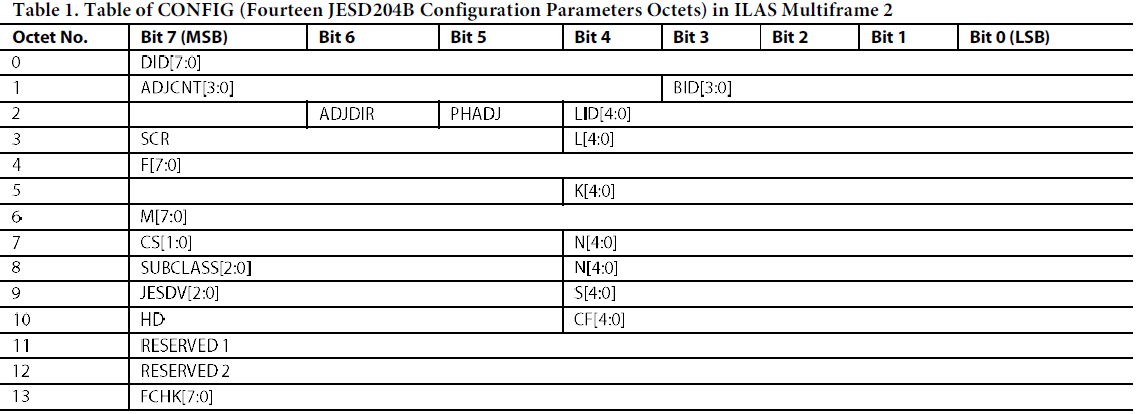

2.2.4.2 初始化通道同步(ILA) 1. Multiframe1:以R码(K28.0)为起始,以A码(K28.3)为终止; 2. Multiframe2:以R码(K28.0)为起始,而后发送Q码(K28.4),而后发送链接配置参数,以A码(K28.3)为终止; 3. Multiframe3:同Multiframe1; 4. Multiframe4:同Multiframe1;

8B/10B特征码说明

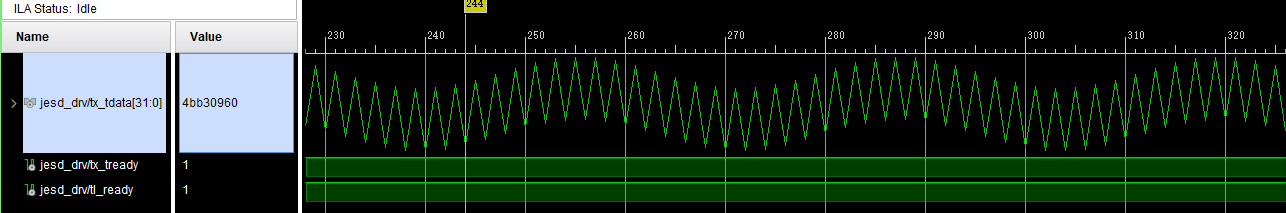

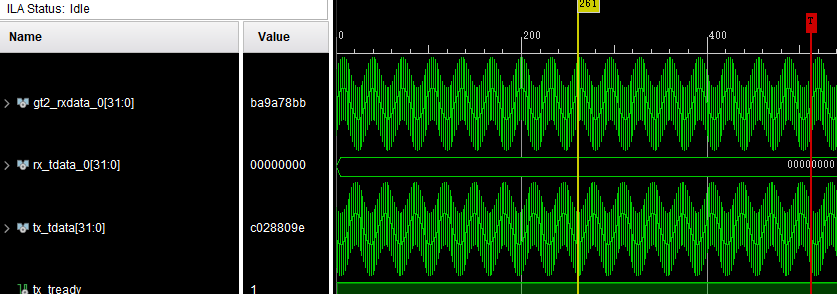

链接配置参数说明 2.2.4.3 数据传输阶段(Data Transmission) 模拟了两组不同频率的正弦信号叠加后的波形,离散后作为数据发送的依据。

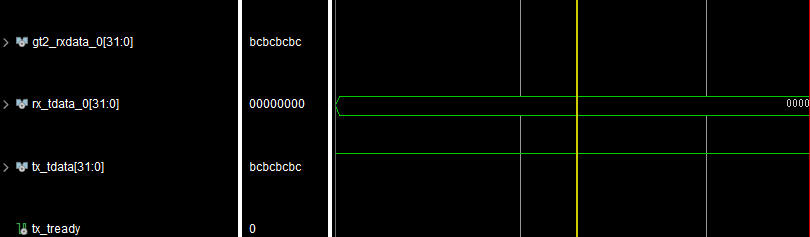

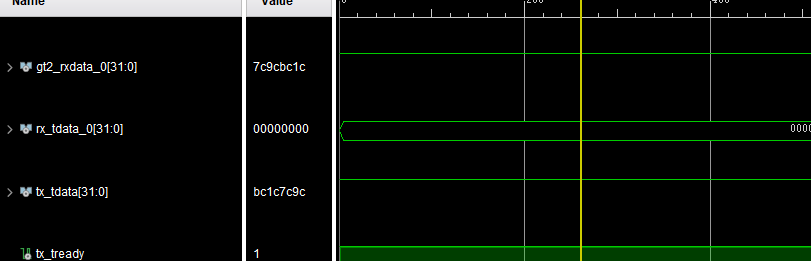

2.2.4.4 模拟ADC的数据发送和接收过程 代码组同步过程实现

初始化通道同步过程实现

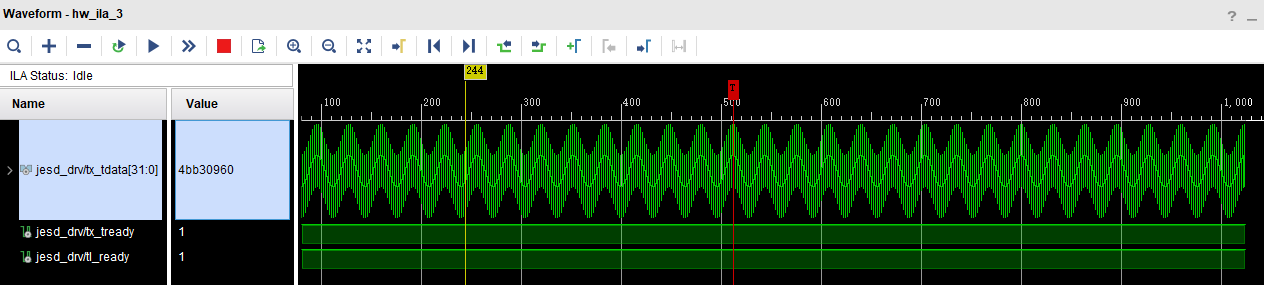

数据传输阶段实现

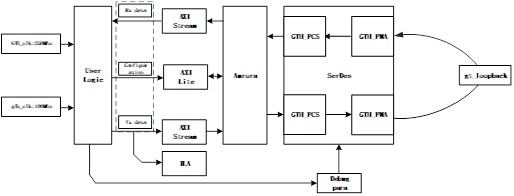

Aurora是Xilinx®为高速串行通信(千兆级别)开发的轻量级,点对点链路层协议,广泛应用于需要背板、电路板间和芯片间连接的应用。细分市场包括有线通信、存储、服务器、测试测量、工业、消费和医疗等。此外,Aurora 也可用作嵌入式处理器应用中的调试端口。具有逻辑资源使用少、数据传输延时低、带宽高、可配置的特点,其优势包括: 高带宽,仅受限于收发器的数据速率; 支持大量键合线路,实现较高的总带宽; 支持全双工和单工通道; 无限帧尺寸/灵活组帧; 小型逻辑封装,采用标准的 AXI-ST 接口; 内置流程控制和热插拔支持。 2.3.2 设计验证方案基于AXI-Lite总线进行寄存器访问和配置,分别对Aurora IP的工作模式与参数进行配置;基于AXI-Lite总线进行寄存器访问和轮询,根据AXI-Lite总线返回的寄存器值,判断其是否处于有效工作状态; 基于JESD204B提供的Debug接口,将其配置为预期的工作模式,本次设计中为Near-PMA-loopback模式; 在顶层文件中,例化上述各个模块,如下图所示,完成相关接口的连接关系,并使用ILA分别监测AXI总线的传输情况、经Aurora IP处理前后的数据对比情况、以及关键信号比如CORE_CONTROL、CORE_STATUS等信号的变化情况。

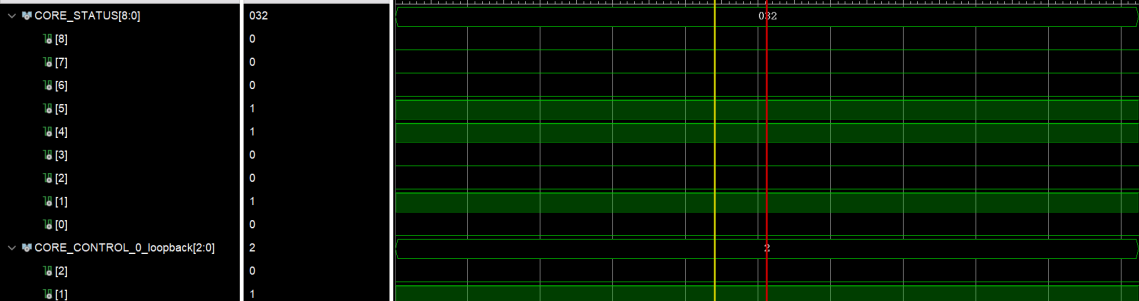

Aurora IP工作状态

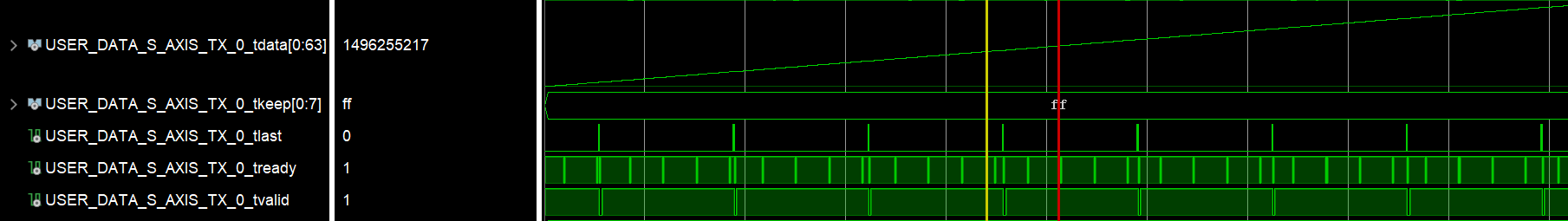

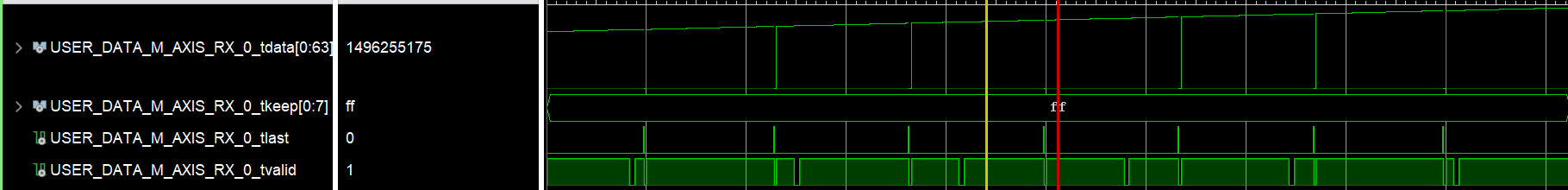

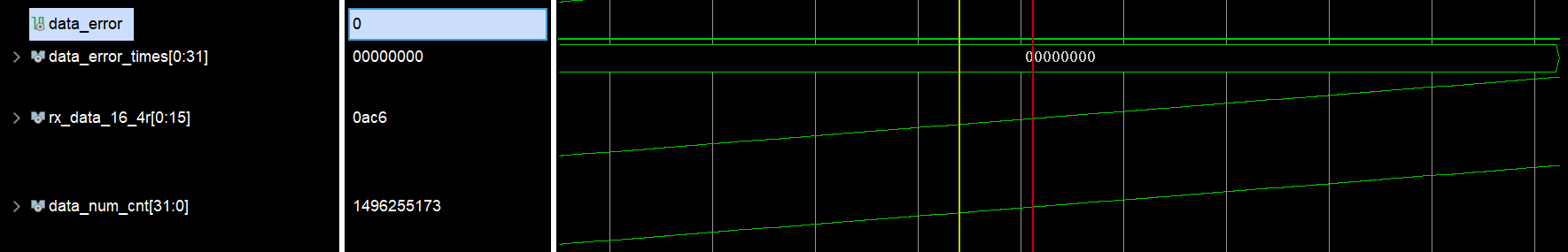

数据收发情况比对结果

数据发送过程

数据接收过程

数据解析结果 |

【本文地址】

今日新闻 |

推荐新闻 |