Nature:“升维打击” |

您所在的位置:网站首页 › 在硅片上可制作出成百上千的集成电路 › Nature:“升维打击” |

Nature:“升维打击”

|

Nature:“升维打击”—2D晶体管的3D集成

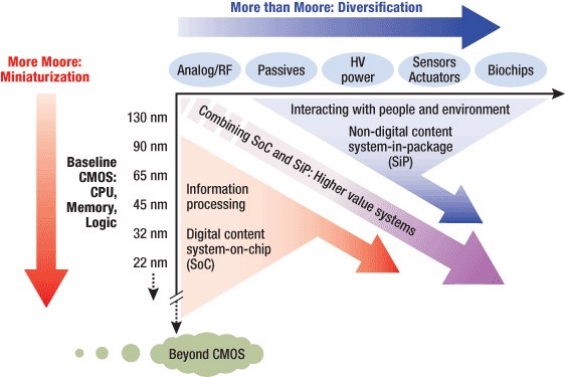

传统的芯片制造技术,绝大多数都是将大量晶体管集成在二维(2D)平面上。随着单位面积中的硅基晶体管数量接近制造极限,延续了近50年的“摩尔定律”正在失效,半导体领域即将进入“后摩尔时代”。科学家们更新了芯片发展技术路线图,一方面想办法延续摩尔定律(More Moore),另一方面通过器件的功能多样化,试图超越摩尔定律(More than Moore)。近年来,三维(3D)集成被广泛关注,不但可以提高单位面积的晶体管数量,通往“More Moore”,还可以利用每层器件的多功能化,实现“More than Moore”(点击阅读相关)。

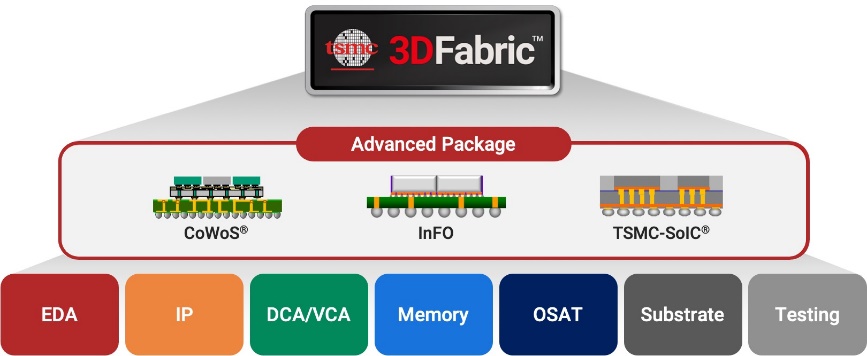

“More Moore”和“More than Moore”。图片来源于网络 [1] 鉴于3D集成令人关注的潜能,一些著名的芯片制造公司,如台积电、英特尔和AMD,都投入到3D集成及封装技术的研发工作,硅基3D集成电路正在走向商业化。新兴纳米材料,如具有原子级厚度及优异载流子迁移率的2D材料,更有助于3D集成电路的开发。然而,3D集成目前还存在大量问题,比如,硅基组件的处理温度限制约为450 °C,这限制了单片集成的发展。

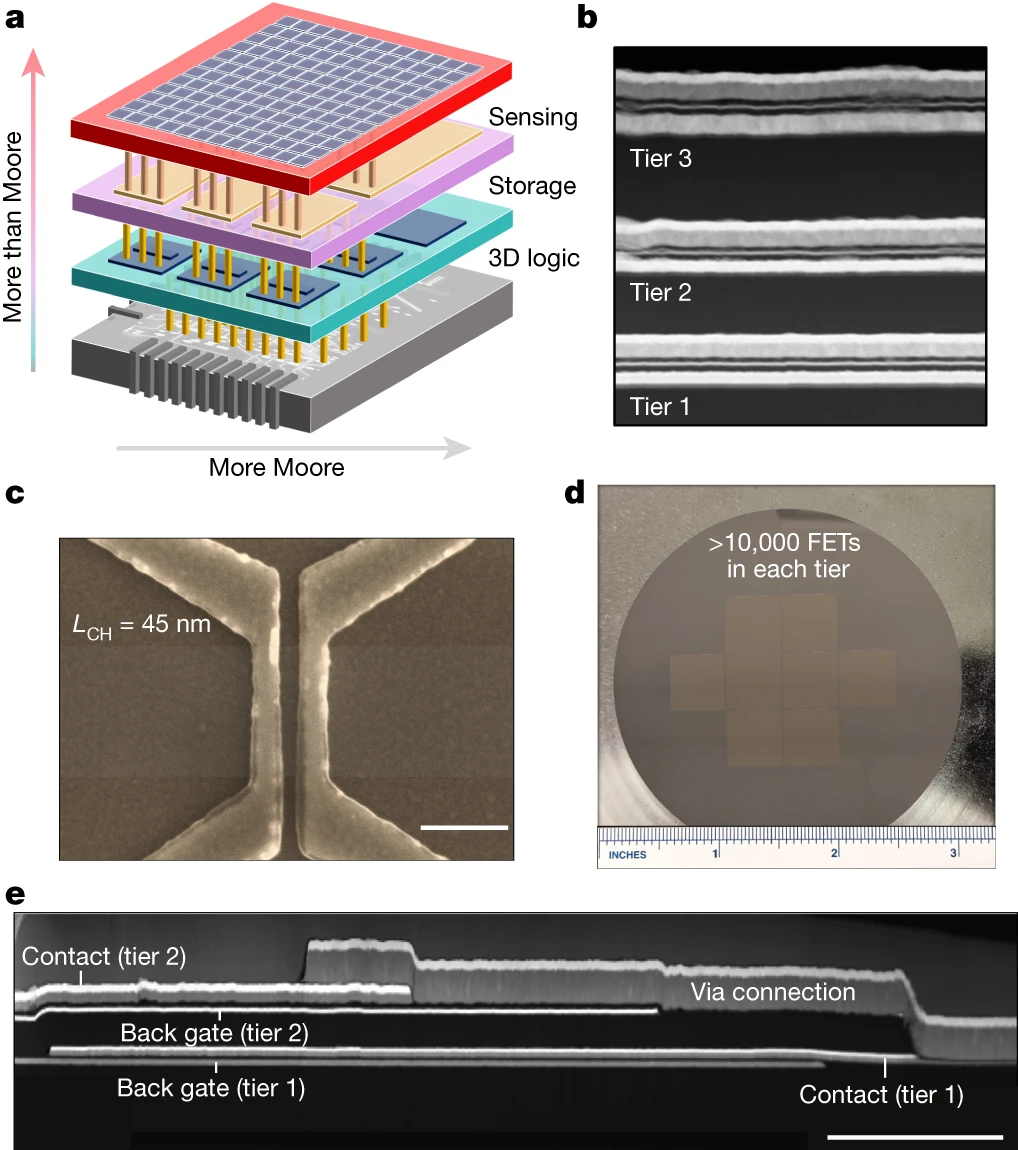

台积电推出的3DFabric。图片来源:台积电 [2] 近日,宾夕法尼亚州立大学Saptarshi Das课题组在Nature 杂志上发表论文,基于大面积生长的2D材料MoS2和WSe2,实现了场效应晶体管(FET)的3D集成。他们进行了:(1)基于MoS2的晶圆级单片双层3D集成,每层可超过10,000个FET器件;(2)基于MoS2和WSe2的三层3D集成,每层约500个FET器件;(3)基于沟道长度可至45 nm的MoS2 FET的双层3D集成,每层约200个FET器件。他们还证明了基于MoS2的3D电路的可行性,并演示了多种功能,包括传感和存储。这一工作将成为更复杂、更高密度和功能更多样的3D集成电路的基础。

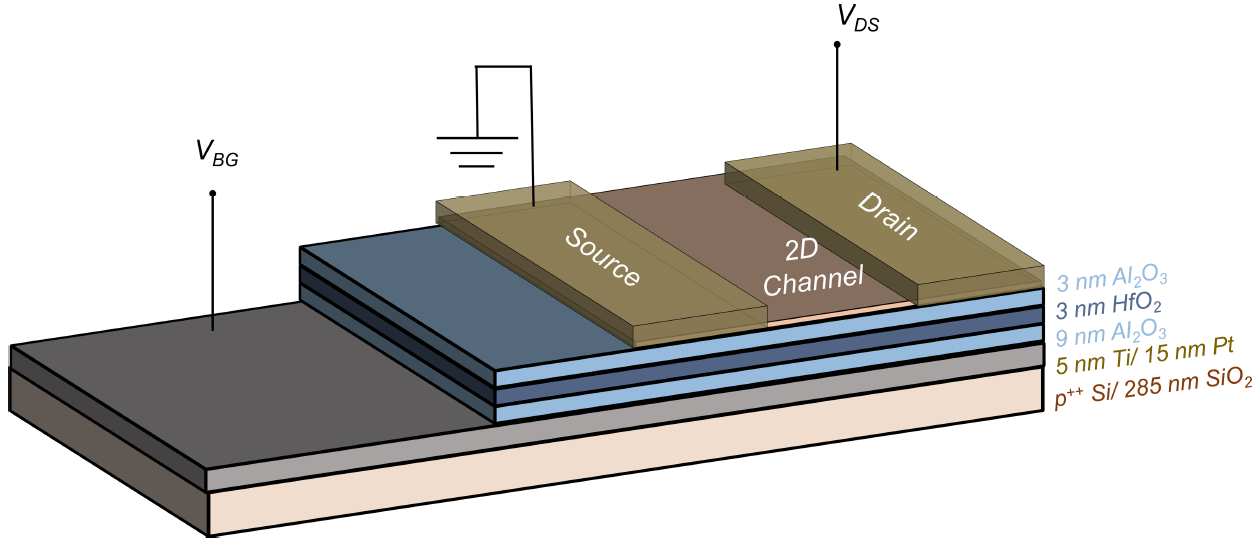

2D FET的单片式3D集成。图片来源:Nature 2D材料MoS2和WSe2通过化学气相沉积法生长,以20-nm Ni/10-nm Au或20-nm Pd/10-nm Au作为源漏极,5-nm Ti/15-nm Pt作为栅极,9-nmAl2O3/3-nmHfO2/3-nm Al2O3作为介电层,制备了2D FET器件。

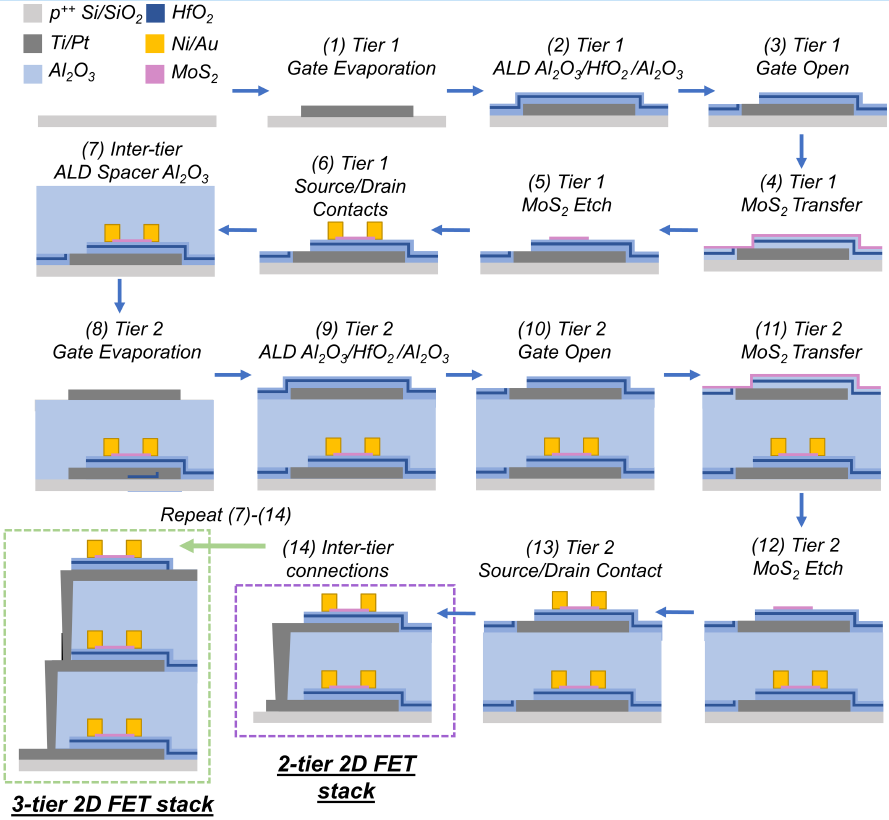

2D FET器件示意图。图片来源:Nature 每“层”器件的制备流程包含7个主要步骤,层与层之间利用Al2O3隔离和封装。整个制作过程在180 °C内完成,使得可以在不降低底层器件性能的情况下实现多层集成。

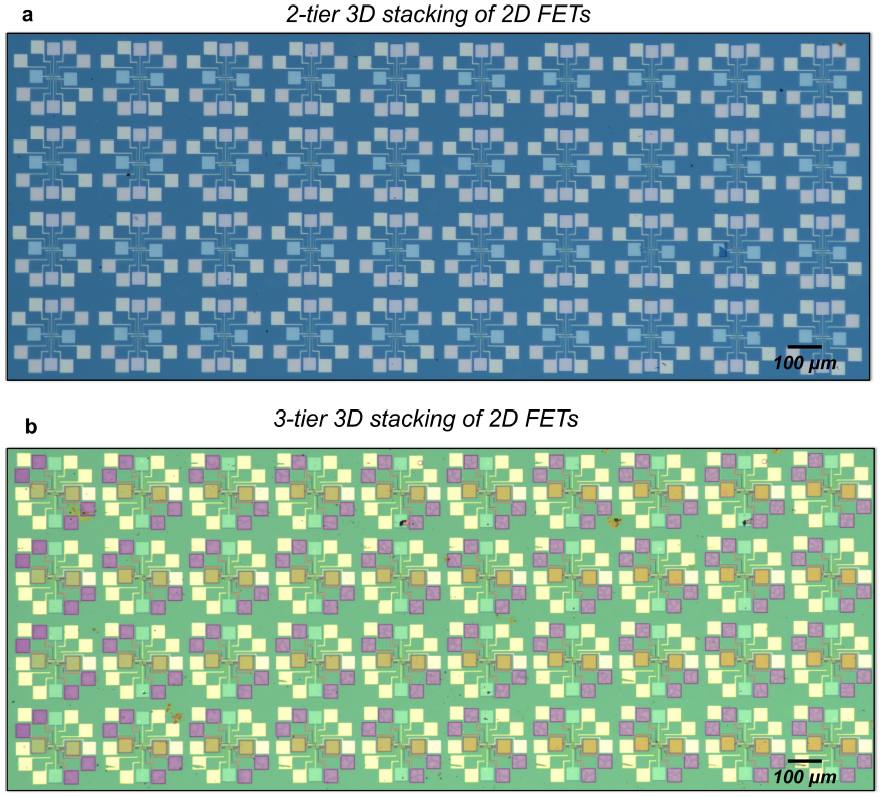

2D晶体管的3D集成制备流程。图片来源:Nature 加工过程在硅片上完成,硅片仅作为衬底支撑使用,也可以选择其他非导电衬底。一层和二层中的器件垂直堆叠,第二层中每个单元包含4个晶体管,第三层中每个单元包含5个晶体管,层与层之间通过孔相连。

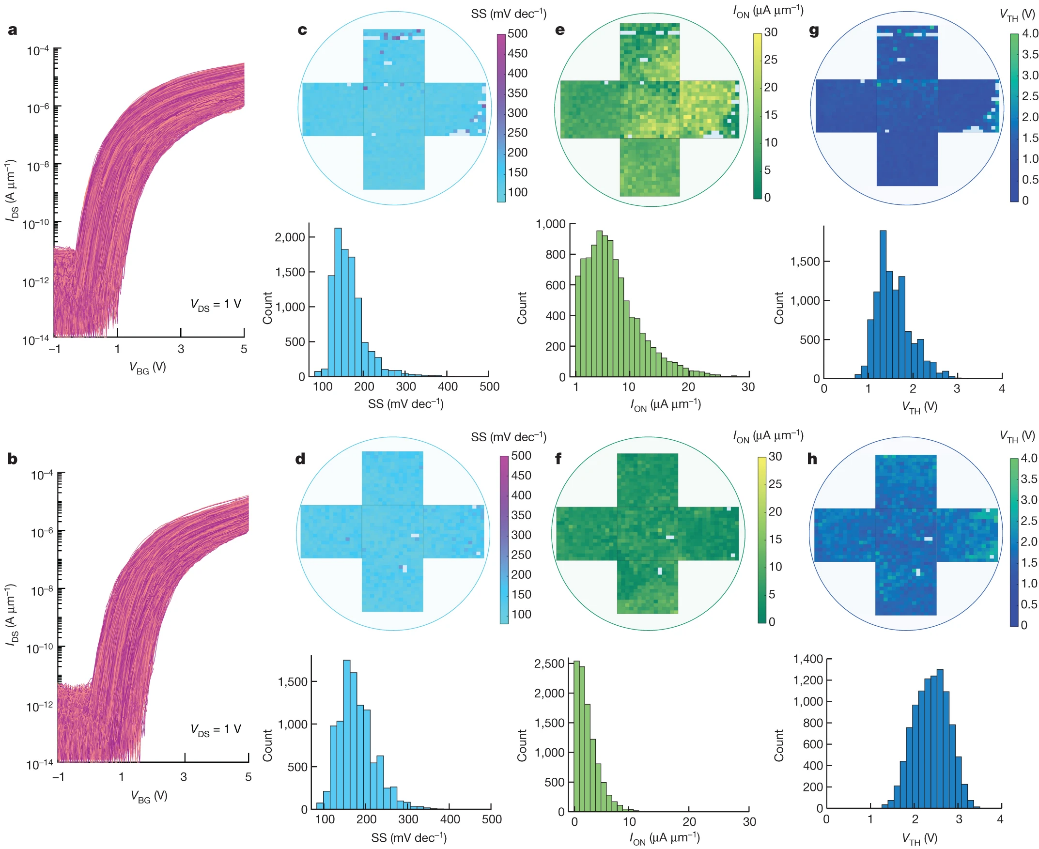

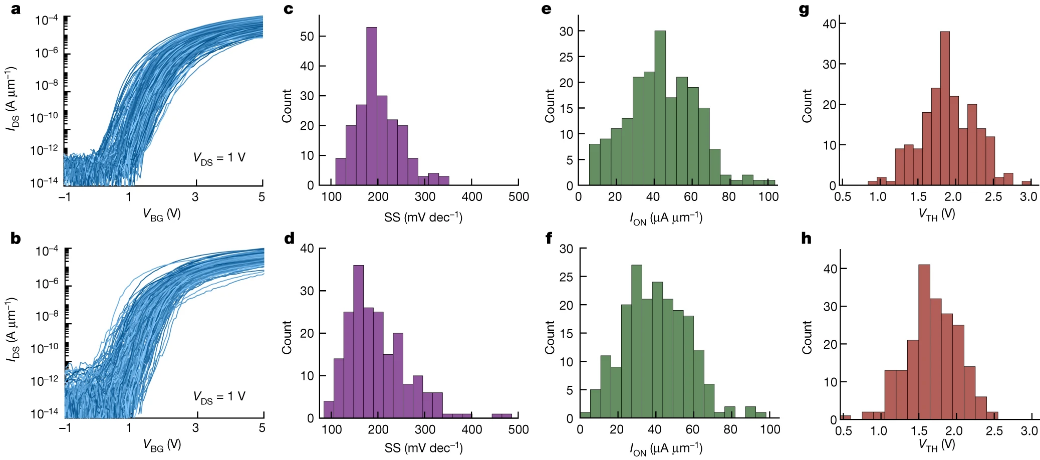

二层和三层的显微照片。图片来源:Nature 研究者首先对集成了两层的MoS2晶体管进行电性能测试,每层10,000个器件,沟道长度300 nm。层1和层2的亚阈值斜率(SS)的中值分别为156 mV/dec和170 mV/dec,最小值79 mV/dec和85 mV/dec,接近60 mV/dec的理想值,标准偏差分别为40 mV/dec和44 mV/dec。此外,层1和层2的开态电流(ION)的中值分别为6.5 μA μm-1和2.7 μA μm-1,标准偏差4.4 μA μm-1和2.0 μA μm-1;阈值电压的中值分别为2.7 V和1.6 V,标准偏差1.4 V和1.2V。

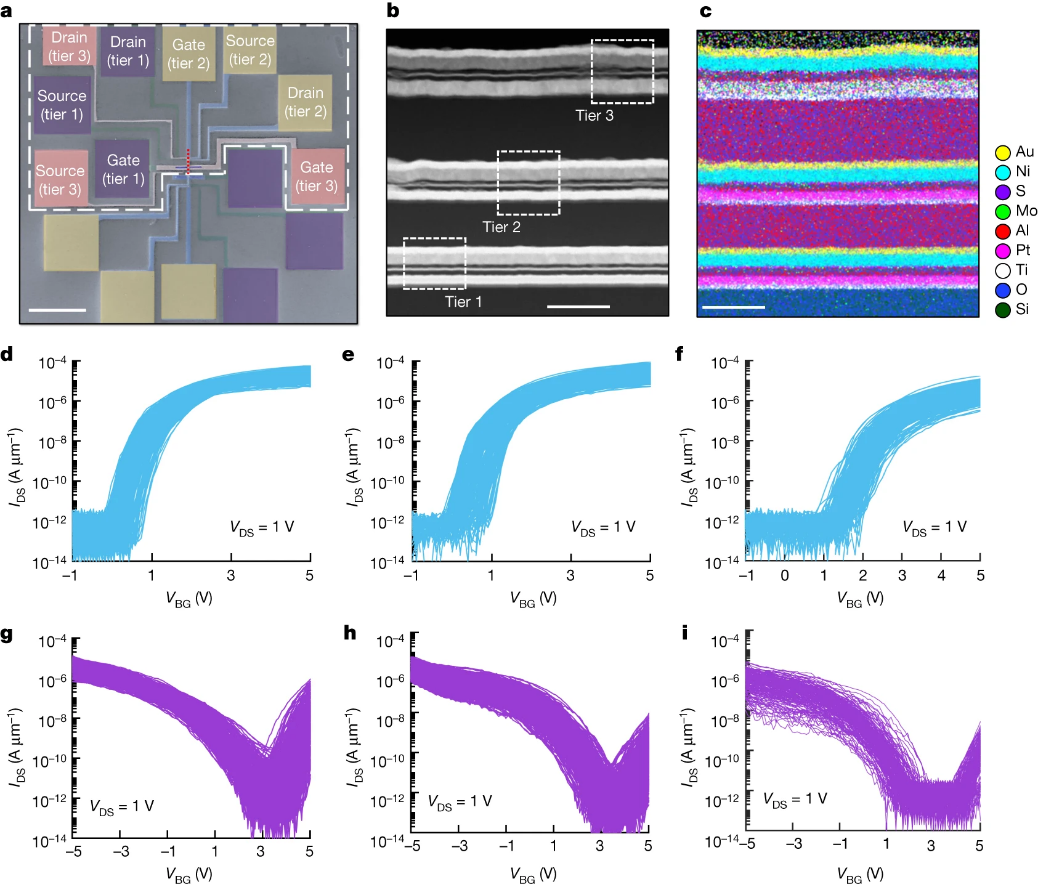

2D FET电学性能。图片来源:Nature 为了证明多层集成的可行性,研究者集成了三层MoS2和WSe2,层1和层2分别有800个器件,层3有450个器件,电镜分析显示每层都完好无损。三层MoS2晶体管均表现出典型的n型传输曲线,层1和层2晶体管的亚阈值斜率的中值为125 mV/dec,层3则为180 mV/dec,这可能是因为层3中2D半导体膜所受应变略有不同。三层WSe2表现出p型主导的双极传输曲线,亚阈值斜率的中值约450 mV/dec,这归因于MoS2的生长质量比WSe2更好,硫空位较少。

三层3D集成。图片来源:Nature 随后,研究者进一步优化光刻条件,将晶体管沟道长度降低至45 nm,并集成了两层MoS2。层1和层2亚阈值斜率的中值分别为200 mV/dec和180 mV/dec,标准偏差约90 mV/dec和70 mV/dec。此外,沟道长度从300 nm降至45 nm,开态电流只增加了约两倍,这主要是源漏电极与MoS2接触电阻的影响,以及阈值电压偏高(~1.9 V)所导致。

45 nm沟道晶体管的两层集成。图片来源:Nature 最后,研究者展示了将二层MoS2集成应用于逻辑电路的潜在可能性,并成功实现了反相器、非易失性存储以及光感应等功能,为未来进一步实现2D材料的3D集成研究提供了方向。

多功能二层MoS2集成应用。图片来源:Nature “我们的集成方法将工艺温度降至200 °C以下,可以与硅芯片工艺兼容”,论文一作Darsith Jayachandran说。“单片3D集成为高密度垂直连接提供了可能”,论文作者Najam Sakib强调。“通过将设备垂直堆叠在一起,可以缩短设备之间的距离,从而减少延迟和功耗”,论文共同一作Rahul Pendurthi补充说。“我们展示了在晶圆级别上集成多层器件的能力,每层排列上万个晶体管,这可能是一个创纪录的数字,并进一步推进半导体行业的合作和发展”,Saptarshi Das总结道 [3]。 原文(扫描或长按二维码,识别后直达原文页面,或点此查看原文):

Three-dimensional integration of two-dimensional field-effect transistors Darsith Jayachandran, Rahul Pendurthi, Muhtasim Ul Karim Sadaf, Najam U Sakib, Andrew Pannone, Chen Chen, Ying Han, Nicholas Trainor, Shalini Kumari, Thomas V. Mc Knight, Joan M. Redwing, Yang Yang & Saptarshi Das Nature 2024, 625, 276-281. DOI: 10.1038/s41586-023-06860-5 参考文献: [1] ITRS 2010: A More-than-Moore Roadmap? https://sst.semiconductor-digest.com/2011/01/itrs-2010__a_more-than-moore/ [2] TSMC 3DFabric™ Alliance https://www.tsmc.com/english/dedicatedFoundry/oip/3dfabric_alliance [3] Integrating dimensions to get more out of Moore’s Law and advance electronics https://www.psu.edu/news/materials-research-institute/story/integrating-dimensions-get-more-out-moores-law-and-advance/ (本文由小希供稿) 如果篇首注明了授权来源,任何转载需获得来源方的许可!如果篇首未特别注明出处,本文版权属于 X-MOL ( x-mol.com ), 未经许可,谢绝转载! 点击分享 收藏 取消收藏 评论: 0 |

【本文地址】

今日新闻 |

推荐新闻 |