从0开始,模拟集成电路设计Cadence Virtuoso学习笔记(三)反相器layout与后仿真 |

您所在的位置:网站首页 › 反相器制作流程图片 › 从0开始,模拟集成电路设计Cadence Virtuoso学习笔记(三)反相器layout与后仿真 |

从0开始,模拟集成电路设计Cadence Virtuoso学习笔记(三)反相器layout与后仿真

|

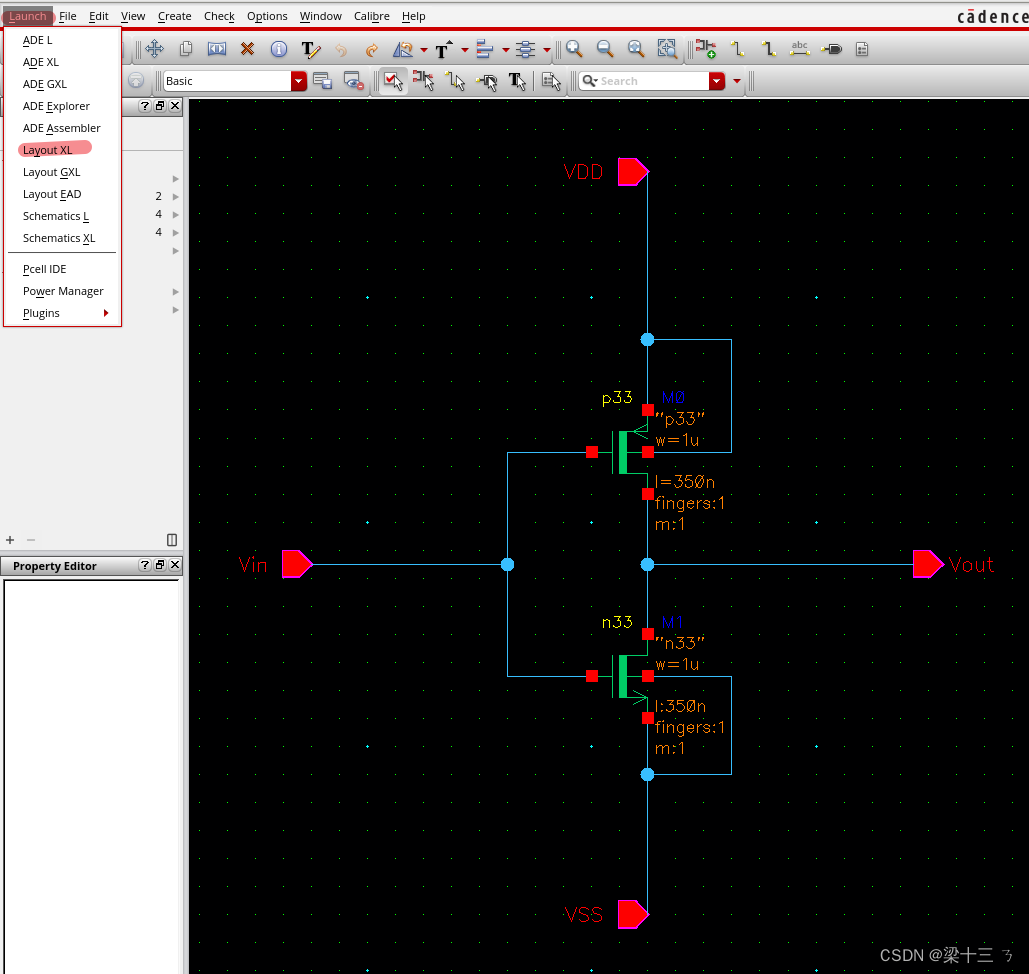

前言 一、版图绘制 1.打开绘制版图界面 2.导入器件 3.连线 二、仿真 1.DRC仿真 2. LVS仿真 总结 前言之前学习了原理图绘制与仿真,这一节进行版图layout绘制,之所以间隔比较久,主要是因为版图绘制内容比较多,在绘制仿真过程中出现了很多问题有的到现在都没有解决,这些问题和选择的器件库以及在原理图绘制时所设置的器件参数等都有关系,这几天抽空解决了一部分,但有的是因为凑巧,这里先对绘制和仿真的流程和注意事项介绍,后面针对具体问题解决后再补充说明。 一、版图绘制 1.打开绘制版图界面首先打开之前绘制的反相器原理图文件,点击launch>layout XL

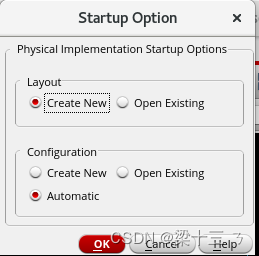

弹出窗口,按图中所示选择

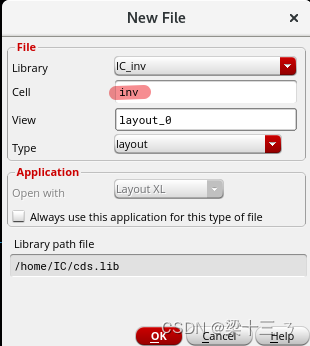

名字和原理图保持一致(这里是我重新画的原理图,之前的名字是test)

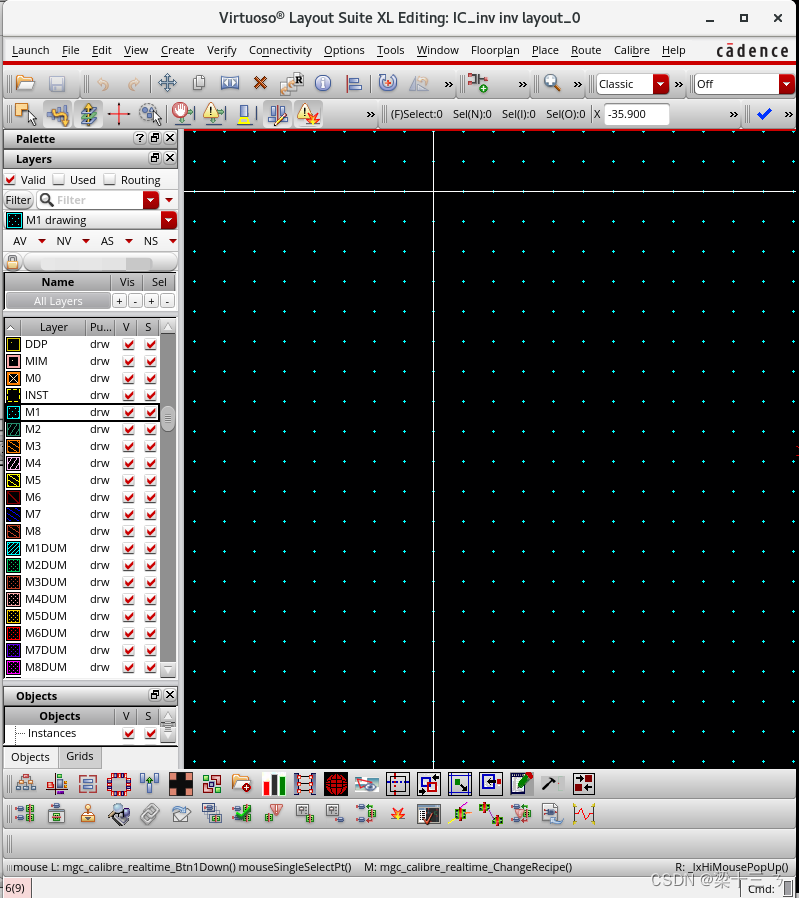

点击ok弹出layout绘制界面

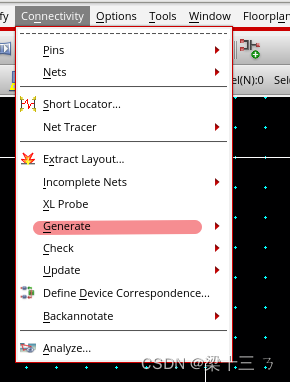

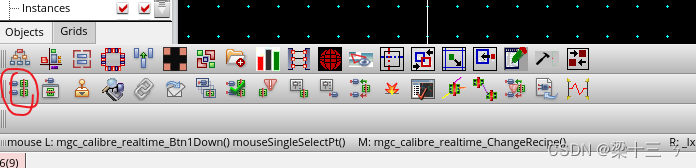

有两种方法,一种是点击这里面的generate>ALL from source 另一种是点击左下角图标

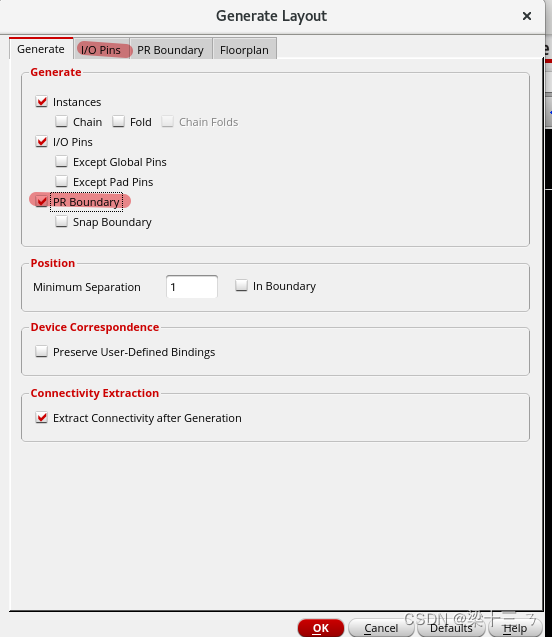

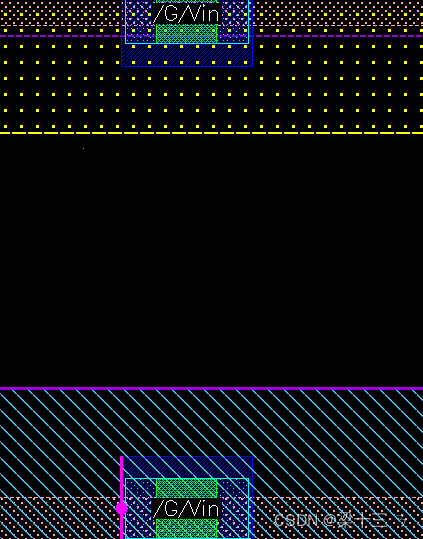

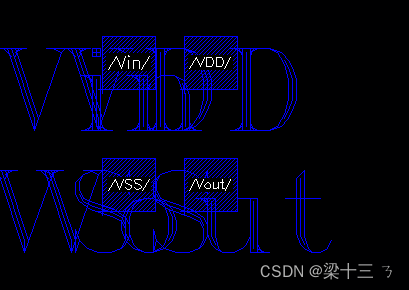

点击后弹出界面,这里取消掉PR Boundary 然后点击IO pin

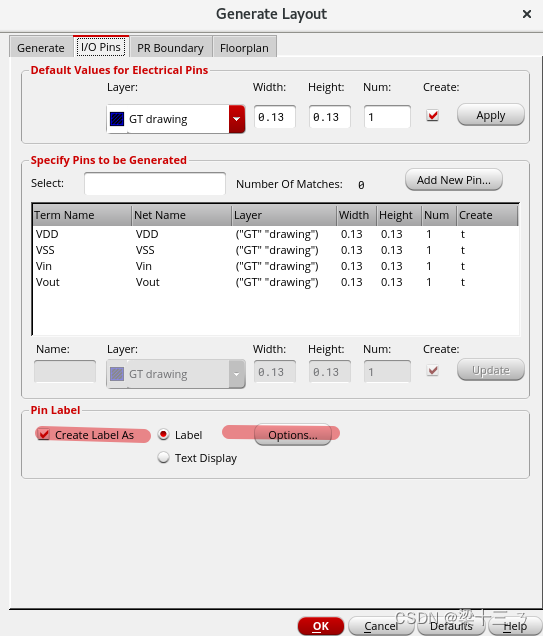

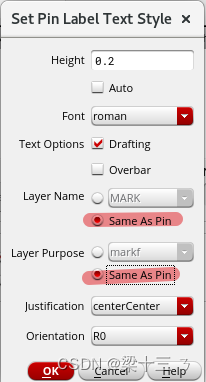

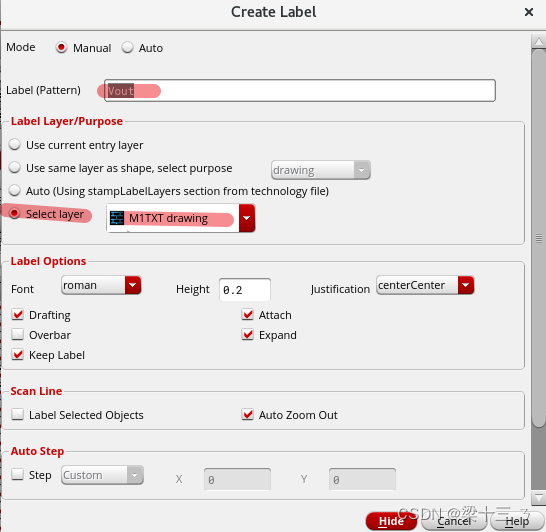

这里点击创造标签后点击options设置标签的大小和字体

大小设置为0.2或0.5,字体选择roma(罗马),然后选中画红线的两个选项

点击ok器件和pin被导入

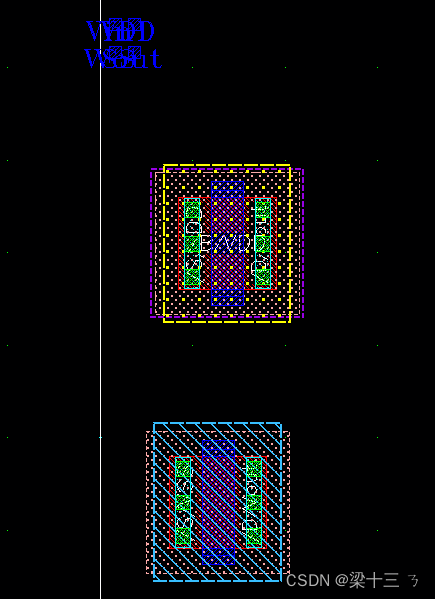

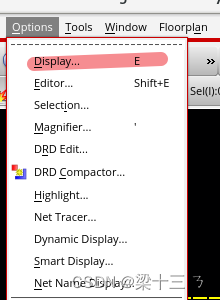

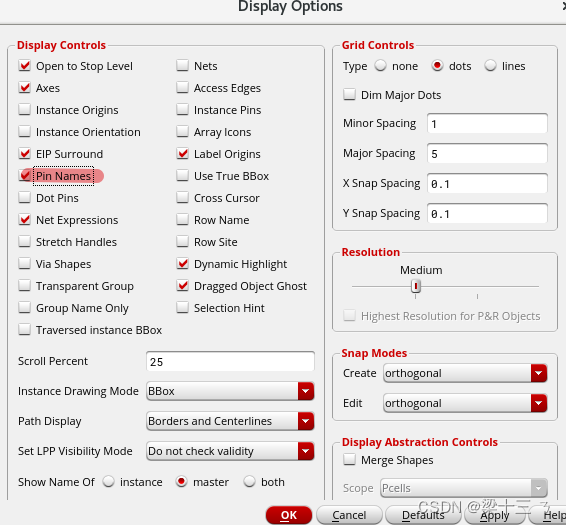

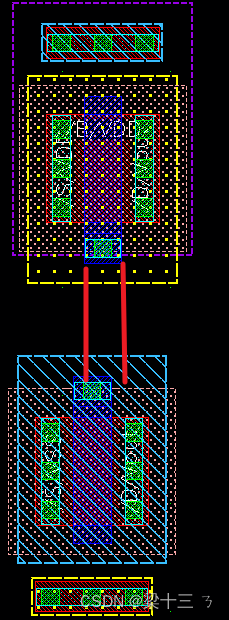

器件可能显示的是红色方块,点击快捷键shift+f显示器件的各层,还有左上角的pin可能没有名字,点击option>display,选择勾选pin name后引脚的标签就出现了(注意这里显示的器件形状和大小与选择的器件参数有关系,大小不一样也很正常)

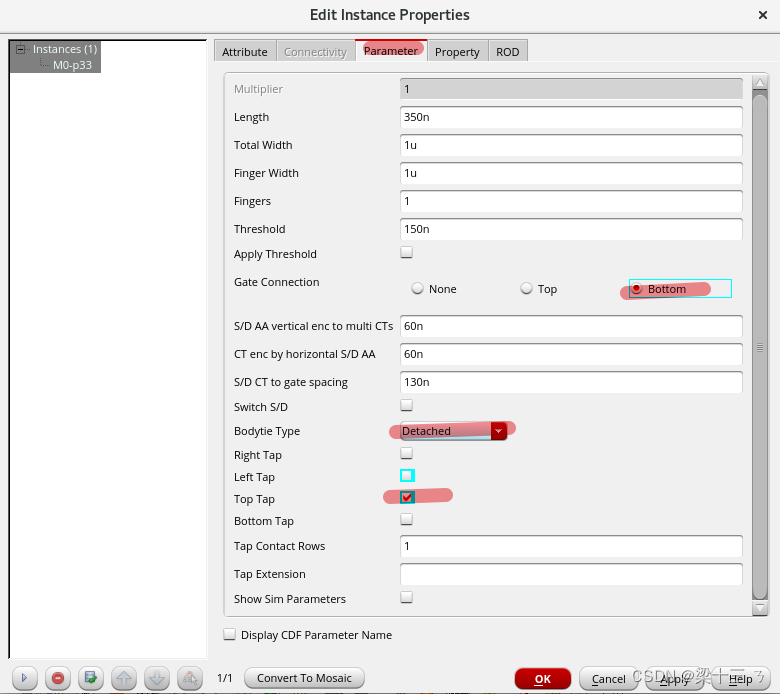

如果器件版图跟我的差不多的话,缺少B端,需要将B端显示出来,选择p管单击快捷键q

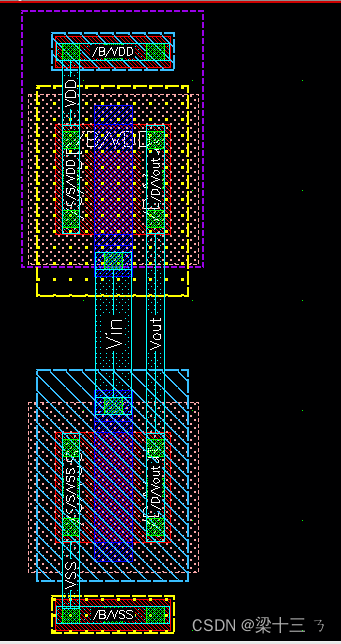

其中gate connection表示的是栅极连接,不勾选的话需要自己在栅极打出接触孔下面的bodytie表示的是体端,p管将体放在上面。点击ok

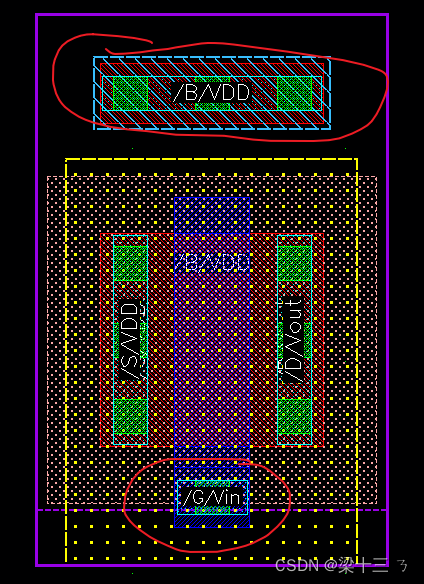

相较于之前只有这两个部分出现变化,上面就是B而下面是gate connection,gate connection也可以通过快捷键o打孔生成,但是需要注意的是要打到m1_gt层上面,左边就是打孔,将该图形放在G上面单击就打孔成功,打孔的规范较多容易在仿真的时候报错,一定要注意相应的规范。

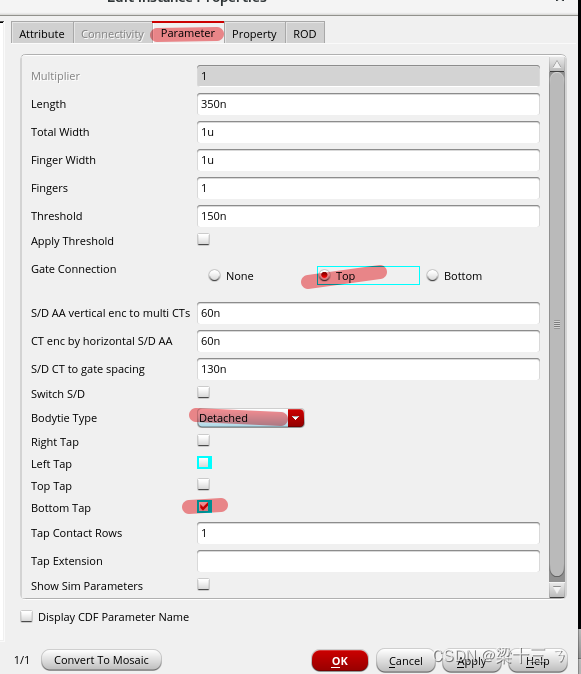

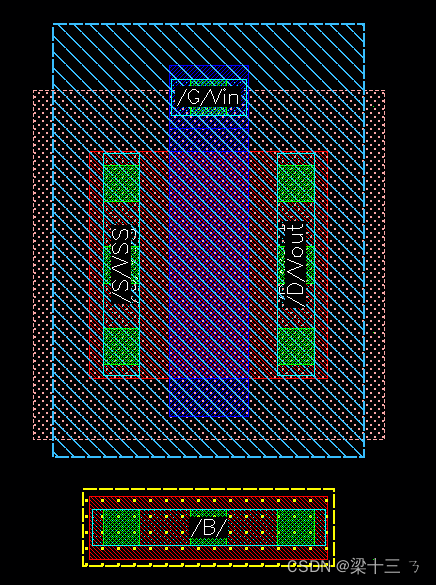

接下来对n管进行同样的操作,单击,按快捷键q,这里吧gate放在上面B放在下面便于连接。

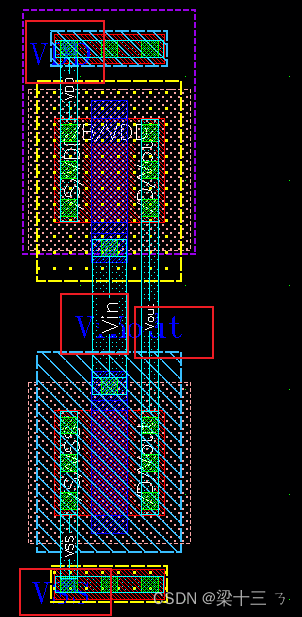

单击ok后如图所示

在连线之前先将器件的栅极对齐,这里栅极其实是错开的,点击快捷键a,然后选中一个管栅极的侧边,再选中另一个管栅极的侧边(鼠标可以自动锁定到边)

对齐后如图所示,这里栅极长相同是由于我最初设置的n管p管的栅极都是350n

接下来就可以进行连线了,单击快捷键p选中一个管的栅极,连接到另一个管的栅极上

随后将其他极也连接上

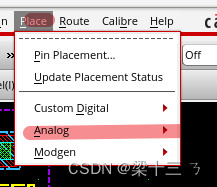

接下来将pin也放到对应位置,点击analog里面的adjust cell pin,但是放置的位置一般不太准确,需要手动调整,将pin调整到对应位置上

放置完之后如图所示

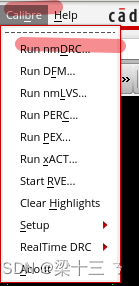

点击保存,接下来就可以进行仿真了 二、仿真 1.DRC仿真 点击run DRC,弹出出窗口

初次仿真点击cancel

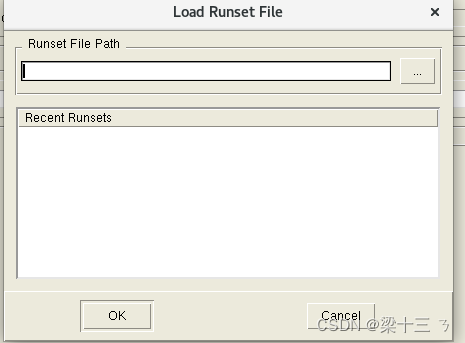

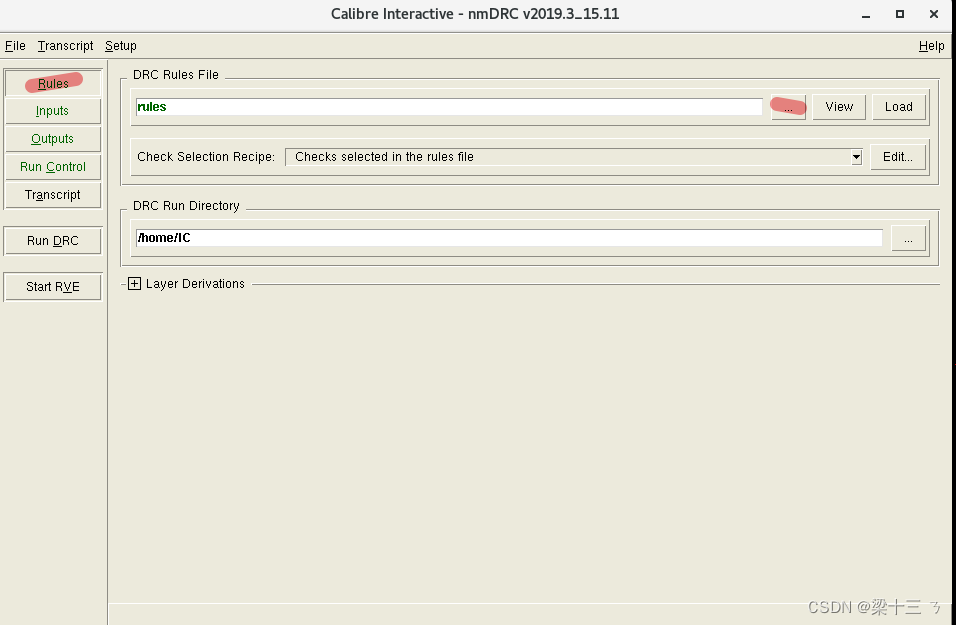

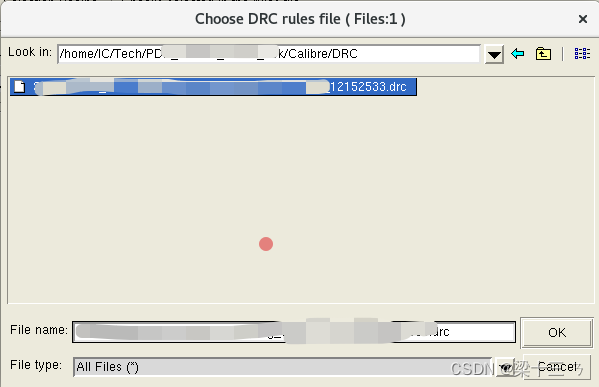

接下来进行设置,首先设置rules,选择PDK里面的calibre文件下的DRC里面的文件

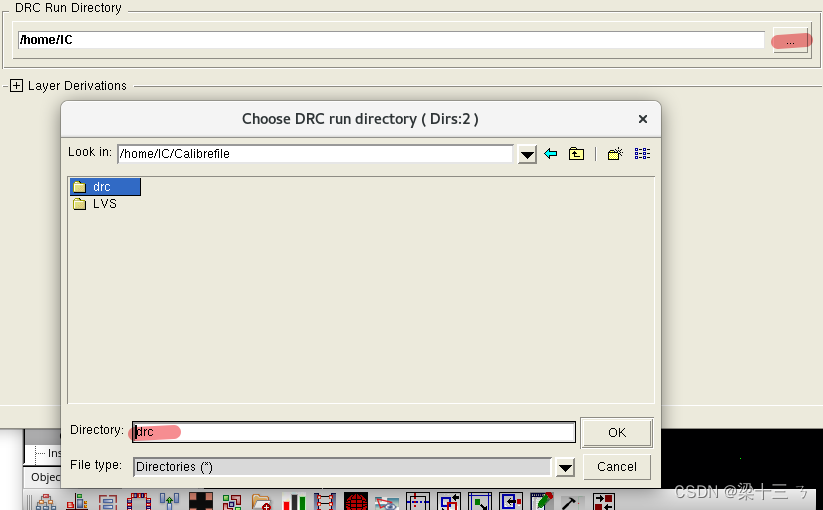

可以新建一个drc文件夹储存生成的文件(注意这里只能单击文件夹后点击ok,进入文件夹内部后点不了ok)

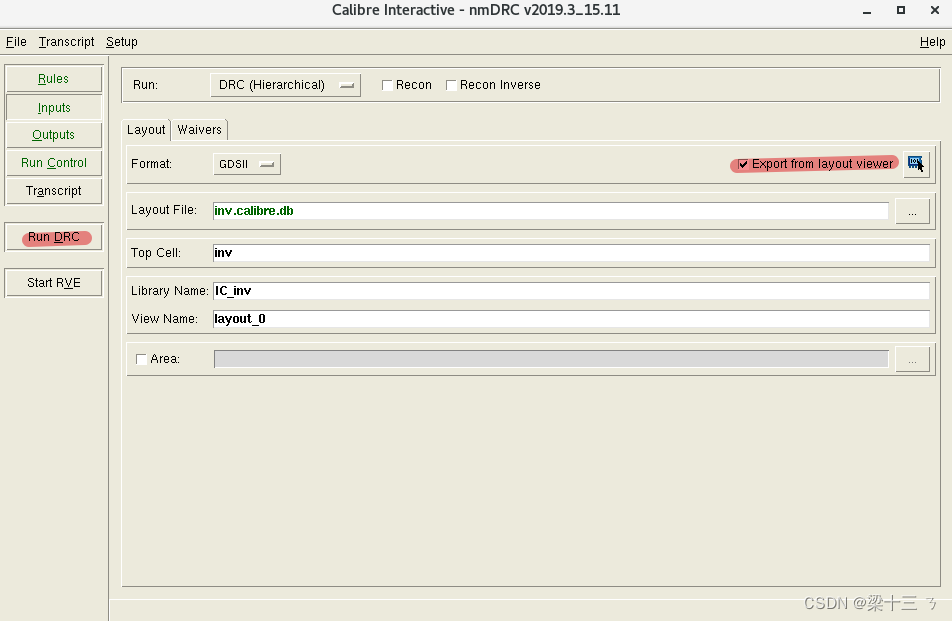

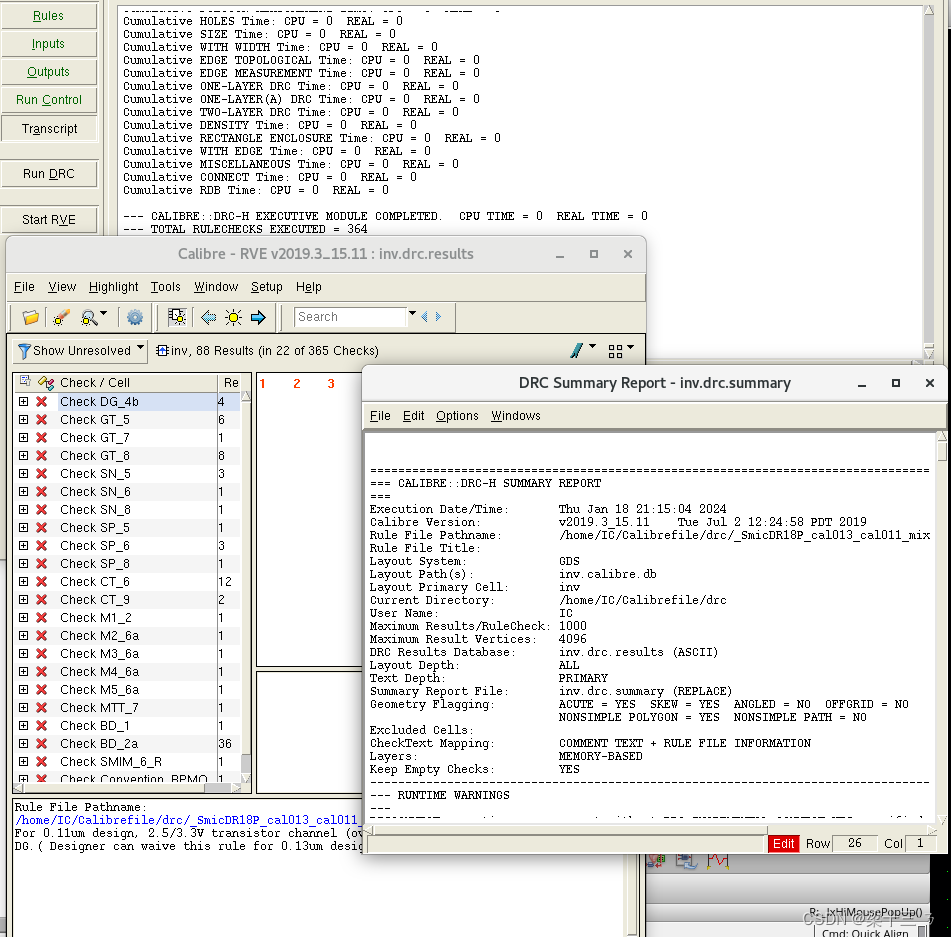

接下来在input里勾选从layout中提取,然后点击run drc

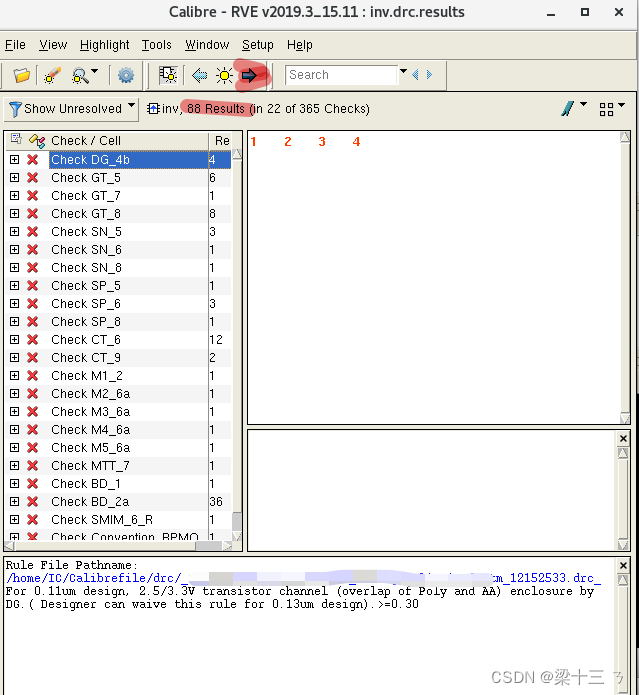

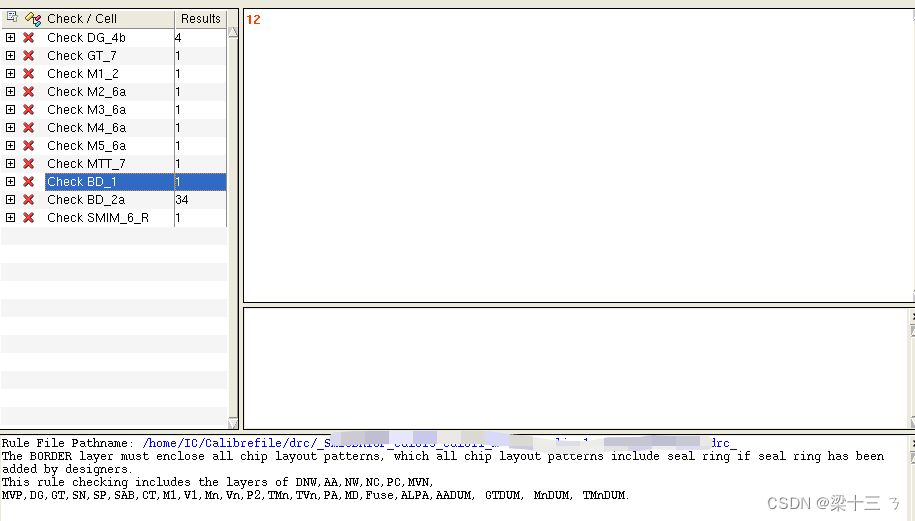

结果会弹出窗口,这的result代表错误选中错误单击箭头可以在图中显示对应的错误点

这些错误中关于BD的和密度的问题可以暂时不用管。 在关闭之前可以保存设置,下次仿真可以不用重新设置rules等选项 2. LVS仿真点击run LVS,弹出窗口

关掉第一个窗口(cancel)

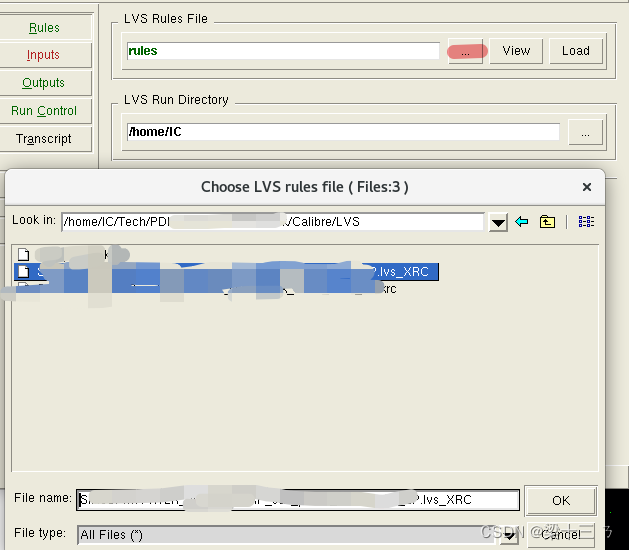

和刚才一样设置rule(在刚才的calibre文件夹下的LVS文件中)

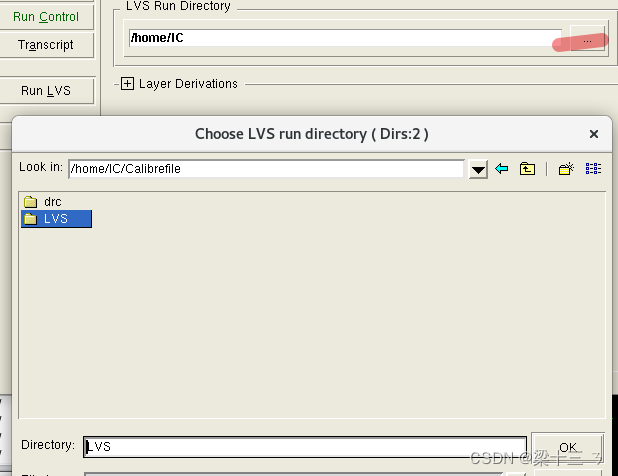

创建文件夹保存结果

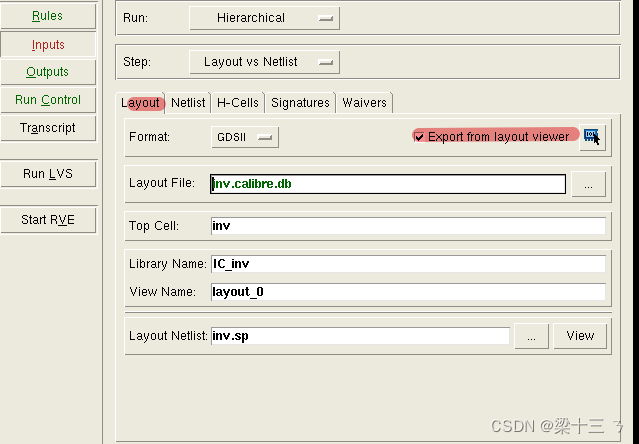

点击input在layout栏勾选

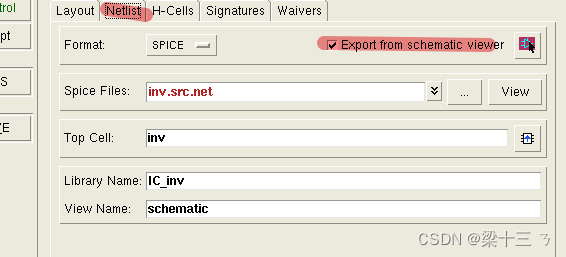

在netlist也勾选

接下来可以点击run lvs进行仿真

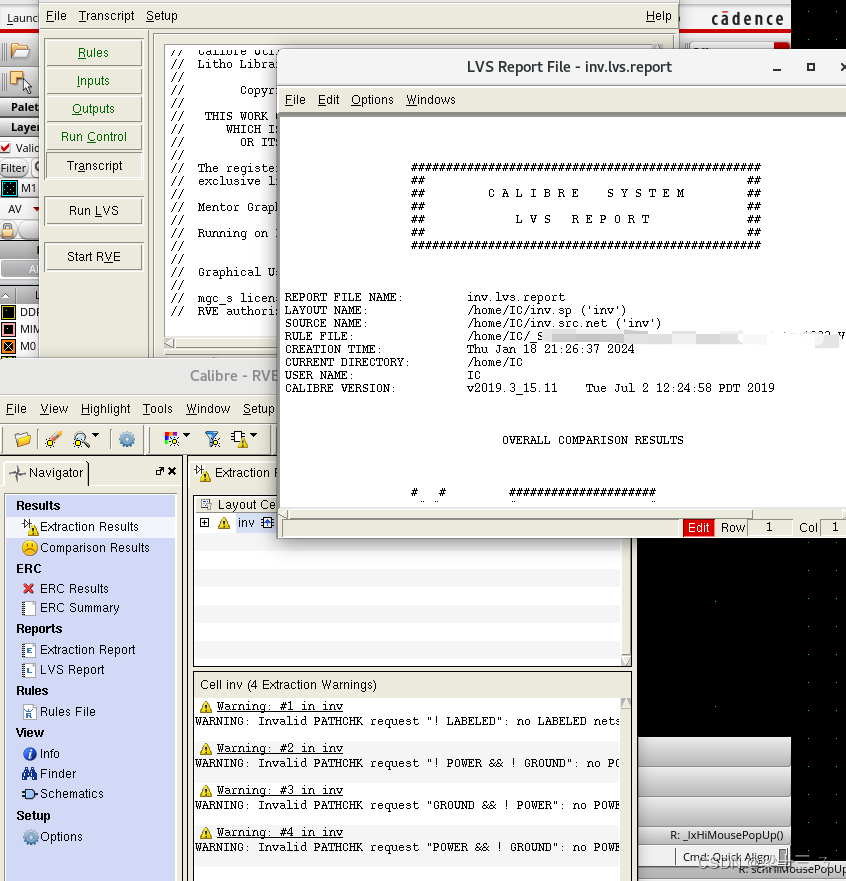

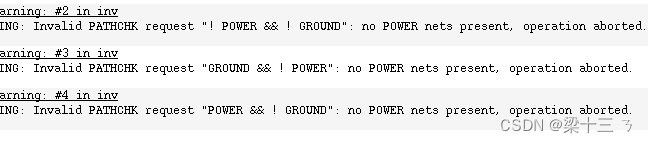

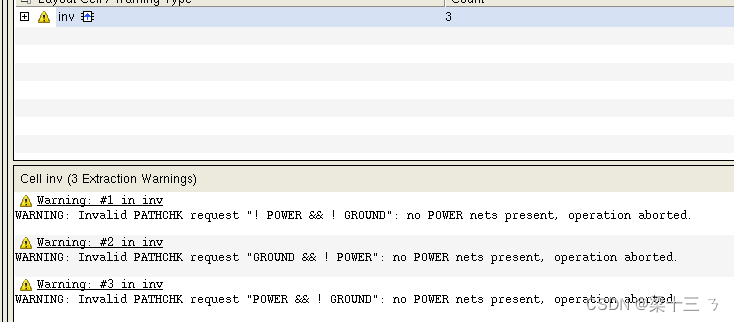

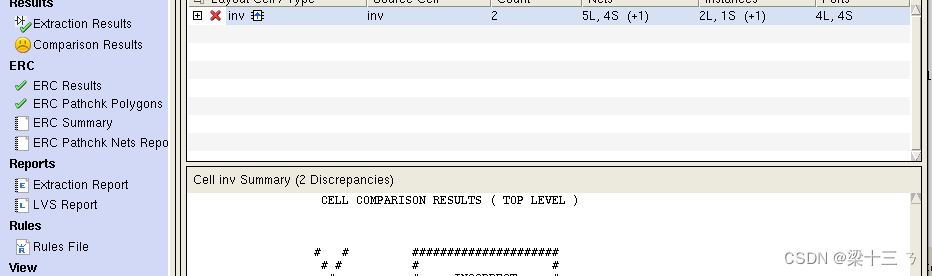

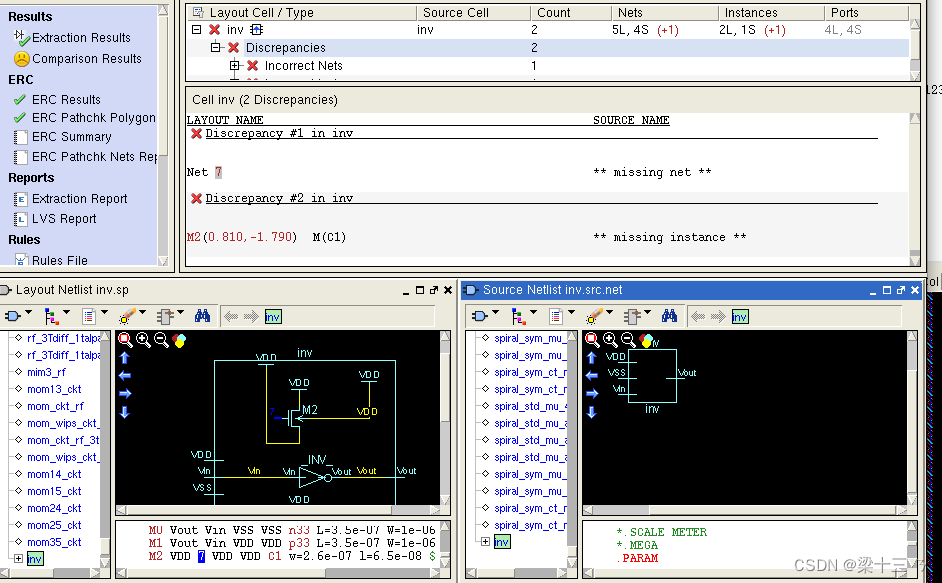

这里如果成功的话会显示笑脸 ERC是电气仿真,(按照步骤学习视频中这两项都没有报错)流程应该是这样的,猜测可能是因为所用的pdk不同或者是哪里出现错误 3.根据提示的错误进行修改,这里先修改LVS和ERC的错误,根据结果报错显示是标签的问题,尝试在图中打上标签

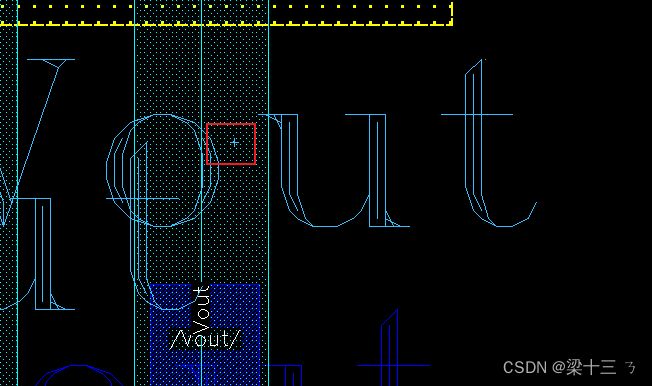

快捷键L,先给Vout打上标签,这里layer要选对M1TXT

注意这个加号要落在线上

接下来保存,再运行一下run LVS看看错误是否减少了(刚才没有关闭run lvs窗口)

如上图,错误少了一个,接下来给剩下三个都打上label再运行看看

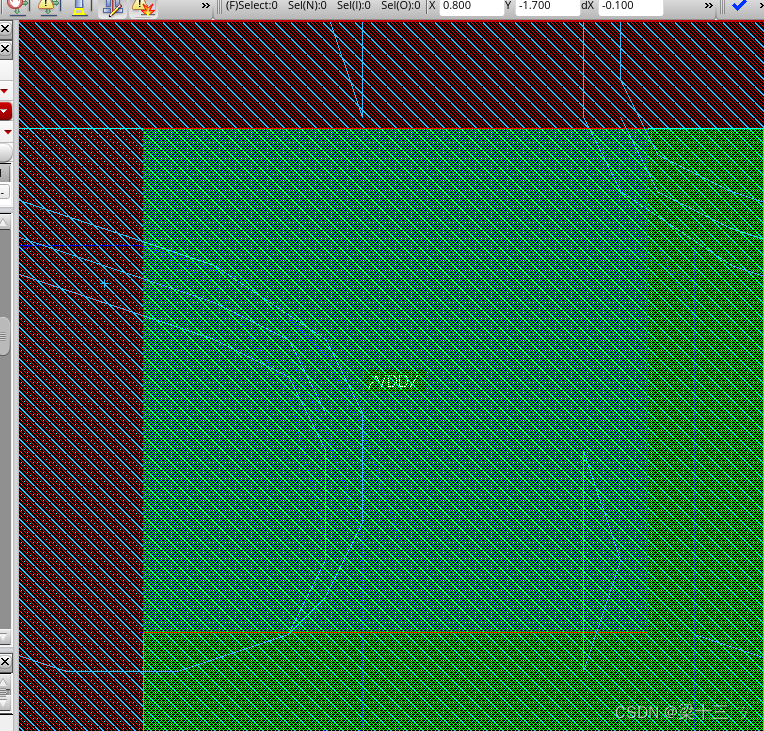

这里LVS还剩2处报错,ERC已经没有报错了 点击错误查看,,layout窗口会放大显示错误的地方

尝试将这里的VDDpin删掉试试

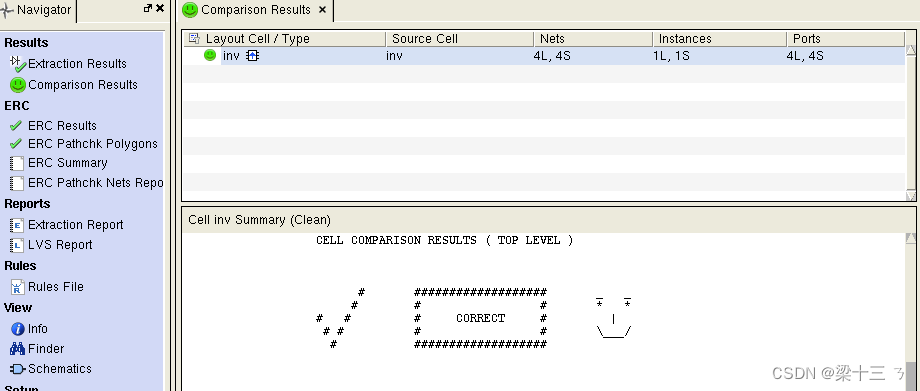

结果仿真成功 这里再重新进行一下DRC仿真

这里错误也少了很多,剩下的基本都是BD和密度的问题 总结使用的软件版本和pdk都可能对这个产生影响,后面可能会尝试不导入pin(我看很多博客都是这样)做的,针对仿真过程中产生的问题可以尝试去help中寻找解决方法,同时因为layout这里操作和规范都很多,需要认真细致的学习。 |

【本文地址】