FPGA基础知识极简教程(9)七段数码管显示的Verilog简单设计 |

您所在的位置:网站首页 › 动态扫描verilog › FPGA基础知识极简教程(9)七段数码管显示的Verilog简单设计 |

FPGA基础知识极简教程(9)七段数码管显示的Verilog简单设计

|

博文目录

写在前面正文七段数码管原理七段数码管译码表单个七段数码管显示verilog设计多个数码管动态扫描显示

参考资料交个朋友

写在前面

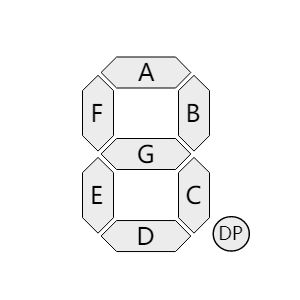

作为FPGA的基础知识教程怎么能少得了这个简单的实际应用七段数码管显示,本篇博文算得上是对以往这个话题的一个总结吧! 注:数码管本身是七段,但是加上小数点之后就是八段了! 正文 七段数码管原理七段显示器是FPGA设计人员通常用来向用户显示信息的指示器。在VHDL和Verilog中可以轻松完成将二进制文件转换为兼容七段显示器的代码。有许多应用程序可能需要使用一个或多个八段显示器,例如: 闹钟秒表按钮计数指示器电压测量(从模拟到数字转换器)等等! 如下是七段数码管的示意图:我们将七段分别标记为A、B、C、D、E、F、G,还有一个小数点DP。 如果用reg型变量来存七段数码管的位值,定义reg型变量: reg [6:0] seg;其中G对应seg[6],F对应seg[5],一直到A对应seg[0],小数点用专门的dp来表示。 七段数码管译码表那么要想显示0到F,对应的译码表为: parameter NUM0 = 7'h3f,//40, NUM1 = 7'h06,//79, NUM2 = 7'h5b,//24, NUM3 = 7'h4f,//30, NUM4 = 7'h66,//19, NUM5 = 7'h6d,//12, NUM6 = 7'h7d,//02, NUM7 = 7'h07,//78, NUM8 = 7'h7f,//20, NUM9 = 7'h6f,//10, NUMA = 7'h77,//08, NUMB = 7'h7c,//03, NUMC = 7'h39,//46, NUMD = 7'h5e,//21, NUME = 7'h79,//06, NUMF = 7'h71,//0e;注意,前面部分为共阴极时的译码表,后面注释掉的为共阳极的译码表! 所谓的共阳极,如下原理图所示:

以共阴极为例,对单个数码管显示的Verilog设计为: module Binary_To_7Segment ( input i_Clk, input [3:0] i_Binary_Num, input i_dp, //小数点输入 output o_Segment_A, output o_Segment_B, output o_Segment_C, output o_Segment_D, output o_Segment_E, output o_Segment_F, output o_Segment_G, output o_dp ); reg [6:0] r_Hex_Encoding = 7'h00; // Purpose: Creates a case statement for all possible input binary numbers. // Drives r_Hex_Encoding appropriately for each input combination. always @(posedge i_Clk) begin case (i_Binary_Num) 4'b0000 : r_Hex_Encoding |

【本文地址】

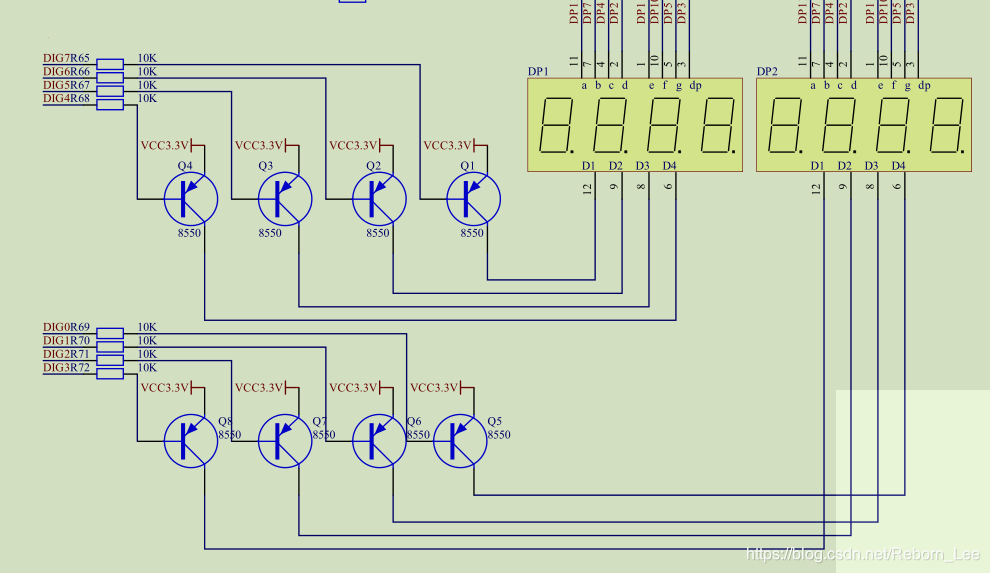

晶体管的集电极连接电源,片选低电平有效,片选选中时,晶体管导通,数码管公共端连接高电平,因此段选低电平,对应段发亮。

晶体管的集电极连接电源,片选低电平有效,片选选中时,晶体管导通,数码管公共端连接高电平,因此段选低电平,对应段发亮。