ECC 技术细节 |

您所在的位置:网站首页 › 内存错误纠正ecc:none是什么意思 › ECC 技术细节 |

ECC 技术细节

|

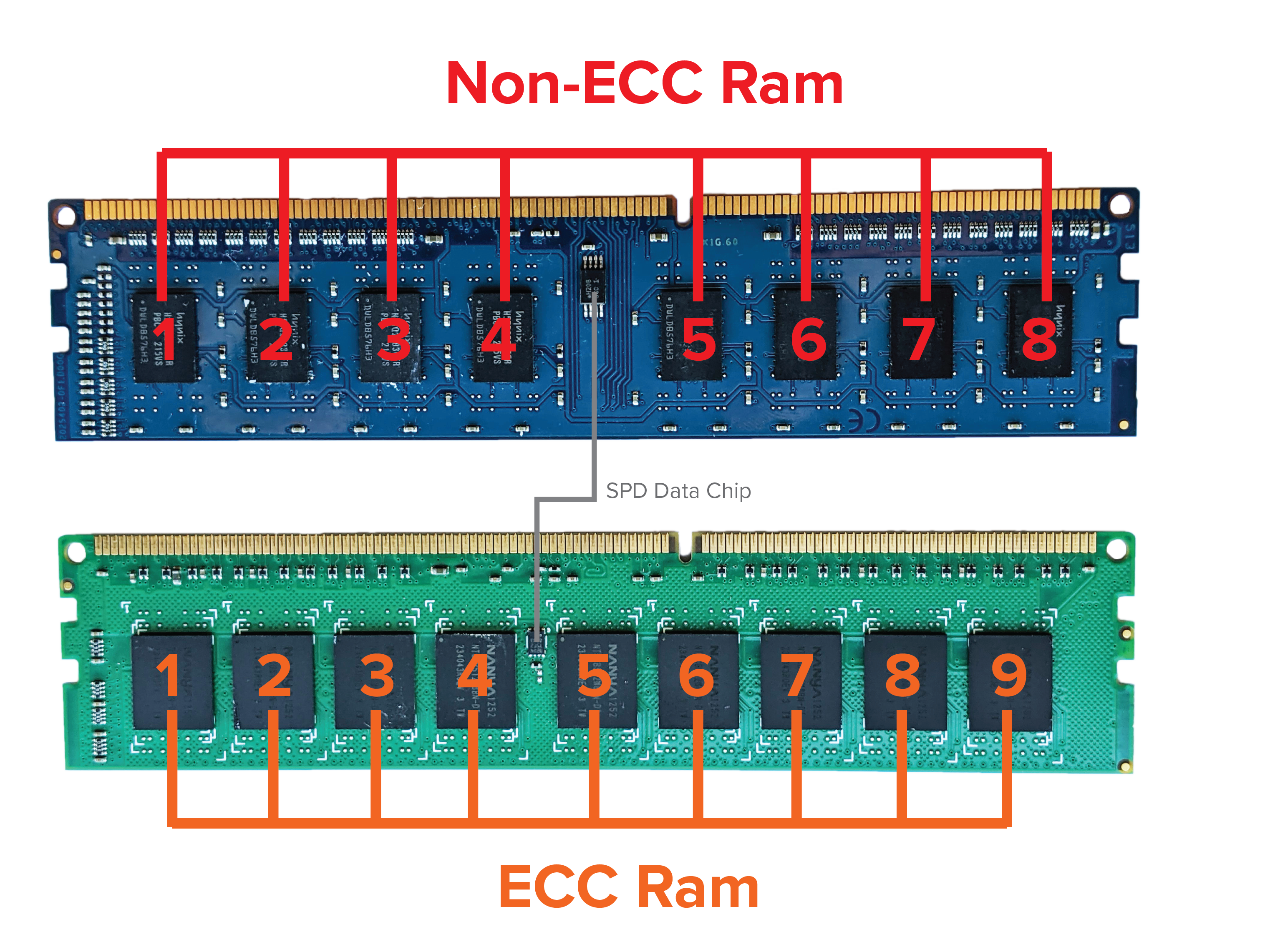

ECC 技术细节 什么是 ECC 内存?ECC如何工作? 有哪些不同的 ECC 方案?DDR5 ECC RAM 有哪些新功能?是否需要 ECC 内存?启用 ECC 保护需要哪些系统要求? 我需要更改 BIOS 设置吗?我如何知道何时检测到 ECC 错误? MemTest86 如何报告 ECC 错误?Windows 如何报告 ECC 错误?Linux 如何报告 ECC 错误?什么是ECC注射? 我可以使用 MemTest86 注入 ECC 错误吗?如何知道我的系统是否支持 ECC 注入?为什么我的 AMD 锐龙系统上没有报告 ECC 错误? 什么是 ECC 内存?纠错码 (ECC) 是一种机制,用于检测和纠正内存数据中的错误,因为 环境干扰和物理缺陷。ECC 内存用于高可靠性应用 不能容忍由于医疗设备、飞机控制系统或银行数据库服务器等数据损坏而导致的故障。 大多数内存错误是由软错误(例如宇宙射线,α射线,电磁干扰)引起的单个(1位)错误,但有些可能是由于硬件故障(例如行锤故障)引起的。 对于在较高高度运行的系统(例如商用飞机),软错误更为普遍。据说在大约10公里的高度,比特错误引起的宇宙射线要高出300倍。 这种单比特错误可以通过ECC内存系统进行纠正。多位错误也可能被检测和/或纠正,具体取决于出错的符号数量。 内存错误的症状包括数据损坏、系统崩溃和/或安全漏洞,使非特权代码无法访问内核。 众所周知,内存错误是大规模数据中心机器崩溃的最常见硬件原因之一。 ECC如何工作?ECC 是通过生成和存储加密的、类似奇偶校验的代码来实现的,该代码不仅用于识别错误位,还用于纠正错误位。 此依赖于实现的 ECC 代码在写入时生成并存储,并在读取时进行验证。 最常见的实现使用汉明码进行单位校正和双比特检测(SECDED)。 汉明码定义了奇偶校验位,这些奇偶校验位覆盖了一组预定义的数据位。通常,8 位汉明码用于保护 64 位数据。 ECC 验证步骤使用奇偶校验矩阵生成一个称为综合征的值。 如果综合征为零,则未发生错误。否则,它用于索引称为综合征表的查找表,以识别错误位(如果可纠正),或以其他方式确定错误是否不可纠正。 汉明 (7,4) 码的综合征表示例(4 个数据位 dn,3 奇偶校验位 pn) 编码为 p1p2d1p3d2d3d4具体如下: 症候群误差向量00000000001001000000010010000011000100000010001000101000010001100000101110000001例如,如果ECC验证步骤计算出要成为的综合征,则上述综合征表可用于查找要为的误差向量。 误差向量标识 d11100000014作为 7 位消息的错误位。 下面总结了读取和写入访问的顺序。 内存写入顺序 CPU 将写入数据发送到内存控制器(对于较新的 CPU,在同一芯片组上)内存控制器根据写入数据生成 ECC 代码内存控制器通过内存通道发送写入数据和 ECC 代码写入数据和 ECC 代码存储在内存 DRAM 芯片中内存读取顺序 CPU 向内存控制器发出读取请求(在同一芯片组上,对于较新的 CPU)内存控制器从内存读取数据和 ECC 代码内存控制器根据读取数据生成 ECC 代码内存控制器验证生成和存储的 ECC 匹配。如果没有,请使用 ECC SECDED 机制来纠正单位错误并检测双比特错误。完整的端到端 ECC 内存系统涉及内存访问期间的 CPU、内存控制器和 DRAM 模块。 因此,这些组件需要额外的电路来支持ECC功能。 例如,ECC RAM 包含一个额外的 DRAM 芯片来存储 ECC 代码,如下图所示。

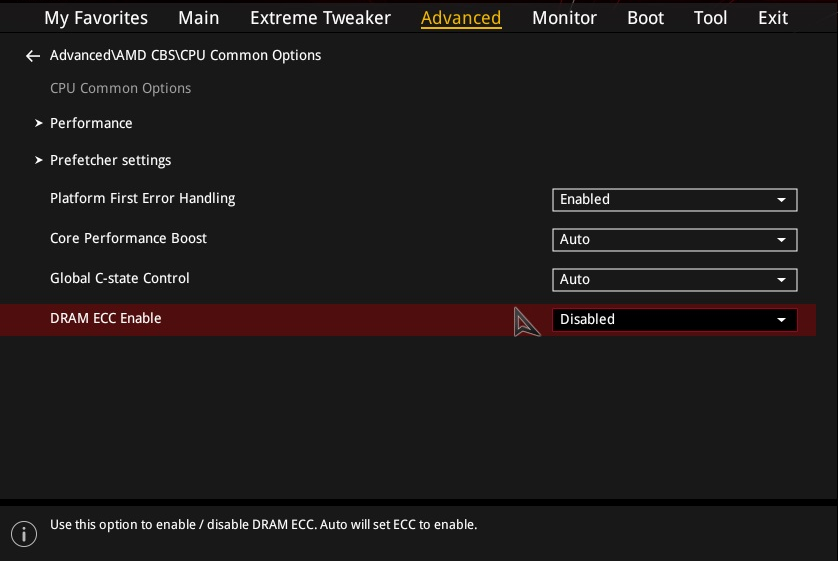

此外,存储器总线不仅包括数据DQ行(例如。DQ0-63),还有ECC校验位CB线(例如。CB0-7)。 通常情况下,ECC RAM也是寄存器RAM,它在内存控制器和DRAM插槽之间放置一个寄存器。 这减少了电气负载,特别是对于安装了大量RAM的系统,服务器级机器通常就是这种情况。 有哪些不同的 ECC 方案? 启用 ECC 的内存子系统可以使用以下一种或多种方案: 边带 ECC (DDR4/DDR5)内联 ECC (LPDDR4/LPDDR5)片上 ECC (DDR5)Link ECC (LPDDR5)边带式 ECC 边带 ECC 是当今 ECC 存储系统中使用的最典型的方案。 边带 ECC 需要支持硬件,包括内存控制器中的 ECC 逻辑、内存总线中的额外位以及内存模块中的独立 DRAM 芯片来存储 ECC 代码。 在写入操作期间,内存控制器生成 ECC 代码并将其与写入数据一起作为“边带”传输,而不会引入额外的命令开销。 在读取操作中,存储的 ECC 代码作为“边带”伴随读取数据,然后由内存控制器进行验证,并在必要时进行校正。 内联式电芯 内联 ECC 用于具有更严格硬件限制的 LPDDR 内存系统。这有效地消除了内存总线中额外位的要求,以及边带 ECC 所需的 ECC 代码的单独 DRAM 芯片。 与边带 ECC 不同,内联 ECC 不是将数据和 ECC 代码捆绑在单个命令中,而是为数据和 ECC 代码发出单独的读/写命令。 此外,ECC 代码存储在与数据相同的 DRAM 芯片中。因此,内联 ECC 会在读/写操作期间引入额外的命令开销。 片上 ECC 片上 ECC 是为 DDR5 内存引入的新方案,它完全独立存在于 DDR5 内存模块中。 与上述方案不同,片上 ECC 不提供端到端保护。片上 ECC 的目的是保护存储在 DRAM 阵列存储单元中的数据的完整性;它不会检测或防止在内存控制器和内存模块之间传输过程中发生的错误。 所有 ECC 检测和校正均在 DRAM 内存单元内部执行;它对 CPU 和内存控制器完全不可见。 为了提供完整的端到端保护,片上ECC需要与边带ECC结合使用。 链接 ECC Link ECC 是为 LPDDR5 内存引入的另一种新方案,用于增强对具有硬件限制的系统的端到端保护。 链路 ECC 本身不提供端到端保护;它为内存控制器和 DRAM 之间的通道上传输过程中发生的错误提供保护。 在写入操作中,内存控制器生成 ECC 代码并将其与写入数据一起发送到 DRAM 模块。 DRAM 模块接收写入数据,生成自己的 ECC 代码,并验证它是否与内存控制器发送的 ECC 代码匹配。 如有必要,将相应地更正单位错误。 与其他方案相反,Link ECC在存储在DRAM单元中时不会检测或防止错误。 为了提供完整的端到端保护,链路ECC需要与内联ECC结合使用,以提供完整的端到端保护。 DDR5 ECC RAM 有哪些新功能?上一代 ECC 内存系统 边带和内联 ECC 方案,可在 DRAM 单元中传输和存储过程中提供端到端的错误检测和纠正 DDR5 RAM 引入了两种附加方案,即片上 ECC(或片上)和链路 ECC,以补偿由于 DDR5 RAM 的速度和密度提高而导致的更高误码率 (BER)。 片上 ECC 可检测并纠正 DRAM 单元中可能发生的错误,例如 DRAM 行刷新期间。 由于工艺技术减小了存储单元的尺寸,错误率不断提高,片上ECC保持了“良好”的产量 记忆细胞。片上 ECC 对系统完全不可见。它的实现、编码/解码算法和元数据都完全包含在DRAM设备中,并且不向系统的其余部分提供有关错误检测和/或纠正的反馈。 同样,链路 ECC 检测并纠正 LPDDR5 链路或信道上的传输错误。与前几代产品相比,由于 LPDDR5 RAM 的速度和功耗发生了重大变化,DQ 线路出错的可能性要高得多。 Link-ECC 为速度和功率改进提供保护。 是否需要 ECC 内存?通常,在 ECC 硬件成本较高且性能略有下降与更高的系统可靠性和可用性之间需要权衡。 根据实现的不同,据说启用 ECC 可能会消耗额外的功率并将内存性能降低约 2-3%。 对于家庭或个人使用,内存错误的后果可能不足以证明额外费用是合理的。 然而,对于高度敏感的工业级系统,与内存故障的社会经济后果相比,额外的硬件成本可以忽略不计。 因此,ECC存储器应始终用于内存故障具有重大后果的系统(例如医疗设备,飞机控制系统,银行支付系统)。 启用 ECC 保护需要哪些系统要求?由于 ECC 保护需要额外的电路,CPU 芯片组、主板和 DRAM 模块需要专门的 ECC 硬件支持。 这包括以下内容: 支持 ECC 的服务器级 CPU 芯片组(英特尔至强、AMD 锐龙)主板支持ECC操作ECC 内存请参阅特定型号的主板和/或 CPU 文档,以验证硬件是否支持 ECC。 使用供应商提供的经认证的 ECC RAM 列表(如果提供)。 我需要更改 BIOS 设置吗? 大多数支持 ECC 的主板允许您从 BIOS 设置中配置 ECC 设置。 具体选项取决于主板供应商或型号,如下所示: DRAM ECC Enable(美国大趋势,华硕,华擎,微星)ECC 模式 (华硕)以下屏幕截图显示了此类 ECC 设置的示例。

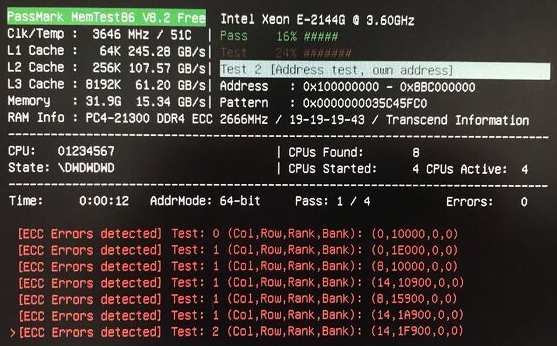

如何记录 ECC 错误并将其报告给最终用户的机制取决于 BIOS 和操作系统。 在大多数情况下,更正的 ECC 错误将写入系统/事件日志。未更正的 ECC 错误可能会导致内核死机或蓝屏。 MemTest86 如何报告 ECC 错误? MemTest86直接轮询芯片组/内存控制器寄存器中记录的ECC错误,并将其显示在屏幕上的用户。 此外,ECC 错误将写入日志和报告文件。 在测试期间,如果支持并启用了 ECC,MemTest86 可能会报告内存控制器检测到的 ECC 错误。 以下屏幕截图对此进行了演示:

检测到的 ECC 错误的可用信息程度在很大程度上取决于 CPU/内存控制器芯片组。这包括以下任何一项: 内存地址DRAM 地址(列、行、排名、库)通道和内存插槽编号以下示例说明了屏幕上显示的检测到的 ECC 错误的可能输出。 [ECC Error] Test: 1, Addr: 0x8F32540AC 在内存地址 0x8F32540AC 中检测到 ECC 错误。 [ECC Error] Test: 1, (Ch,Sl,Rk,Bk,Rw,Cl): (1,0,2,0,17900,0) 在通道1插槽0中的DIMM模块中检测到ECC错误,该模块指示了列位地址(0x2)、插槽地址(0x0)、行地址(0x17900)、列地址(0x0)。 [ECC Error] Test: 1, Channel/Slot: 1/0 在通道1插槽0中的DIMM模块中检测到ECC错误。没有关于触发 ECC 错误的内存地址的信息可用。 *注* ECC 错误报告的通道/插槽是从内存控制器的角度出发的,不一定与主板上预期的物理插槽相对应。 尽管大多数主板都是如此,但有些主板未映射到预期的物理插槽。一个特殊的主板是Supermicro H12SSL-NT,它遵循以下物理插槽映射: 举报的频道主板插槽0答11B12D13C14H15G16E17F1感谢lunadesign确定Supermicro H12SSL-NT的映射 由于不同芯片组之间的内存控制器架构不同,因此没有通用的 ECC 错误框架;每个芯片组都需要特定的 ECC 轮询代码。 具体而言,这将涉及轮询以下一个或多个硬件寄存器: 基于 x86 的系统的计算机检查体系结构 (MCA) 寄存器集成内存控制器 (IMC) PCI 寄存器英特尔 SoC 芯片组的边带寄存器AMD 锐龙芯片组的系统管理网络 (SMN) 寄存器机器检查体系结构 (MCA) 是一种特定于 x86 的机制,供 CPU 向更高级别的软件(例如操作系统)报告一般硬件错误。 这允许系统软件以通用方式处理硬件错误,而无需芯片组的内部细节。 它定义了一组通用的特定于模型的寄存器 (MSR),用于在检测到硬件错误时确定系统响应。在 ECC 错误的情况下, 可能会生成异常,即机器检查异常 (MCE),并且违规地址、通道和/或综合征可能会记录在 MSR 中。 某些芯片组还可能定义一组集成内存控制器 (IMC) PCI 寄存器,用于记录检测到的 ECC 错误,例如违规 DRAM 地址(等级、银行、行、列)、通道和/或综合征。这些寄存器通过标准PCI机制访问。 与机器检查架构 (MCA) 不同,PCI 寄存器特定于每个芯片组,并且需要单独的特定于芯片组的实现。 某些芯片组(如英特尔凌动 SoC)使用内部总线作为访问 ECC 寄存器的间接方法。 此类寄存器称为边带寄存器,在前面描述的PCI寄存器之上增加了一层额外的复杂性。 尽管有额外的层,但类似的ECC错误详细信息记录在这些寄存器中,例如DRAM地址(等级,银行,行,列),通道和/或综合征。 对于 AMD 锐龙芯片组,使用称为系统管理网络 (SMN) 的内部边带总线来访问 ECC 寄存器。 与英特尔 SoC 中的边带寄存器类似,SMN 寄存器是访问记录在这些寄存器中的 ECC 错误详细信息(如 DRAM 地址(秩、库、行、列)、通道和/或综合征)的间接方式。 Windows 如何报告 ECC 错误? 在 Windows 中检测到的 ECC 错误在事件日志中显示为 Microsoft Windows 硬件错误体系结构 (WHEA) 警告事件。 Log Name: System Source: Microsoft-Windows-WHEA-Logger Date: 1/1/2021 12:00:00 AM Event ID: 19 Task Category: None Level: Warning Keywords: User: LOCAL SERVICE Computer: WIN10 Description: A corrected hardware error has occurred. Reported by component: Processor Core Error Source: Corrected Machine Check Error Type: Cache Hierarchy Error Processor APIC ID: 2如果在 BIOS 中正确启用了 ECC,最终用户应该能够通过 WHEA 接收错误,而无需在 Windows 中进行任何配置。 Linux 如何报告 ECC 错误? Linux 内核支持通过 EDAC(错误检测和纠正)驱动程序子系统报告 ECC 内存的 ECC 错误。 根据 Linux 发行版,ECC 错误可能会由以下人员报告: mcelog- 收集和解码 x86 上的 MCA 错误事件(已弃用)edac-utils- 填充 DIMM 标签数据并汇总内存错误(已弃用)rasdaemon- 监控 ECC 内存,并在最近的 Linux 内核上报告可纠正和不可纠正的内存错误安装 rasdaemon rasdaemon 可以使用相应的包管理器为大多数 Linux 发行版安装: apt-get install rasdaemon # Debian/Ubuntu 启用 rasdaemon 服务 rasdaemon 服务可以使用 systemd 服务管理器 systemctl 启动 systemctl enable rasdaemon systemctl start rasdaemon 查询 ECC 错误计数和摘要 # ras-mc-ctl --error-count Label CE UE mc#0csrow#2channel#0 0 0 mc#0csrow#2channel#1 0 0 mc#0csrow#3channel#1 0 0 mc#0csrow#3channel#0 0 0 # ras-mc-ctl --summary Memory controller events summary: Corrected on DIMM Label(s): 'mc#0csrow#2channel#1' location: 0:2:1:-1 errors: 3 Corrected on DIMM Label(s): 'mc#0csrow#3channel#0' location: 0:3:0:-1 errors: 3 Fatal on DIMM Label(s): 'mc#0csrow#3channel#0' location: 0:3:0:-1 errors: 1 什么是ECC注射?ECC 注入是内存控制器中引入的一项调试功能,用于人为插入内存错误以验证系统行为是否正确。 此功能旨在供开发人员和系统集成商使用,而不是供最终用户在生产中使用。 根据供应商的不同,可以使用各种ECC注入选项(例如。英特尔,AMD)和芯片组(例如。至强,锐龙,原子)。 这些选项包括: 读取和/或写入数据路径地址范围每块计数单位或多位错误单次或连续我可以使用 MemTest86 注入 ECC 错误吗? 如果 CPU/内存控制器芯片组支持错误注入并且该功能未被 BIOS 锁定,则 MemTest86 专业版支持 ECC 注入。 查看 MemTest86 支持的具有 ECC 注入功能的当前芯片组列表。 在主菜单或配置文件中启用 ECC 注入后,MemTest86 将尝试在每次测试开始时注入单位 ECC 错误。 如果系统成功注入并检测到 ECC 错误,用户应看到 [ECC 注入] 消息,后跟 [检测到 ECC 错误] 消息。 如果未出现[检测到 ECC 错误] 消息,则很可能 BIOS 锁定或禁用了 ECC 注入。 如何知道我的系统是否支持 ECC 注入? 通常,ECC 注入不是最终用户通常可以访问的功能。即使芯片组支持 ECC 注入功能,细节通常也很少,并且不会在公开的数据表中描述。 请参阅 CPU/内存控制器芯片组的数据表,以确定 ECC 注入功能是否可用且完全指定。 特别是,某些英特尔芯片组(Broadwell、至强可扩展)使用英特尔可信执行技术(英特尔 TXT)来锁定 ECC 注入。 英特尔 TXT 使用安全硬件模块验证 BIOS、固件、操作系统和虚拟机管理程序的完整性,以保证可信的操作环境。 因此,这需要防止对特定内存控制器寄存器(包括 ECC 注入寄存器)的访问受到损害。 某些支持 ECC 注入的芯片组具有锁定机制,一旦在 BIOS 中启用,就会有效地禁用 ECC 注入功能。 对于这些情况,可以使用 BIOS 选项使该功能保持解锁状态。否则,需要自定义 BIOS 才能解锁该功能。 为什么我的 AMD 锐龙系统上没有报告 ECC 错误?BIOS设置,平台优先错误处理(PFEH)可能会阻止ECC错误报告给MemTest86。 以下屏幕截图显示了此设置的示例。

如果启用此设置,请设置为禁用,然后再次尝试运行 MemTest86。 另一种解释是使用带外(OOB)监控解决方案,例如基板管理控制器(BMC)和智能平台管理接口(IPMI)。 用于服务器平台(例如。美超微服务器) |

【本文地址】