分辨率、刷新率、像素时钟速率、通道速率(dsi) |

您所在的位置:网站首页 › 兽设爪子模板 › 分辨率、刷新率、像素时钟速率、通道速率(dsi) |

分辨率、刷新率、像素时钟速率、通道速率(dsi)

|

刷新率:

分为垂直刷新率和水平刷新率,一般提到的刷新率通常指垂直刷新率。垂直刷新率表示 屏幕的图象每秒钟重绘多少次,也就是每秒钟屏幕刷新的次数,以Hz(赫兹)为单位。刷新率越高越好,图象就越稳定,图像显示就越自然清晰,对眼睛的影响也越小。刷新频率越低,图像闪烁和抖动的就越厉害,眼睛疲劳得就越快。一般来说,如能达到80Hz以上的刷新频率就可完全消除图像闪烁和抖动感。 分辨率:分辨率可以从显示分辨率与图像分辨率两个方向来分类。 显示分辨率(屏幕分辨率)是屏幕图像的精密度,是指显示器所能显示的像素数量。由于屏幕上的点、线和面都是由像素组成的,显示器可显示的像素数量越多,画面就越精细,同样的屏幕区域内能显示的信息也越多,所以分辨率是个非常重要的性能指标之一。可以把整个图像想象成是一个大型的棋盘,而分辨率的表示方式就是所有经线和纬线交叉点的数目。显示分辨率一定的情况下,显示屏越小图像越清晰,反之,显示屏大小固定时,显示分辨率越高图像越清晰。 图像分辨率则是单位英寸中所包含的像素点数,其定义更趋近于分辨率本身的定义。 mipi: 总述在上一篇DSI协议协议讲解后,相信很多人还是云里雾里,因为一个是概念太多,另一个是纯理论,没有结合实际项目分析,难以让人有深刻的理解。看完本篇章依旧会云里雾里。但是还是要讲。本篇章将讲述DSI协议的时钟计算和常见概念区分,结合实际的开发过程,把MIPI时钟的意义、计算方式以及DSI协议中的几个容易混乱的概念进行区分。 (一)DSI协议讲解 (二)DSI时钟的计算和常见概念区分 (三)DSI时序讲解与实际测试 注:本系列文章有时候描述不严谨,MIPI 与DSI混用,MIPI是包括多种协议接口的总称,而DSI是特指MIPI在显示屏上的应用协议。大部分情况下,这么混用,相信大部分读者也是不会有误解的。 时钟计算任何一个协议接口,都必须依赖时钟进行数据传输,比如串口、SPI、I2C、MIPI,包括其他液晶接口LVDS EDP等等。因为只有有时钟,数据才能进行按部就班的传输,否则传送接收不按照一定的规则来,就无法被准确识别。只是有的协议接口上明着存在时钟线,比如I2C(i2c clk)、MIPI(clock lane),有的协议明面上没有一条时钟线,比如串口,但是他们一定会依赖时钟来进行传输数据,串口来说就是波特率,它是主从设备两端通过一定的时钟频率来发送接收的概念,所以串口本质上还是要依靠时钟来进行传输数据。 回到DSI的时钟上,我们来讲讲它的时钟是什么,有哪些种类,怎么计算。

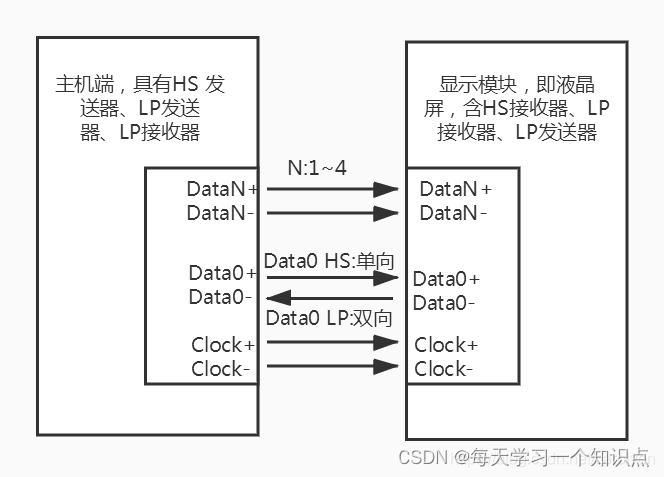

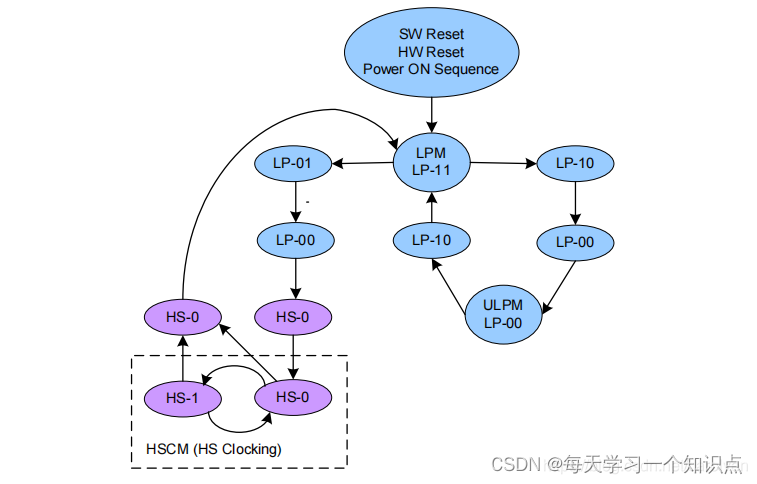

我们还是先搬出这张DSI接口图,可以看到有一组Clock+ Clock-的连接线,这组连接线就是DSI的时钟信号线了。主从设备依靠这组时钟线上传输的时钟信号来指挥数据的传输和解析(LP模式下不需要这组时钟,因为在LP模式下的数据传输依靠的是Data0+ Data0-的异或来作为时钟的)。 液晶基础时钟概念 通用时钟概念PORCH:液晶时序当中,常常用到的一些参数HSYNC、HBP、HACTIVE、HFP,VSYNC、VBP、VAVTIVE、VFP,概念如下: HFP: Horizon front porch HBP: Horizon back porch VFP: Vertical front porch VBP: Vertical back porch HACTIVE: Horizon display period VAVTIVE: Vertical display period H-total = HSYNC+HBP+HACTIVE+HFP V-total = VSYNC+VBP+VACTIVE+VFP 上述porch概念的具体含义,这里就不展开描述了。网上有很多资料,后续如果有更新液晶接口系列——RGB接口的话也许会重点讲解下这部分。简单说H-total 和V-total分别表示,为了传送一帧图像,每一行数据需要实际传送的像素数(H-total )和总共需要传输几行(V-total),而这两个值不等于分辨率原因在于图像传输有一些时序要求,方便数据的同步等,所以每一行都会用一些无用(非图像数据)的像素(pixel)传输。 2、DSI时钟概念 Total pixel = H-total x V-total x fps(一般是60)fps是帧率,表示1s内传输的图像帧数,H-total x V-total表示一帧图像要传输的总pixel数,所以Total pixel 表示1s内要传输的pixel总数。说白了就是1s要传输多少个点。 Bitclk= Total pixel x 位深/lane number 位深:简单说是表示一个像素点需要多少bit来表示,比如如果rgb888格式的图像的,那就是3*8=24bit,如果是rgb565格式的图像,那位深就是5+6+5 = 16bit。以rgb888位例子,每个pixie要用24bit来表示,那么Total pixie x 24 表示的是1s内要传输多少个bit,所以Bitclk就表示1s内一条数据lane线上传输的bit总数。 Byteclk = bitclk/8显然1Byte = 8bit,所以Byteclk =bitclk/8,表示1s内一条数据lane线上传输的Byte数。 pclk(Dsi pixel clock) = (Byteclk * lane number)/bpp(byte) = Total pixel bpp简单说就是表示一个像素点需要用几个Byte表示,所以pclk就是表示1s内所有的lane传输的总Byte数/每个像素占用的字节数 = 所有的lane传输的总pixel数,与Total pixel 值相等。 UI = 1/BitclkUI是MIPI时序中很多时间要求的基本单位,我们可以从液晶IC的时序要求手册上看到它的身影,很多时序的上升沿、时序间隔等以UI为单位,用xx UI来表示时序要求。 注:A、实际测的MIPI时钟:= Bitclk /2 (因为是双边沿采样,一个时钟可以穿两个bit的数据) B、有些平台,Bitclk的计算方式不同,上述公式是理论上的,以高通平台为例的,但是有些平台(比如展锐)公式如下,且建议用该公式进行计算:Bitclk = Total pixel x 位深 x 1.2 / lane number 加主要是为了提高时钟,因为MIPI传输协议中,实际传输数据还会包括包头、包尾等更多的非图像数据,而没有乘以1.2计算出来的时钟是刚好够传输图像的时钟,如果不乘以1.2,那么时钟就会过小,因为被协议数据占据了一部分时钟,这样会导致时钟过低,从而液晶无法正常显示。1.2这个值是个经验值,而RK平台通常是在理论计算出后直接加上100Mhz,而不是乘以1.2. C、如B所说,那么为什么高通平台可以直接不乘以1.2也不用加100Mhz呢?这个就设计到MIPI传输的burst mode传输。简单说,就是burst mode传输在进行传输图像的时候,将图像数据压缩了,从而大大加快图像传输的实际耗时(也就是耗用的时钟),这样他就留出了多余的时钟出来供协议数据进行传输。其他平台虽然也是支持burst mode的,但是平台在时钟的计算上可能有所限制(比如无法精准分频,高通可以),会导致时钟计算出来的哪怕有burst mode也是不足的。该问题曾经在某大神群里得到了一些解答,但是由于个人对于MIPI协议没有那么熟悉,至今还是有一些疑惑。后续针对该问题,也许会再扩展一篇专题分享文档。 DSI时钟计算 重点重点重点,重点来了,有了前面这些概念,现在我们可以来学校下怎么算时钟 对于任何液晶接口,其时钟计算的基本原则就是:时钟 = 1s内液晶接口传送的数据量,很多平台时钟概念有不同的表示,但是最终都是依赖这个计算原则来算的。所以mipi接口时钟(就是你用示波器去测量Clock lane的波形频率,是最终体现在接口上的实实在在的能测量到的时钟)公式如下 dsi clk = Bitclk / 2 = H-total x V-total x fps x 位深 / lane number / 2 上面公式中为什么要除以2,因为我们上一篇中讲过,MIPI采用双边沿采样传输,即一个时钟的上升沿和下降沿都可以传输数据,所以一个时钟可以传输2个bit,所以需要的实际时钟就可以只要是bitclk的一半就可以了。(如DSI时钟概念下的 “注B” 所分析,有的平台最终结果还要乘以1.2或者加上100M等) 来来来,我们for example下,比如我们要调试的液晶,porch参数如下: HFP=48, HBP=48, HSYNC=32, VFP=8,VBP=8, VSYNC=4,HACTIVE=1920,VAVTIVE=1080,传输的图像格式是rgb888,fps=60,使用4个lane来传输。 那么 dsi clock = H-total * V-total * fps*位深 / lane numberl / 2 =(HSYNC+HBP+HACTIVE+HFP)*(VSYNC+VBP+VACTIVE+VFP) * 60 * 24 / 4 / 2 = 405504000 Hz =405.50 Mhz DSI的“模式”概念区分 在协议讲解的篇章中,我们提到了DSI的各种模式,LP模式、HS模式、Control Mode、Escape Mode、LPM模式、Bus Turnaround Request等等,这么多模式,很容易把我们搞晕,他们之间是什么关系呢? 根本模式是LP模式和HS模式,其模式下线路有不同的电平状态,不同的电平状态通过不同的时序组合可以使得LANE进入不同的模式(三种模式之一:High-speed(高速模式)、Control mode(低速模式)、Escape mode(低速模式)),对于CLOCK 和 DATA LANE,它们进入的不同状态又有具体的不同划分(对应上述三种模式的其中部分模式),如下: CLOCK有三个模式: 低功耗模式LPM (Low Power Mode) 超低功耗模式ULPM(Ultra Low Power Mode) 高速时钟模式HSCM(High Speed Clock Mode) DATA有三个模式: Escape Mode, High-Speed Data Transmission, Bus Turnaround Request 每种状态进入的时序如下图和下表所示: Clock Lane: Data Lane: 液晶屏的模式COMMAND模式和VIDEO模式 这个是针对屏幕来说的,简单理解,如果是通过将数据写到液晶IC中的GRAM的,即为COMMAND模式的屏幕(通过每次写显示数据时需要先发送命令给屏幕:我要开始写屏幕了,要写的位置坐标是(x,y))。而video模式的屏幕除了一开始给液晶IC的初始化命令(写IC的各种寄存器去开启液晶的各种配置,command屏也会有),后面屏幕的显示是一直不中断的给他发送显示数据的。 VIDEO屏的三种模式 Non-burst Mode Sync pulses Non-burst Mode Sync event Burst mode

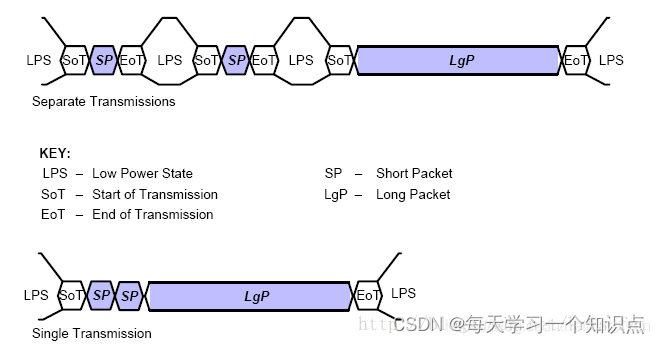

1、data lane传输数据时会进入LP 连续传输传输数据的时候,每次传输完一包数据,会进入LP模式。平台上有时候可以配置,使得可以连续发送多包才进入LP模式。至于多少包,有的是一行图像数据,有的是一帧图像数据,具体设置看平台。该配置目前本人还未非常明确。 2、Separate transmission和Single Transmission 当packet很多时,由于每次HS mode传输间会插入LPS,这样效率会很低。所有有了如下Separate transmission和Single Transmission两种传输方式: Separate方式: 无论是short packet 或者 long packet传输,中间都会加上LPS Single 方式:在发完Short packet之后马上发送Long packet,不插入LPS

对于clock这个lane,也有continuous clock behivor何non-continuous clock behavior的方式,作为continuous clock behivor时,clock一直处于工作状态,而作为non-continuous clock behavior时, clock在每次HS data传输之间进入LP11状态。他们的本质区别就是在LPM和HSCM之间做切换。当packet很多时,由于每次HS mode传输间会插入LPS,这样效率会很低。所有有了Separate transmission和Single Transmission两种传输方式 总结 本篇重点从DSI的时钟计算和DSI的模式区分为重点展开,对于MIPI协议的深入理解,实际上仍然只是冰山一角的内容。如果需要更加彻底深入理解MIPI,建议还得从液晶IC的芯片手册以及实际的调试、时序波形抓取入手,更有利于理解本篇所说的内容 链接:https://blog.csdn.net/carolven/article/details/119284541 |

【本文地址】

今日新闻 |

推荐新闻 |

这三种模式的区别主要是在于传输图像过程中,不同模式会发送不同的数据包,最常用的是burst mode。具体差别可以看DSI协议讲解中的参考链接,或者从液晶的IC手册中去看,一般都会有。

这三种模式的区别主要是在于传输图像过程中,不同模式会发送不同的数据包,最常用的是burst mode。具体差别可以看DSI协议讲解中的参考链接,或者从液晶的IC手册中去看,一般都会有。