数字电路与逻辑设计:计数器及其设计(Multisim) |

您所在的位置:网站首页 › 八进制计数器原理 › 数字电路与逻辑设计:计数器及其设计(Multisim) |

数字电路与逻辑设计:计数器及其设计(Multisim)

|

计数器及其设计(Multisim)

一、 实验目的二、 实验仪器与器件三、 实验内容及步骤四、 思考题

一、 实验目的

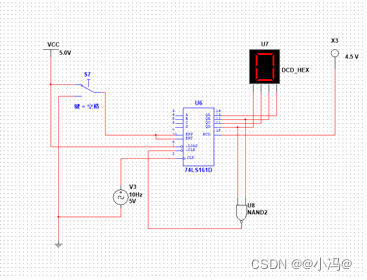

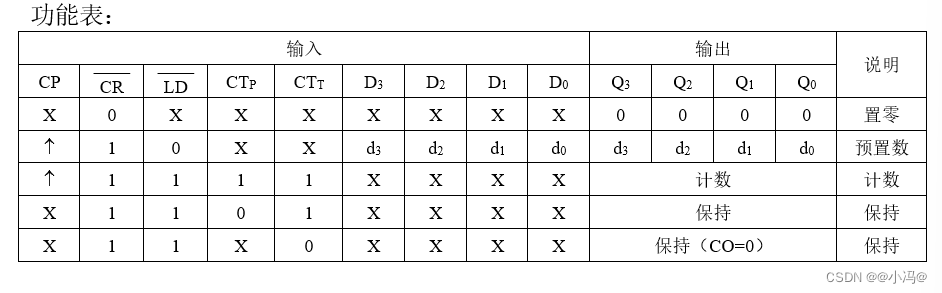

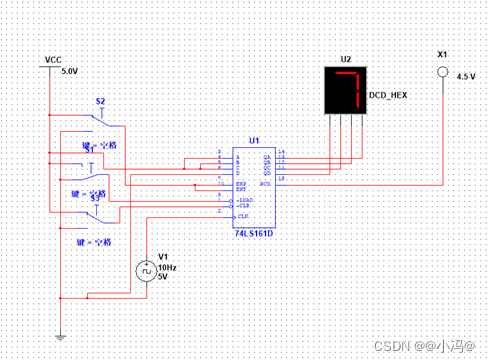

1、 熟悉仿真软件Multisim 2011的基本用法; 2、 熟悉和掌握计数器的功能以及测试方法; 3、 掌握任意进制计数器的构成方法,熟悉清零法和预置法的特点,运用集成计数器构成任意N进制计数器; 4、 熟悉数码管的基本功能和使用方法。 二、 实验仪器与器件1、 计算机 2、 仿真软件Multisim 2011 三、 实验内容及步骤1、 计数器功能测试 测试计数器74LS161, 给出功能表。 启动Multisim 2011仿真系统,在电路设计窗口按照图4.1创建计数器功能测试电路。

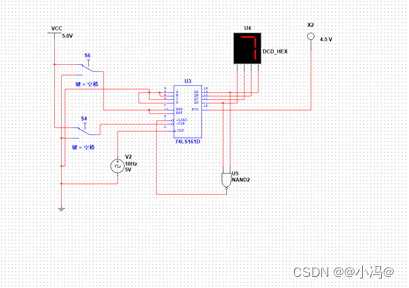

2、N进制计数器的设计 1) 采用清零法,试用74LS161构成10进制计数器,给出设计电路以及状态图。 同步清零法

图4.2.2 74LS161构成异步清零法十进制计数器 图4.2.2 74LS161构成异步清零法十进制计数器  2) 采用预置法,试用74LS161构成6进制计数器,给出设计电路以及状态图,要求预置数为0011。 2) 采用预置法,试用74LS161构成6进制计数器,给出设计电路以及状态图,要求预置数为0011。  图4.2.3 预置法74LS161构成六进制计数器 图4.2.3 预置法74LS161构成六进制计数器

比较清零法和预置法的特点; 触发器工作状态不同(1)置数法所有触发器的时钟端连在一起,即所有触发器在同一时钟作用下同步工作。 (2)清零法置数触发器不在同一时钟作用下同步工作。 时钟脉冲CP作用不同(1)置数法时钟脉冲CP控制所有触发器同步工作。 (2)清零法时钟脉冲CP只触发部分触发器,其余触发器由电路内部信号触发。 生效条件不同(1)置数法输入条件满足,等待时钟有效时刻生效。 (2)清零法与时钟无关,输入条件满足,立即生效。 四、 思考题1、 74LS161处于正常计数状态时,LOAD端和CLR端各应处于什么逻辑电平? 答:高电平 2、 同步清零和异步清零有什么不同? 同步清零就是一定要等到时钟脉冲有效(等于0或者等于1)的时候才能清零,异步清零就是不用看时钟脉冲,一置清零端就立刻能置零。 同步就是要等下一个cp信号到来时才进行反应,异步就是不受cp信号限制立即反应。 |

【本文地址】

今日新闻 |

推荐新闻 |

图4.1.1 计数器测试电路

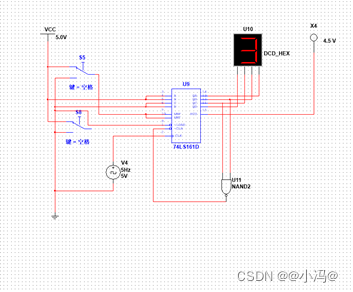

图4.1.1 计数器测试电路  图4.1.2 计数器测试电路

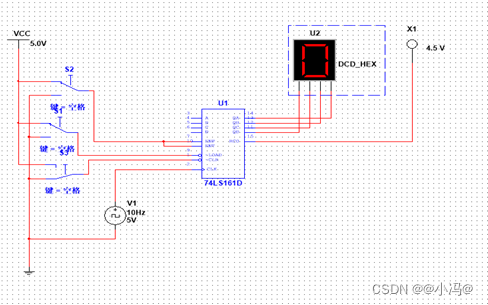

图4.1.2 计数器测试电路 图4.1.3 计数器测试电路

图4.1.3 计数器测试电路 图4.2.1 74LS161构成同步清零法十进制计数器

图4.2.1 74LS161构成同步清零法十进制计数器