光刻胶剥离工艺 |

您所在的位置:网站首页 › 光刻胶剥离工艺 › 光刻胶剥离工艺 |

光刻胶剥离工艺

|

摘要 新的全湿剥离工艺在去除高度注入的光刻胶时不需要干等离子体灰化工艺,同时保持低缺陷水平和至少相当于记录工艺的高产量性能。灰化步骤的消除减少了不希望的基板损坏和材料损失,改善了周期时间,释放了晶圆厂占地面积,并降低了资本投资和运营成本。 在 CMOS 制造中,离子注入用于修改硅衬底以满足各种带隙工程需求。通常,图案化光刻胶 (PR) 用于定义离子注入位置。离子注入后,图案化的光刻胶必须完全去除,表面必须为下一轮的图案化和离子注入做好准备。离子注入在光刻胶表面形成一层坚韧的层,使其难以去除。 常使用干式等离子体灰化去除注入的光刻胶,然后进行湿式化学清洗。离子注入工艺的三个回路——隔离(阱)回路、晶体管通道回路和晶体管结构回路——用于构建CMOS器件。仅阱环路就占总工艺层的近三分之一,在 90nm 逻辑 CMOS 制造的情况下,可能涉及超过 21 个步骤的离子注入和光刻胶剥离。因此,循环时间的任何减少都会迅速成倍增加,从而显着缩短总处理时间。 全湿光刻胶优势 已经提出了一种全湿光刻胶去除工艺,以消除等离子体引起的基板损坏的可能性并减少基板材料损失 [1, 2]。此外,消除等离子体灰化步骤显着减少了离子注入图案化周期时间,这对于代工 CMOS 制造尤其重要。 在大批量生产环境中,只有在与现有记录工艺 (POR) 的最终良率性能相匹配的情况下,采用这种全湿式光刻胶剥离工艺才是合理的。

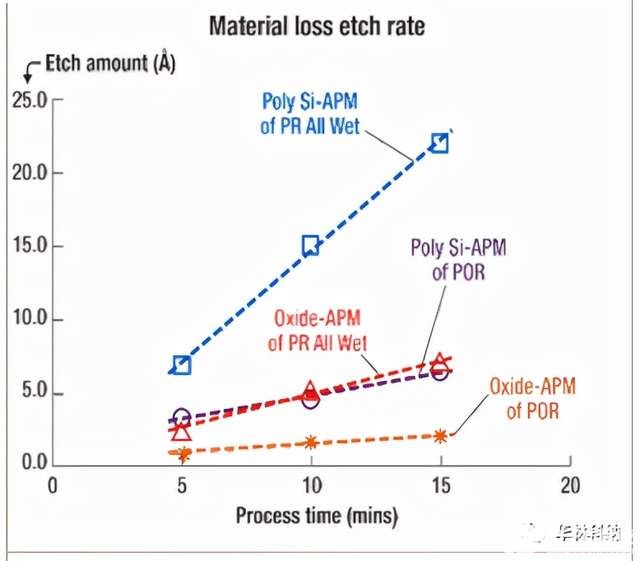

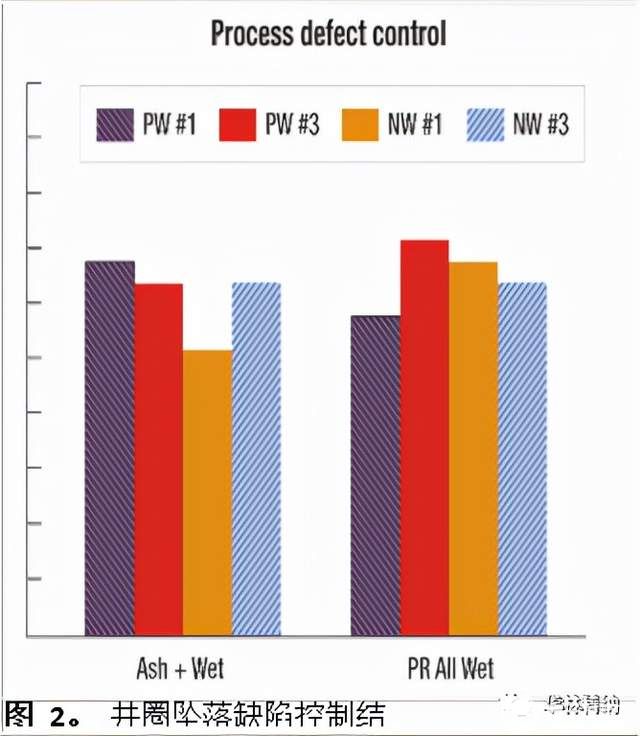

制造基线(灰化后清洁)工艺和全湿剥离工艺的蚀刻速率行为如图 1 所示。蚀刻速率数据用于设置全湿剥离工艺参数,以最大限度地减少下降缺陷控制性能,并将工艺引起的材料损失与当前器件几何形状的制造基线相匹配。在这项工作中,所有四个井回路都使用了一个使用五分钟的 SPM 暴露,然后是两分钟的 APM 暴露的过程。 处理周期时间 与 POR(灰+湿)相比,这种全湿工艺可以将每个掩模的光刻胶剥离周期时间从 70 分钟减少到大约 25 分钟——大约是 POR 基线周期时间的三分之一。考虑到井回路的七个掩模层,通过全湿光刻胶剥离的总循环时间从八小时减少到大约五小时,这使循环时间减少了 60% 以上。 产量表现基准 为了实现离子注入后光刻胶全湿剥离工艺与当前基线(灰化 + 灰化后清洁)工艺之间的批量生产比较,使用称为协调置信度的专有统计控制技术对晶圆最终良率表现。该技术在制造过程中使用逐步相同的表征,并通过各种晶圆验收测试 (WAT) 进行最终良率性能分析。 结论 已开发出一种全湿式光刻胶去除工艺,该工艺减少了工艺步骤的数量并消除了等离子体引起的基板损坏的可能性,同时还最大限度地减少了基板材料损失。正如本文详述的工艺验证实验所证明的那样,与当前的制造基线工艺(等离子灰化后湿法清洗)相比,这种剥离方法可提供等效的缺陷控制和可比的良率控制 (>99.9%)。此外,全湿法工艺证明能够将离子注入周期时间减少 60% 以上,同时将洁净室空间利用率提高 300% 以上。

审核编辑:符乾江 |

【本文地址】

今日新闻 |

推荐新闻 |