数字IC设计 |

您所在的位置:网站首页 › 做1010序列检测器的状态图 › 数字IC设计 |

数字IC设计

|

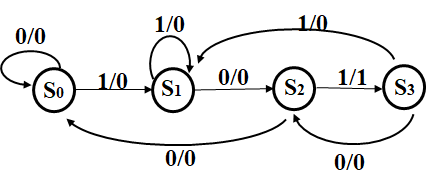

数字IC设计——用Verilog实现序列检测器(有限状态机) 序列检测器在数据通讯,雷达和遥测等领域中用与检测步识别标志。它是一种用来检测一组或多组序列信号的电路。例如检测器收到一组串行码{1110010}后,输出标志1,否则,输出0。 一、“101” 序列检测器序列检测器:有“101”序列输入时输出为1,其他输入情况下,输出为0。画出状态转移图,并用Verilog描述。 先分析输入序列时,产生的结果 序列检测器就是将一个指定序列从数字码流中识别出来。本例中将设计一个“101”序列的检测器。设X为数字码流的输入,Z为检测出标记输出,高电平表示发现指定的序列101.考虑码流为10101010101…则 时钟1234567891011输入X10101010101输出Z00101010101 将上述功能转化为状态转移图: 用Verilog语言描述状态机

module Detect_101(

input clk,

input rst_n,

input data,

output flag_101

);

parameter S0 = 0,

S1 = 1,

S2 = 2,

S3 = 3;

reg [1:0] state;

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

state 用Verilog语言描述状态机

module Detect_101(

input clk,

input rst_n,

input data,

output flag_101

);

parameter S0 = 0,

S1 = 1,

S2 = 2,

S3 = 3;

reg [1:0] state;

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

state |

【本文地址】

今日新闻 |

推荐新闻 |