锁相倍频电路的实现 |

您所在的位置:网站首页 › 倍频器电路设计 › 锁相倍频电路的实现 |

锁相倍频电路的实现

|

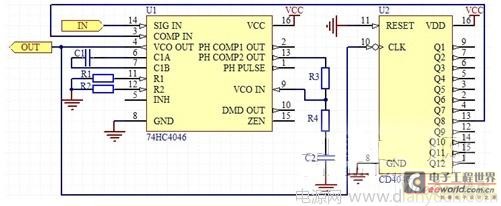

2.2 锁相倍频电路 此锁相倍频电路采用了一片锁相环芯片74HC4046、一片累加计数器CD4040和低通滤波器,其电路连接图如图3所示。

图3 锁相倍频电路原理图 A相电压经过零信号检测电路后得到与A相电压同步的50Hz方波,作为锁相倍频电路的输入信号进入锁相环芯片74HC4046的14号引脚,4 号引脚是74HC4046内部压控振荡器的输出端,其输出信号输入CD4040的10号引脚,进行256倍的倍频,其倍频信号从二进制计数器CD4040 的13号引脚输出又进入74HC4046的3号引脚,即比较信号输入端,74HC4046内部的相位比较器对两个信号进行相位比较后,从相位比较器Ⅱ的输出端13号引脚输入,经过由 、 和组成的低通滤波器,将高频噪声滤除后,再进入74HC4046的内部压控振荡器,作为其控制信号,从上述过程可以看到这是一个闭环控制系统,经过不断的调节,使输出信号频率为输入信号频率的256倍,并且使输入信号与比较信号的频差为零。 3 实验结果及分析 过零检测电路在外加信号频率为50Hz正弦波时的实验波形图如图4所示。

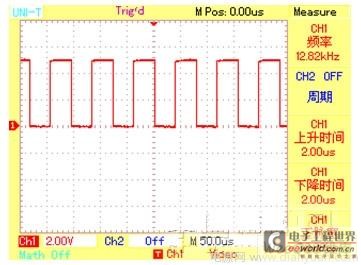

图4 过零信号与正弦波形 图5所示为所设计的锁相倍频电路的输出实验波形。

图5 锁相倍频电路输出的12.82kHz方波 压控振荡器的输入电压来自于低通滤波器的输出,所以输出频率会有一定的波动,此锁相倍频电路的输出频率范围在12.77kHz- 12.82kHz。锁相倍频电路输出的频率在被DSP捕捉到后就会启动AD7656对信号采样,由于输出频率的脉动,采样点的正弦和余弦值可能会与表中存储的正弦和余弦表有一定误差。在满足锁相速度的前提下,应当尽可能减小低通滤波器的截止频率,以减小输出频率的波动。

[1] [2] [1] [2]  关键字:倍频

编辑:冰封 引用地址:http://www.eeworld.com.cn/dygl/2011/0303/article_4798_2.html

本网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有,本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时通过电子邮件或电话通知我们,以迅速采取适当措施,避免给双方造成不必要的经济损失。

关键字:倍频

编辑:冰封 引用地址:http://www.eeworld.com.cn/dygl/2011/0303/article_4798_2.html

本网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有,本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时通过电子邮件或电话通知我们,以迅速采取适当措施,避免给双方造成不必要的经济损失。

上一篇:您的放大器偏移是否出了问题? 下一篇:EMI抑制方法分析研究  关注eeworld公众号快捷获取更多信息

关注eeworld公众号快捷获取更多信息

关注eeworld服务号享受更多官方福利

关注eeworld服务号享受更多官方福利

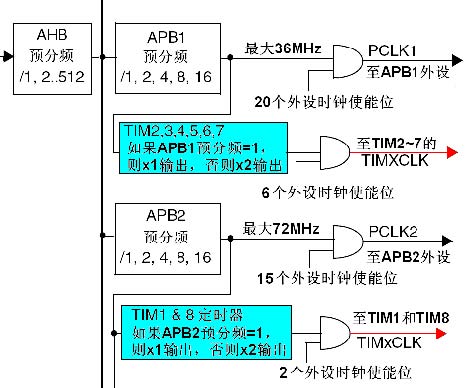

推荐阅读 STM32通用定时器基本用法DVI倍频系数 STM32的定时器是个强大的模块,定时器使用的频率也是很高的,定时器可以做一些基本的定时,还可以做PWM输出或者输入捕获功能。从系统框架图下看,名为TIMx的有八个,其中TIM1和TIM8挂在APB2总线上,而TIM2-TIM7则挂在APB1总线上。其中TIM1&TIM8称为高级控制定时器(advanced control timer).他们所在的APB2总线也比APB1总线要好。APB2可以工作在72MHz下,而APB1最大是36MHz。关于倍频系数 由上图可知,当APB1 的预分频系数为1 时,这个倍频器不起作用,定时器的时钟频率等于APB1 的频率;当APB1的预分 发表于 2018-10-07 【STM32F103攻城笔记】外部晶振HSE倍频设置系统时钟

上一篇的内部晶振的系统时钟设置已经对系统时钟进行了配置,而外部晶振的倍频只需要改变上一篇的初始化函数就可以,其他均一样!第一步:建立一个HSE倍频的初始化函数void SystemClock_Config(void) ;所以我们由上一篇文章变为:int main (void){ RCC_ClocksTypeDef RCC_Clocks; //初始化 SystemClock_Config(); //调用刚才改过的函数NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2

发表于 2018-09-01

STM3210X的外部时钟配置以及倍频的选择

系统默认的用8MHZ的时钟进行倍频得来72MHZ 注:外部时钟为8MHZ就无需改动第一步:改变外部时钟在假设外部时钟为12MHZ 那么就改为#define HSI_VALUE ((uint32_t)12000000) /*!< Value of the Internal oscillator in Hz*/第二步:改变倍频参数假设外部时钟为12MHZ 那么就改为 /* PLL configuration: PLLCLK = HSE * 6 = 72 MHz */ RCC->CFGR &= (uint32_t

发表于 2018-08-19

不用晶振,STM32内部HSI时钟的倍频使用

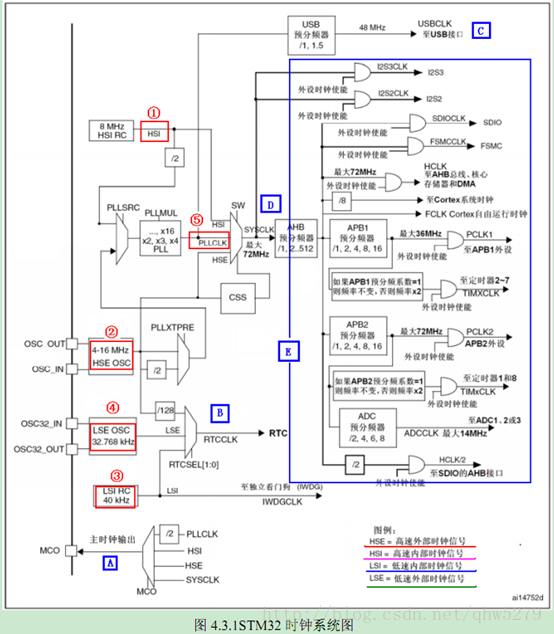

博主最近用STM32F1系列单片机做一个触摸屏USB鼠标,考虑不用外部晶振而使用STM32内部8MHz HSI RC作为时钟源。由于USB协议规定了48MHz 的USB时钟,故必须对HIS作PLL倍频处理后得到PLLCLK作为STSCLK时钟。时钟关系见如下STM32F1时钟树:类比正点原子STM32F1寄存器版本使用外部晶振的时钟初始化函数,改动得到使用HSI作为时钟源,SYSCLK为48MHz的初始化代码:void Stm32_Clock_Init(u8 PLL) { unsigned char temp=0; MYRCC_DeInit

发表于 2018-06-26

【STM32F103攻城笔记】外部晶振HSE倍频设置系统时钟

上一篇的内部晶振的系统时钟设置已经对系统时钟进行了配置,而外部晶振的倍频只需要改变上一篇的初始化函数就可以,其他均一样!第一步:建立一个HSE倍频的初始化函数void SystemClock_Config(void) ;所以我们由上一篇文章变为:int main (void){ RCC_ClocksTypeDef RCC_Clocks; //初始化 SystemClock_Config(); //调用刚才改过的函数NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2

发表于 2018-09-01

STM3210X的外部时钟配置以及倍频的选择

系统默认的用8MHZ的时钟进行倍频得来72MHZ 注:外部时钟为8MHZ就无需改动第一步:改变外部时钟在假设外部时钟为12MHZ 那么就改为#define HSI_VALUE ((uint32_t)12000000) /*!< Value of the Internal oscillator in Hz*/第二步:改变倍频参数假设外部时钟为12MHZ 那么就改为 /* PLL configuration: PLLCLK = HSE * 6 = 72 MHz */ RCC->CFGR &= (uint32_t

发表于 2018-08-19

不用晶振,STM32内部HSI时钟的倍频使用

博主最近用STM32F1系列单片机做一个触摸屏USB鼠标,考虑不用外部晶振而使用STM32内部8MHz HSI RC作为时钟源。由于USB协议规定了48MHz 的USB时钟,故必须对HIS作PLL倍频处理后得到PLLCLK作为STSCLK时钟。时钟关系见如下STM32F1时钟树:类比正点原子STM32F1寄存器版本使用外部晶振的时钟初始化函数,改动得到使用HSI作为时钟源,SYSCLK为48MHz的初始化代码:void Stm32_Clock_Init(u8 PLL) { unsigned char temp=0; MYRCC_DeInit

发表于 2018-06-26

MSP430F5438学习笔记 DCO倍频至8MHZ

1.平台说明 MS430F5438// 时钟默认情况 // FLL时钟 FLL选择 XT1 // 辅助时钟 ACLK选择 XT1 32768Hz // 主系统时钟 MCLK选择 DCOCLKDIV &n

发表于 2017-02-21

用mega8生成spwm程序(单极性倍频控制)

//ICC-AVR application builder : 2006-7-7 11:30:51

// Target : M8

// Crystal: 8.0000Mhz 20k for G4PC50U

#include

#include

#define INT0 6

//=====================周期为20ms,spwm频率为20k===========================//

short list[]={1,4,7,10,13,16,19,22,25,28,31,34,37

发表于 2016-10-29

热门资源推荐

更多

MSP430F5438学习笔记 DCO倍频至8MHZ

1.平台说明 MS430F5438// 时钟默认情况 // FLL时钟 FLL选择 XT1 // 辅助时钟 ACLK选择 XT1 32768Hz // 主系统时钟 MCLK选择 DCOCLKDIV &n

发表于 2017-02-21

用mega8生成spwm程序(单极性倍频控制)

//ICC-AVR application builder : 2006-7-7 11:30:51

// Target : M8

// Crystal: 8.0000Mhz 20k for G4PC50U

#include

#include

#define INT0 6

//=====================周期为20ms,spwm频率为20k===========================//

short list[]={1,4,7,10,13,16,19,22,25,28,31,34,37

发表于 2016-10-29

热门资源推荐

更多

半导体三极管 半导体三极管

W波段宽带倍频器的设计与仿真 W波段宽带倍频器的设计与仿真

微波高次倍频链路设计 微波高次倍频链路设计

调Q Nd∶YAG环形腔外腔倍频技术研究 调Q Nd∶YAG环形腔外腔倍频技术研究

数据结构与算法分析C++描述 数据结构与算法分析C++描述  音频功率放大器设计手册 第6版 音频功率放大器设计手册 第6版  半导体器件物理(第3版) 半导体器件物理(第3版)  电工电子技术(上) 电工电子技术(上)

|

【本文地址】