基于FPGA用VerilogHDL设计实现DDS直接频率合成的详细步骤(QuartusII调用ModelSim进行仿真详细步骤) |

您所在的位置:网站首页 › 信号发生电路设计 › 基于FPGA用VerilogHDL设计实现DDS直接频率合成的详细步骤(QuartusII调用ModelSim进行仿真详细步骤) |

基于FPGA用VerilogHDL设计实现DDS直接频率合成的详细步骤(QuartusII调用ModelSim进行仿真详细步骤)

这个时候,我们在MATLAB主界面中,右侧的workspace栏中,选中name为s的一项,双击,便可打开该数组的值,如下所示:

将该表格中的所有数据选中(可选中第一个数据,然后将进度条拉到最后一个数据的位置,按下键盘上的shift键,鼠标点击最后一个数据,便可全选了),单击右键,复制即可。然后打开execl软件,选中A1单元格,ctrl+V(粘贴),即可。

在表格中,我们会发现,这些数据是带有2位小数位的,而我们的mif文件不支持小数,因此需要将这些数据进行四舍五入。四舍五入的方法非常简单我们只需要选中行1(在数字1处点击鼠标左键即可选中),单击鼠标右键,选择设置单元格格式,如下图所示:

将该表格中的所有数据选中(可选中第一个数据,然后将进度条拉到最后一个数据的位置,按下键盘上的shift键,鼠标点击最后一个数据,便可全选了),单击右键,复制即可。然后打开execl软件,选中A1单元格,ctrl+V(粘贴),即可。

在表格中,我们会发现,这些数据是带有2位小数位的,而我们的mif文件不支持小数,因此需要将这些数据进行四舍五入。四舍五入的方法非常简单我们只需要选中行1(在数字1处点击鼠标左键即可选中),单击鼠标右键,选择设置单元格格式,如下图所示:

设置完成之后我们再看,发现表格中的数据已经全部被四舍五入了,此时的数据,就是我们可以使用的数据了。

设置完成之后我们再看,发现表格中的数据已经全部被四舍五入了,此时的数据,就是我们可以使用的数据了。

此时,我们已经完成了

mif

文件所需数据的生成工作,我们可以将这个表格文件保存,也可以直接开着,不用关闭就行,因为这个文件只是一个中转。下一步,就是将这些数据生成我们所需要用到的mif

文件了。

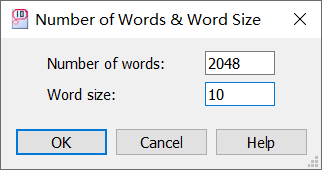

二、使用Quartus II制作mif软件

打开quartus II软件,选择file—>New,在打开的选项卡中,选择Memory Initialization File,点击OK。在弹出的mif文件大小设置选项卡中,设置Number of Words为2048,Word Size为10,点击OK

即可,详细如下所示:

此时,我们已经完成了

mif

文件所需数据的生成工作,我们可以将这个表格文件保存,也可以直接开着,不用关闭就行,因为这个文件只是一个中转。下一步,就是将这些数据生成我们所需要用到的mif

文件了。

二、使用Quartus II制作mif软件

打开quartus II软件,选择file—>New,在打开的选项卡中,选择Memory Initialization File,点击OK。在弹出的mif文件大小设置选项卡中,设置Number of Words为2048,Word Size为10,点击OK

即可,详细如下所示:

此时,就会建立好一个空白的mif文件,其中所有内容均为0,如下图所示:

三、设计DDS系统 1、module DDS module DDS( clk,//时钟 reset_n,//复位 Fword,//频率控制字 Pword,//相位控制字 DA_Data//数据输出 ); input clk; input reset_n; input [31:0] Fword; input [10:0] Pword;//Rom地址11位:横坐标最大为:2048 output [9:0] DA_Data; reg [31:0] r_Fword;//频率 寄存器 reg [10:0] r_Pword;//相位 寄存器 reg [31:0] Fcnt;//累加器 wire [10:0] rom_addr; always @(posedge clk) begin r_Fword |

【本文地址】

今日新闻 |

推荐新闻 |