使用Cadence AMS仿真器做數模混合仿真 |

您所在的位置:网站首页 › 仿真工具cadence › 使用Cadence AMS仿真器做數模混合仿真 |

使用Cadence AMS仿真器做數模混合仿真

|

使用Cadence AMS仿真器做數模混合仿真

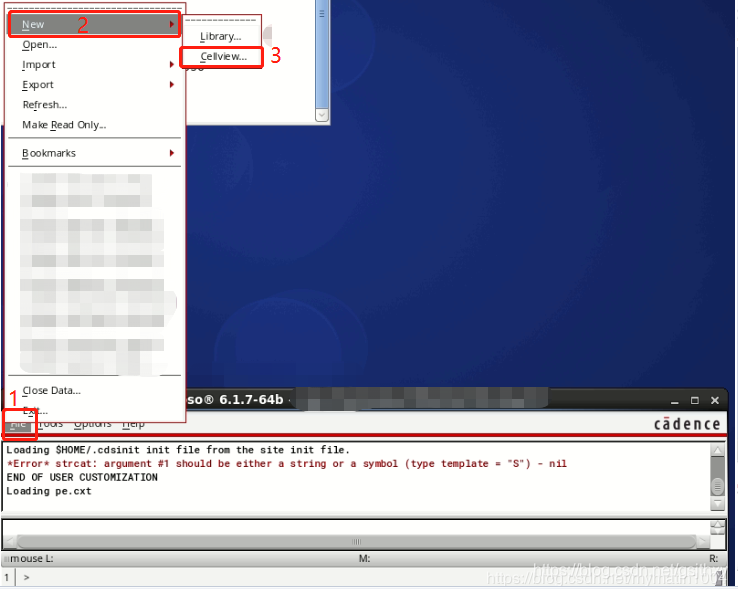

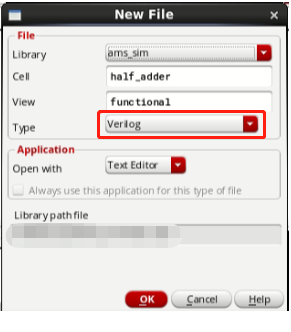

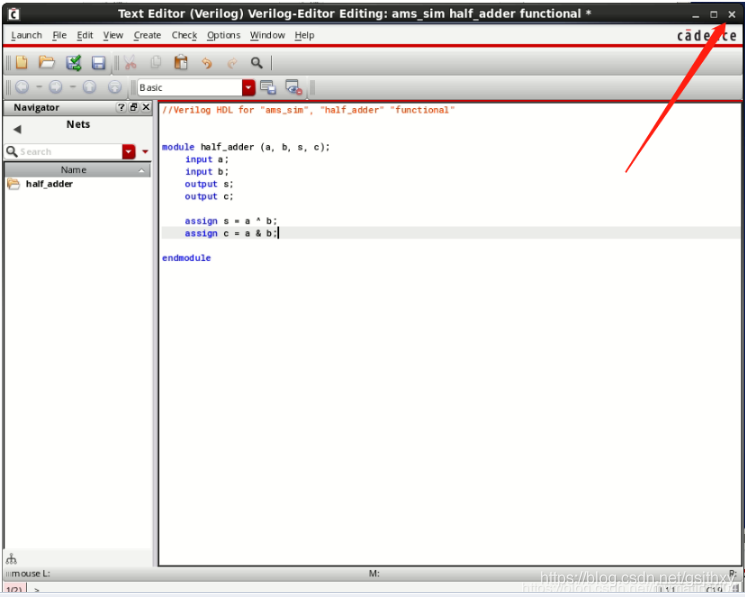

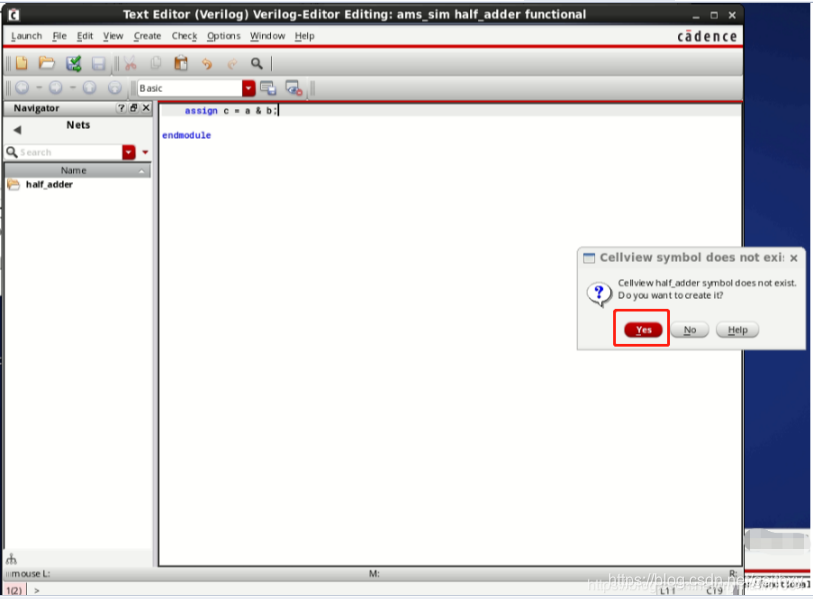

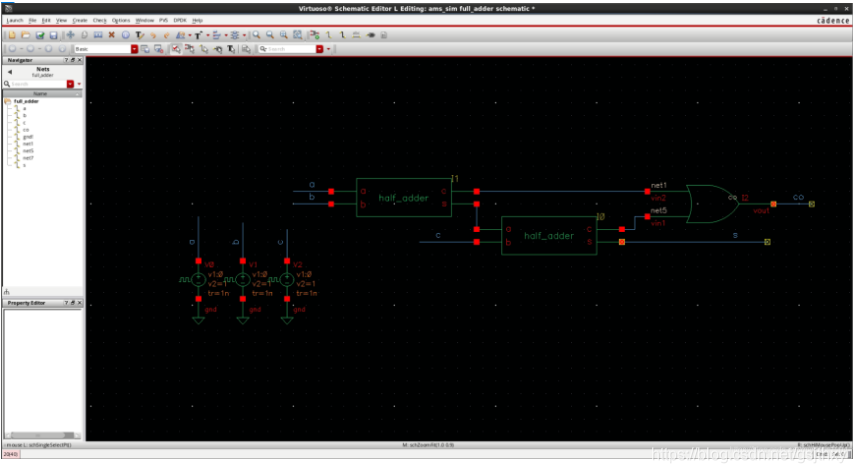

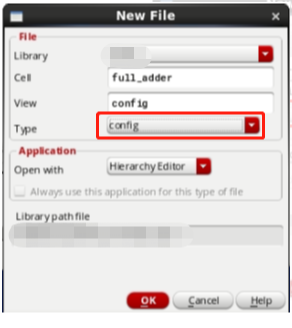

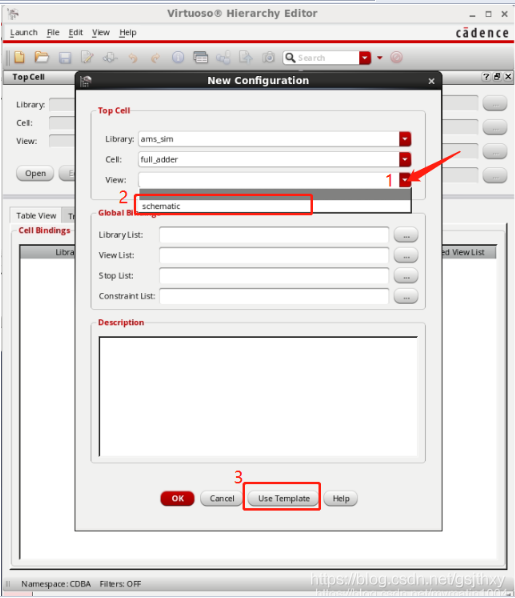

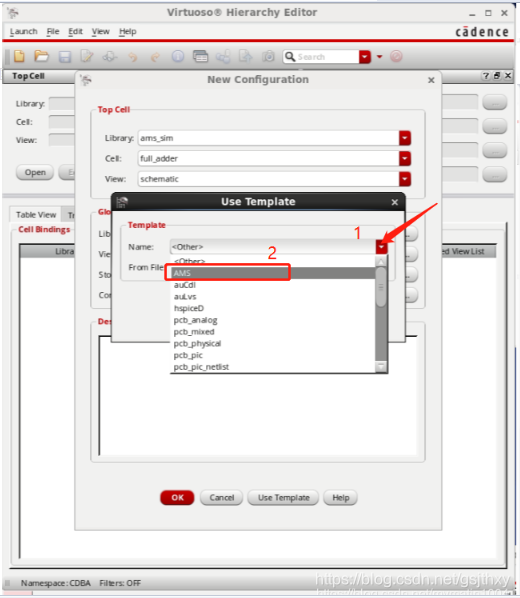

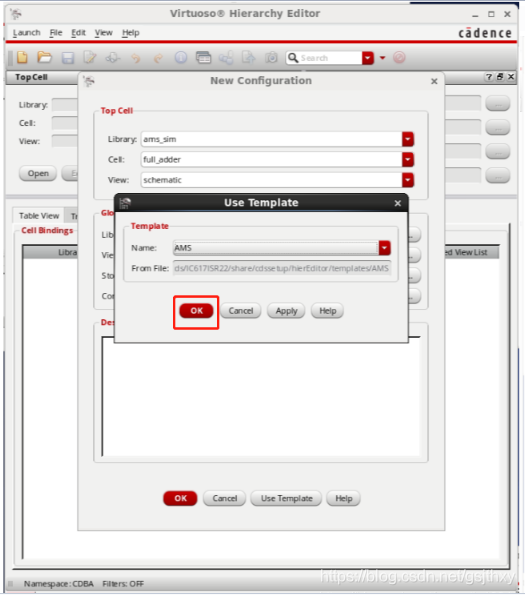

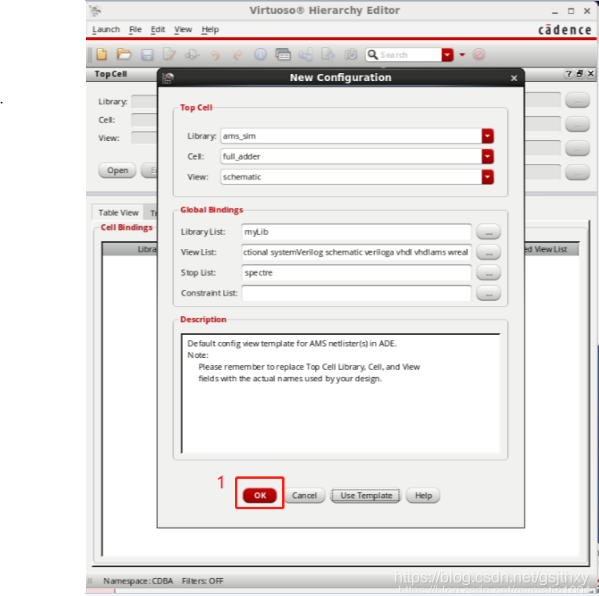

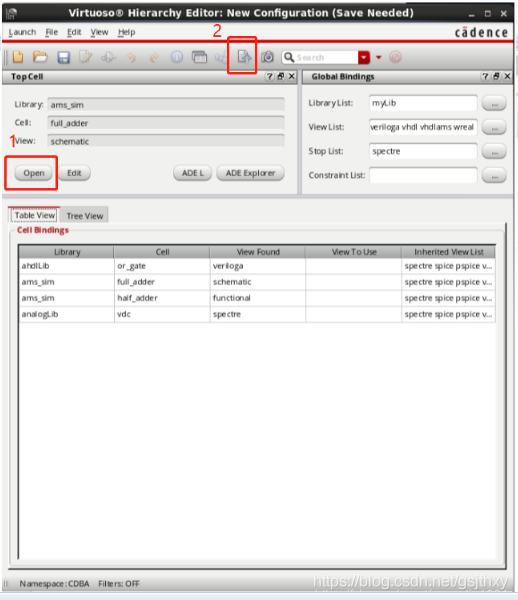

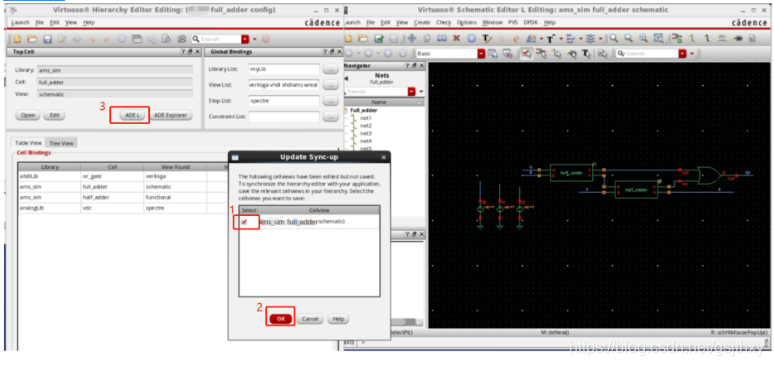

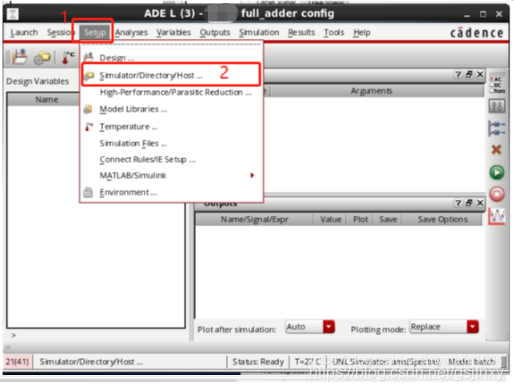

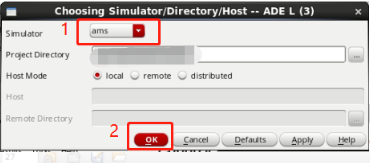

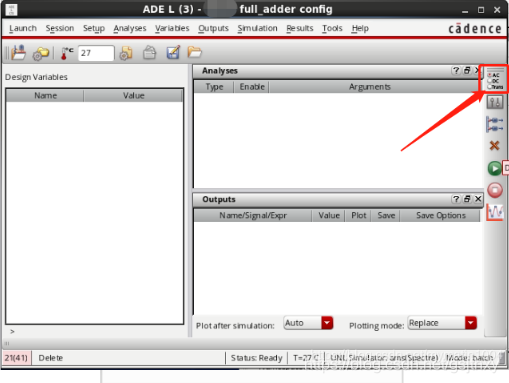

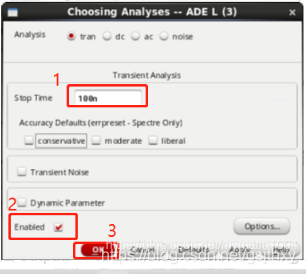

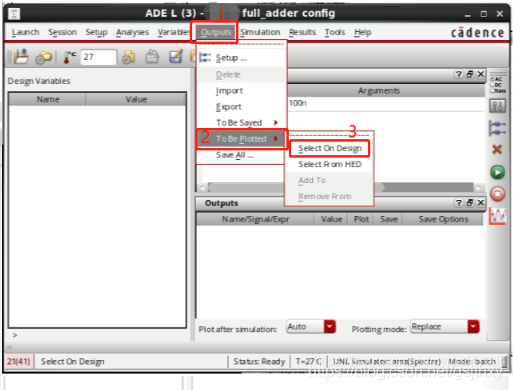

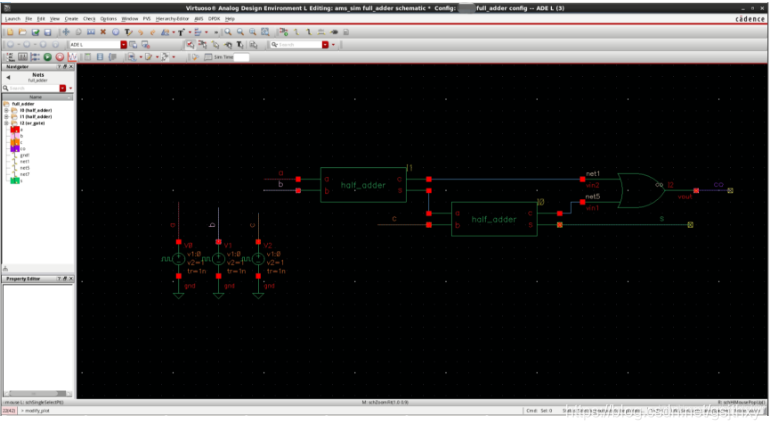

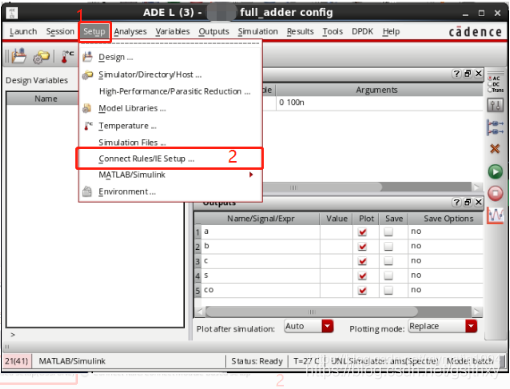

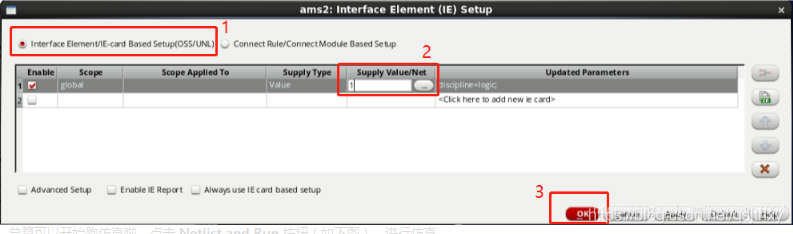

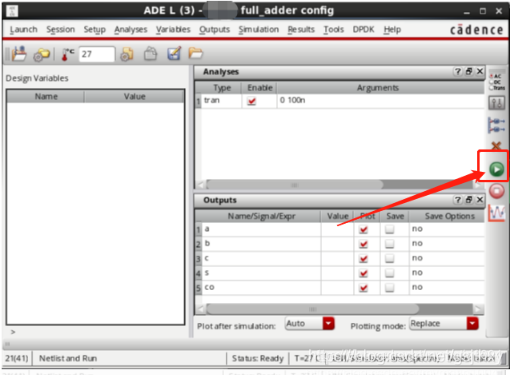

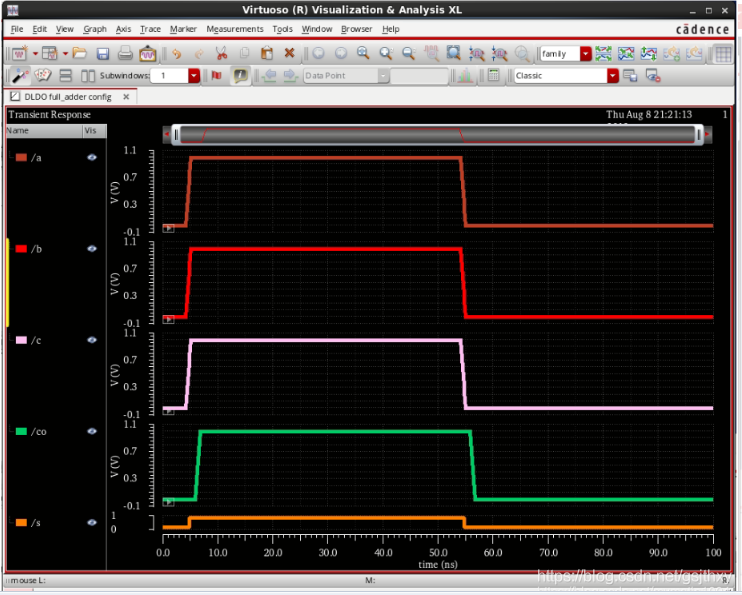

一、前言 这里是一篇关于使用 Cadence 软件通过 ams 仿真器对混合信号电路(Digital-Analog 混合电路)仿真的过程记录。由于之前在网上搜到的相关资料实在不多,因此在这里以实现一个全加器为例,复现一次混合信号电路的仿真过程。这里。为了体现混合信号仿真,这里通过 Verilog 硬件描述语言实现半加器的功能,通过外加逻辑门(模拟Analog电路) 实现整体的全加器功能。(多图预警) 1.1、本文轉自:https://blog.csdn.net/mymatin1004/article/details/98804521二、Cadence 基于ams仿真器的混合信号电路仿真 P.S.:这里假设大家曾经有一些在 Cadence 中 Analog 电路的操作经验 如: check and save : Shift + x 2.1、建立数字(Digital)模块 首先,打开软件,点击 File -> New -> Cellview 准备为我们的将由 ** Verilog** 写成的半加器新建一个 Cellview 之后会弹出新建文件的对话框,这里由于我们将使用 ** Verilog** , 因此在填好 ** Cell ** 的名字之后,记得在 ** Type** 中选择 ** Verilog**, 相应的, View 也会变成 functional 。然后点击 OK 。 接下来会弹出下面这个界面(和普通编辑器蛮像),在里面写好 Verilog 之后,先点击保存,然后点击右上角的 ** X** 来关闭窗口。 2.2、建立 Analog - Digital 混合仿真原理图 接下来开始进行混合仿真电路原理图的搭建,和建立第一个 Cellview 方法相同,不过在这里 Cell 的名字换成 full_adder 啦,然后记得 Type 这里是 schematic ,相应的 View 会变成 schematic。点击 OK 创建。 2.3、建立 Analog - Digital 混合仿真config文件 依旧是类似之前创建 Cellview 的方法,不过需要注意的是:这里在 Cell 的名字要与刚刚混合仿真的 schematic的名字相同。Type 一定要选 config。这样在 View 中也是 config。点击 OK 进行创建。 这时会弹出新的对话框(如下图),在 Name 中选择 AMS。 选好之后点击 OK。 就会发现模板看起来已经加载进来了(如下图),这时点击 OK 点击完上图中更新的按钮,可能会弹出 Update Sync-up 的对话框,这时记得打钩之后点击 OK就可以啦。接下来点击 3 那里的 "ADE L” 按钮。 可以从弹窗中看到 Simulator 是 ams,确认无误之后点击 OK 选择仿真之后想要对其绘制曲线的net。点击 Outputs -> To Be Ploted -> Select On Design 2.4、针对混合信号电路demo进行仿真 总算可以开始跑仿真啦,点击 Netlist and Run 按钮(如下图),进行仿真 最后的波形如下图所示。不得不说,这个仿真速度确实不是很快,尤其当电路规模较大的时候 三、展望 到此,本过程记录结束,希望能帮到像我之前一样各处找教程、资料,不断试错摸索中的人们。

|

【本文地址】

今日新闻 |

推荐新闻 |