一个时钟周期执行一条指令的过程理解(单周期CPU) |

您所在的位置:网站首页 › 什么是指令周期,cpu周期和时钟脉冲周期 › 一个时钟周期执行一条指令的过程理解(单周期CPU) |

一个时钟周期执行一条指令的过程理解(单周期CPU)

|

引言

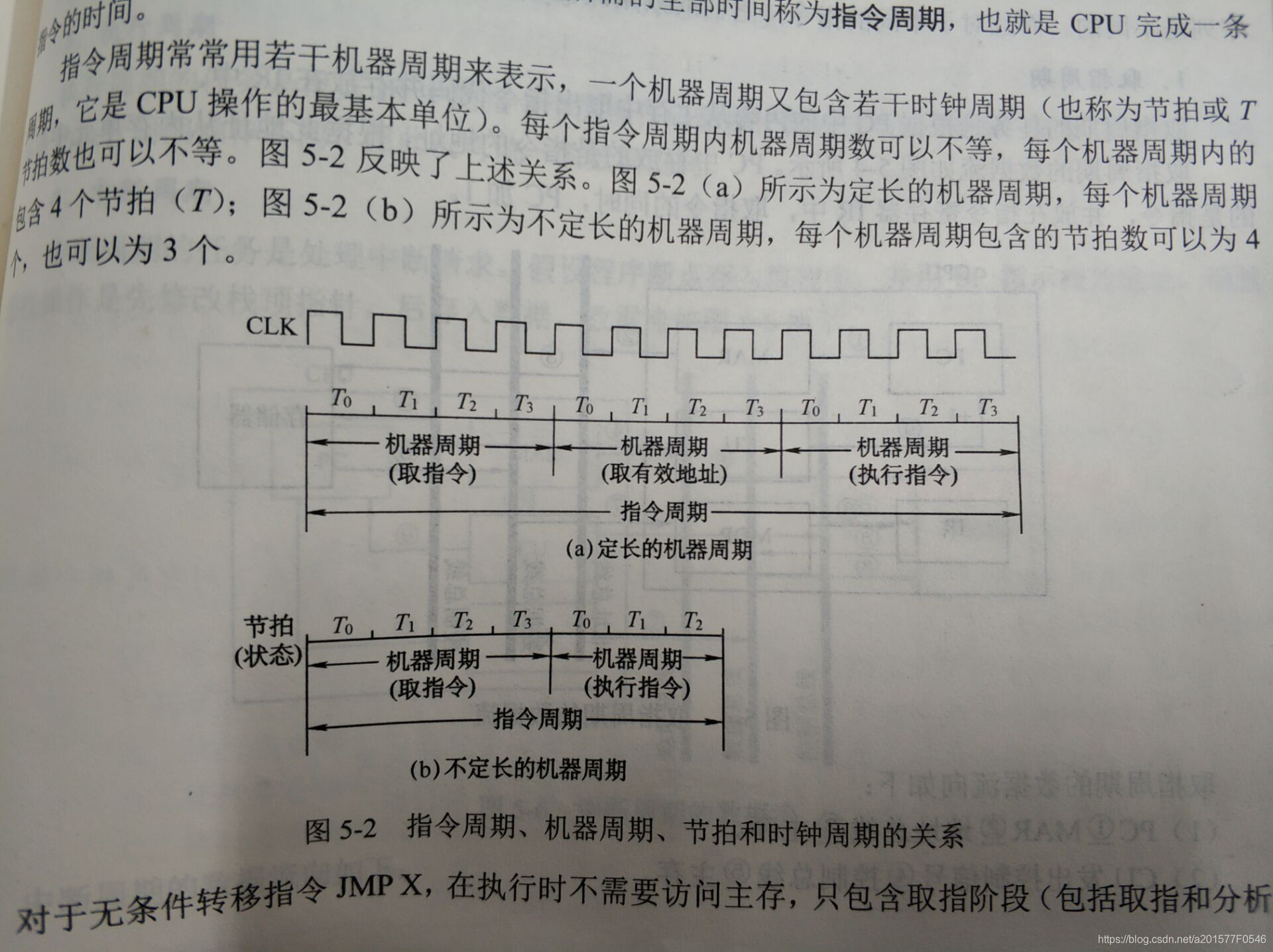

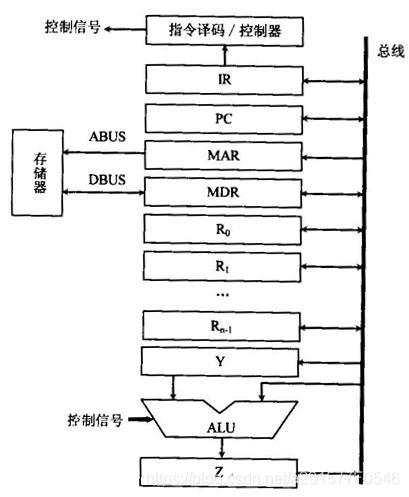

离2019考研只剩19天不到了,回顾专业课的时候又发现了一些不明白的地方,我觉得有必要把想通的思路整理记录下来。万一·····二战的时候还能用得着呢? 教材的指令系统那一章是这样告诉我的:指令有指令周期,分取指周期(IF)和执行周期(EX),这两个大的周期内部又有很多微操作,比如PC送MAR,PC+1等等这种,一个微操作至少一个时钟周期,图画的明明白白解释的很清楚。 首先要知道单周期处理器只是CPU一种实现方式,并且由于效率太低,现代设计中并不采用这种方式。虽然CPI=1,但它的总体性能不好——因为时钟周期取决于执行时间最久的那条指令(一般就是取数指令),而这个时间实在是···太久了。 下面结合它的数据通路我来捋一捋: 假定所有的状态单元(图中的PC,指令存储器,数据存储器,寄存器)都是上升沿触发的,

假设现在时钟处于低电平阶段。在这段时间内可以进行读数据、地址计算等操作,但就是不能往任何状态单元里写数据。 若当前执行的指令是取数指令,那么在低电平时间段内发生的事情有: 从指令存储器取指,译码,ALU负责PC的自增(注意,现在还没有迎来上升沿,故新的PC值“堵”在了PC的写端口进不去)从寄存器堆读出基址寄存器的值ALU将基址寄存器的值与指令中进行符号拓展后的address字段(图中的指令[15-0])相加ALU的结果作为数据存储器的地址,由数据存储器读出相应数据,送往寄存器堆写数据端口(上升沿还没来,数据“堵”在外面进不去)好,现在上升沿终于到了!在它到来的那一刻,PC和寄存器的写端口同时打开!堵在外面的数据终于一拥而上! 在时钟处于高电平的期间 ,PC完成了自增,从数据存数其取出来的数据也终于写入了寄存器! 过了不久这一切都稳定了下来,下降沿如期而至,写端口咔嚓一声全部关闭··· 轮回又从新时钟周期的低电平开始···· 看,这就是一个时钟周期执行一条指令的过程,我就是这样理解的,仅供参考? 这段写的好羞耻 附注:关于单周期数据通路必须有独立的指令存储器和数据存储器的原因: 书上原话,不过我不能理解这种说法。就算是共用一个存储器又怎么了?真是想不明白 因为处理器在一个周期内只能操作每个部件一次,而在一个周期内不可能对一个单端口存储区进行两次存取 关于不能使用单总线数据通路的原因: 如果是单总线结构,那么就拿本文里的例子来说,lw取数指令需要写2次,一次是PC,一次是寄存器。如果共用一根片内总线必然需要分2次传输! 稍微解释一下:因为传给PC的值与从数据存储器取出的数据是不同的两组数据,而总线上一次只能传输其中一种,所有接到总线上的部件共享这组数据自行取用,所以为了保证数据各得其所必须分2次 这对单周期CPU来说,这就变成不可能完成的指令了。以上 |

【本文地址】

今日新闻 |

推荐新闻 |

我一直以来都认为,指令是由一系列微操作实现的,执行一个微操作至少一个时钟周期,那么执行一条指令肯定得好几个时钟周期,时钟周期需要满足执行最久的微操作,那么整个指令的执行时间就是微操作执行时间的加总。学到处理器那章之后才发现不是这样的,一个时钟周期完全可以执行一条指令!也就是单周期处理器

我一直以来都认为,指令是由一系列微操作实现的,执行一个微操作至少一个时钟周期,那么执行一条指令肯定得好几个时钟周期,时钟周期需要满足执行最久的微操作,那么整个指令的执行时间就是微操作执行时间的加总。学到处理器那章之后才发现不是这样的,一个时钟周期完全可以执行一条指令!也就是单周期处理器

一个观点:所有的状态单元写端口一直都堵着数据,然而只有上升沿来到,状态单元才开始接纳这些数据 PS:《计算机组成与设计:硬件/软件接口》 这本书很好看,图就是这里面的。

一个观点:所有的状态单元写端口一直都堵着数据,然而只有上升沿来到,状态单元才开始接纳这些数据 PS:《计算机组成与设计:硬件/软件接口》 这本书很好看,图就是这里面的。