vhdl变量除法 |

您所在的位置:网站首页 › 二进制除法余数怎么办 › vhdl变量除法 |

vhdl变量除法

|

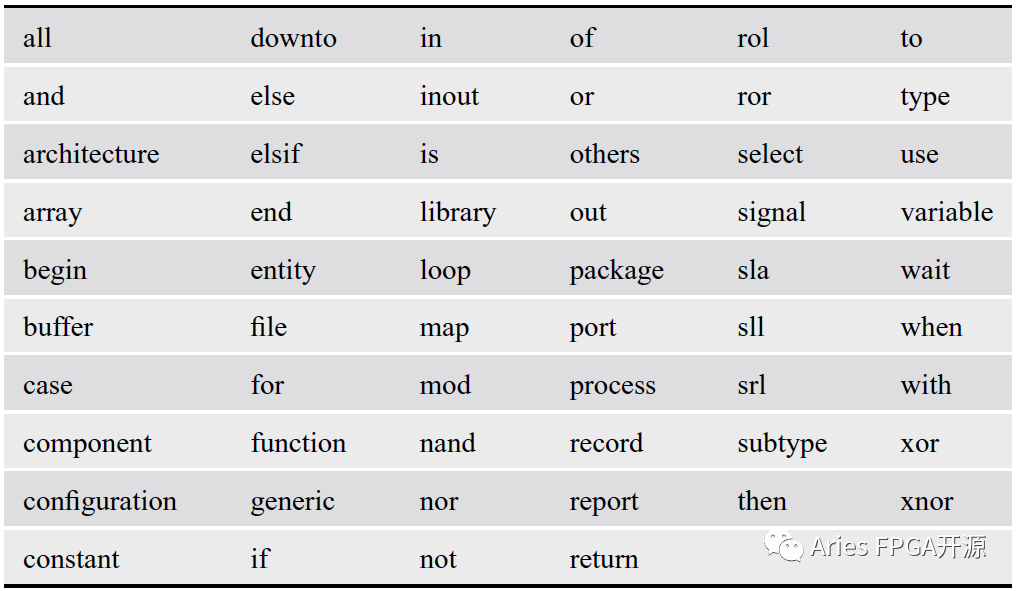

本教程使用最新的VHDL标准VHDL-2008,该标准可以提高设计人员的工作效率,并且适合用于数字设计入门课程。目前大多数编译器都支持VHDL-2008,但可能默认使用早期版本,所以在编译VHDL-2008之前,修改EDA设置。为了保持简洁准确的描述,VHDL教程使用拓展的巴科斯范式注释。尖括号内的内容为必选项,::=是“被定义为”的意思,竖线|表示任选一个,{}大括号内的内容为可重复0至无数次的项,[]内的内容为可选项。(不过不需要过度关注这些,每个讲解都带有例子) 一、注释、标识符和关键字 在VHDL中,单行注释前面带有(--)。VHDL-2008引入了多行注释,即以/*开头,以*/结束。 VHDL中的关键字和标识符不区分大小写。 标识符必须以字母开头,并且可以包含任意数量的字母、数字(0-9)和下划线。 末尾字符不能为下划线。 VHDL中定义的关键字不能作为标识符。 不允许出现两个连续的下划线。 例如: 合法标识符:Mux3、state_next 非法标识符:-Deal(起始不能为非英文字母)30Q(起始不能为数字)For(关键字不能作为标识符) VHDL-2008定义了115个关键字,相比较其它编程语言算是很多了,但在学习时,不需要学习那么多,常用的一些知道即可。 二、类型 VHDL是一种强类型语言,每一个变量在使用前都必须声明类型。下图是一些相对常用的VHDL-2008关键字。

2.1 Std_logic VHDL设计中常用的类型是std_logic。std_logic类型的信号或变量表示其值是单比特的。在电子电路中,使用电压来表示0和1的逻辑值。在VHDL规范中,这些逻辑值可以用std_logic值0或1来表示。 2.2 Boolean 逻辑比较操作的结果被预定义为boolean,与std_logic不一样的是,它的值为“真 “或”假“。当需要boolean时,VHDL-2008可以自动将一个std_logic转化为boolean类型。 2.3 Integer Integer(整数)和std_logic_vector类型不一样,它的数值范围为 Integer通常用来定义参数,比如一个多比特的std_logic_vector信号的宽度。Integer类型通常不用来存储电路计算得到的数据。Integer类型采用十进制书写方式,使用数字0-9。例如,数值100就写成100(不需要加引号) 2.4 Std_logic_vector VHDL使用std_logic_vector类型来表示多比特信号,它由std_logic构成的数组。要完全指定std_logic_vector类型,必须包含索引范围。 例如:std_logic_vector(2 downto 0)是一个3比特std_logic_vector,索引值是从2到0。 2.5 子类型 |

【本文地址】

今日新闻 |

推荐新闻 |