JK latch JK触发器 【数字电路】 |

您所在的位置:网站首页 › 上升沿和下降沿触发的d触发器逻辑符号 › JK latch JK触发器 【数字电路】 |

JK latch JK触发器 【数字电路】

|

JK latch

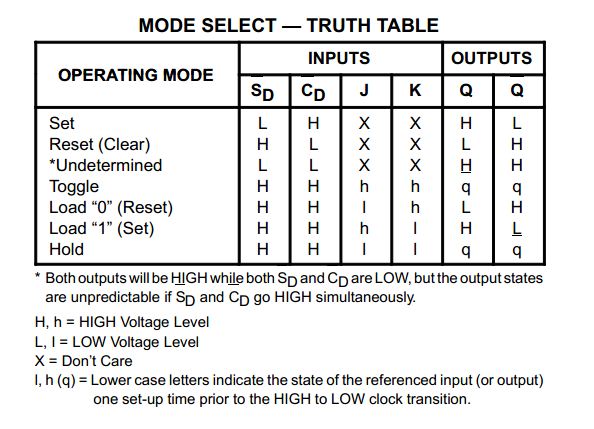

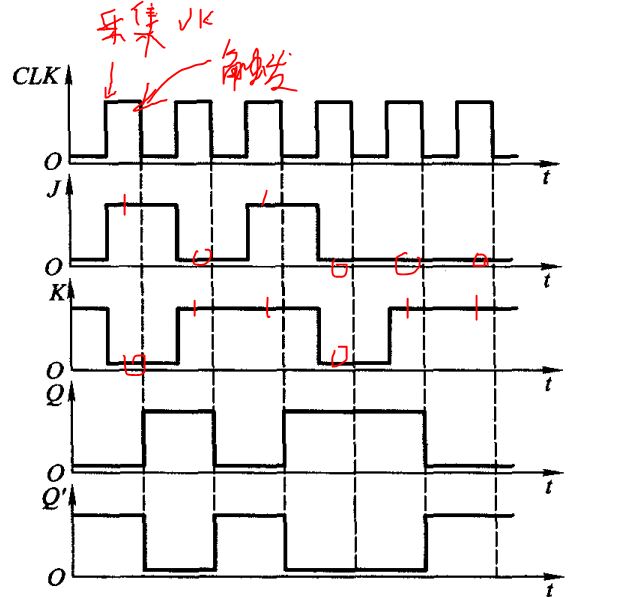

JK触发器 74LS112的实验note JK和SR比较起来,区别就在于JK多了一个操作——toggle。当JK是1 1 时,输出状态翻转。 切记!JK是主从触发器,上升沿读取JK的状态,下降沿触发! 不然下面这个时序图是觉得很矛盾,觉得矛盾就是应为没有理解JK的实际工作方式。下降沿触发的时候是和JK的状态无关的 曾哥的解释(我觉得不能再细致了,一开始很懵,后来明白了就是爽!): 对于这个的时序,当CP第一个上升延到来时候,住触发器根据jk=10,置主触发器输出为Qm=1,但CLK=1期间,主触发器是可变的,当jk=00时候,由于是保持态,所以主触发器保持为Qm=1,当下降沿到来,主触发器锁存,从触发器Q=Qm=1,期间JK的变化不影响主触发器也不影响从触发器,当上升沿再次到来,此时从触发器锁存保持Q=Qm=1不变,但主触发器根据jk=00和Q=1,保持Qm=1,但是在第二个CLK=1期间,有一段jk=01,则Qm=0,之后jk=00,保持Qm=0,所以在第二个下降沿的时候,Q=Qm=0(输出最近一次主触发器的值)。后面的以此类推。 update:2014.06.02

“切记!JK是主从触发器,上升沿读取JK的状态,下降沿触发!” 这句话其实是有问题的,我毛毛躁躁,习惯的去关注JK的状态,而忽略了,Q的输出,其实是和Q也有关系的(翻转)。曾哥建议改成: “上升沿时读取JK和Q的状态,但在CLK期间主触发器会对这些输入电平保持敏感。” |

【本文地址】

今日新闻 |

推荐新闻 |

谢谢曾哥的指导。。。指出有有严谨的地方。

谢谢曾哥的指导。。。指出有有严谨的地方。