计算机组成原理实验1 |

您所在的位置:网站首页 › 三个d触发器构成的寄存器 › 计算机组成原理实验1 |

计算机组成原理实验1

|

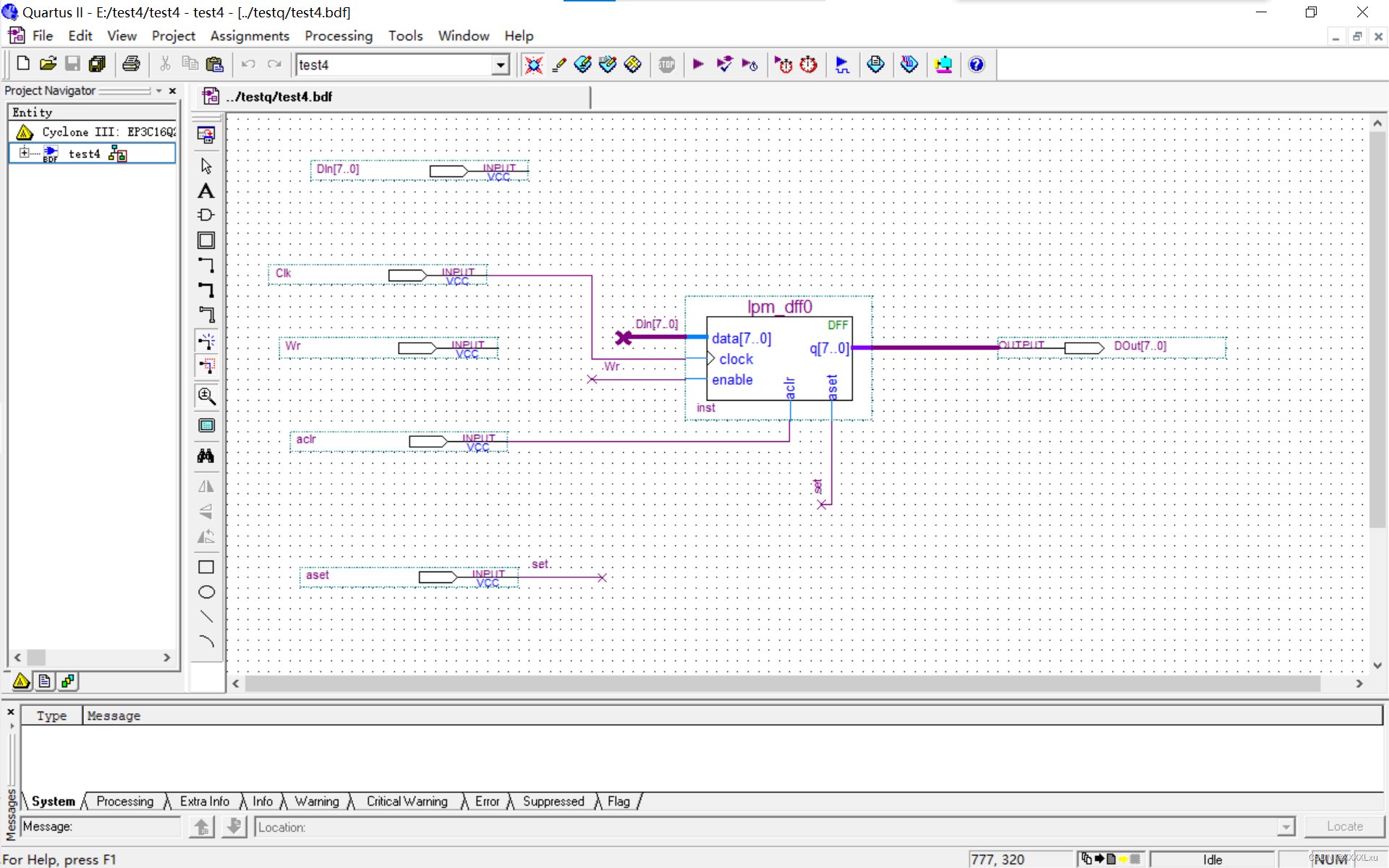

实验一 寄存器组的设计 叠甲:本人三本985大二差生,什么都不会,文章都是自己的学习记录,没有任何参考价值,难免有不少错误,请大家轻点喷。 注:实验的quartus实现可联系我提供,实验报告中原理和实现过程已经很清晰,自己实现对学习更有帮助。 一、实验内容 (1)测试D触发器的功能。 (2)设计具有1个读端口、1个写端口的4×8位寄存器组,并验证设计正确性。 二、电路设计与实现 (提示:主要包括需求分析、模块划分、引脚组织,以及器件选择、信号命名及电路组成,注意描述分析与设计的过程) 第一部分:D触发器功能的测试 需求分析触发器功能的测试包括电路实现、电路仿真及结果分析几个步骤,仿真时先采用功能仿真方式得到结果并分析,再采用时序仿真方式模拟时序的仿真结果。 引脚组织及命名电路由1个lpm_dff,输入引脚Din[7..0]、Clk、Wr、aclr、aset,输出引脚Dout[7..0]构成。 器件选择Lpm_dff一个,input引脚,output引脚。 电路组成

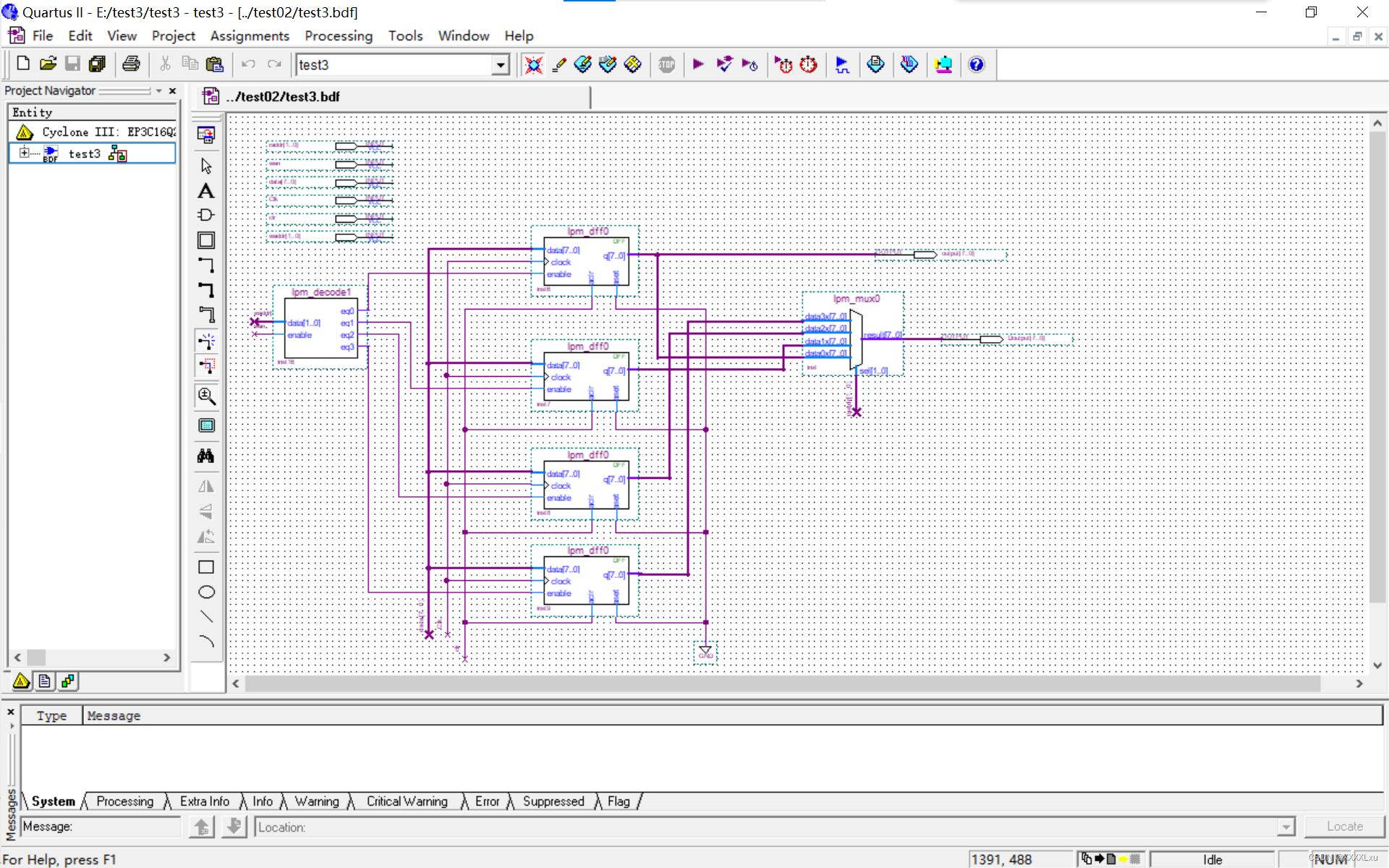

第二部分:寄存器组的设计、实现及验证 需求分析 由于寄存器组包含4个8位寄存器,故操作时的地址引脚为log24=2位、数据引脚为8位。由于要求读/写端口分离,寄存器所存信息的读出无需信号控制,故寄存器组可同时进行读、写操作。 模块划分寄存器组大致分为三个模块:写地址、数据的输入、数据的输出。 引脚组织读操作相关引脚为地址引脚raddr[1..0]、数据输出引脚q[7..0],写操作相关引脚为地址引脚waddr[1..0]、数据输入引脚data[7..0]、写使能引脚wen、时钟脉冲引脚Clk,清零操作相关引脚为清零引脚Clr。 器件选择Input引脚若干,output引脚一个,lpm_decode译码器一个,lpm_dff触发器4个,lpm_mux数据选择器一个。 分析与设计过程在写操作中,通过waddr[1..0]译码来选择寄存器,通过wen、Clk实现写入控制。将4个D触发器的数据信号端相连,作为数据输入阶段的输入信号。在读操作通过raddr[1..0]选择目标寄存器。数据输出的选择可使用选择器来实现;清零操作通过Clr来控制。 (6)电路组成

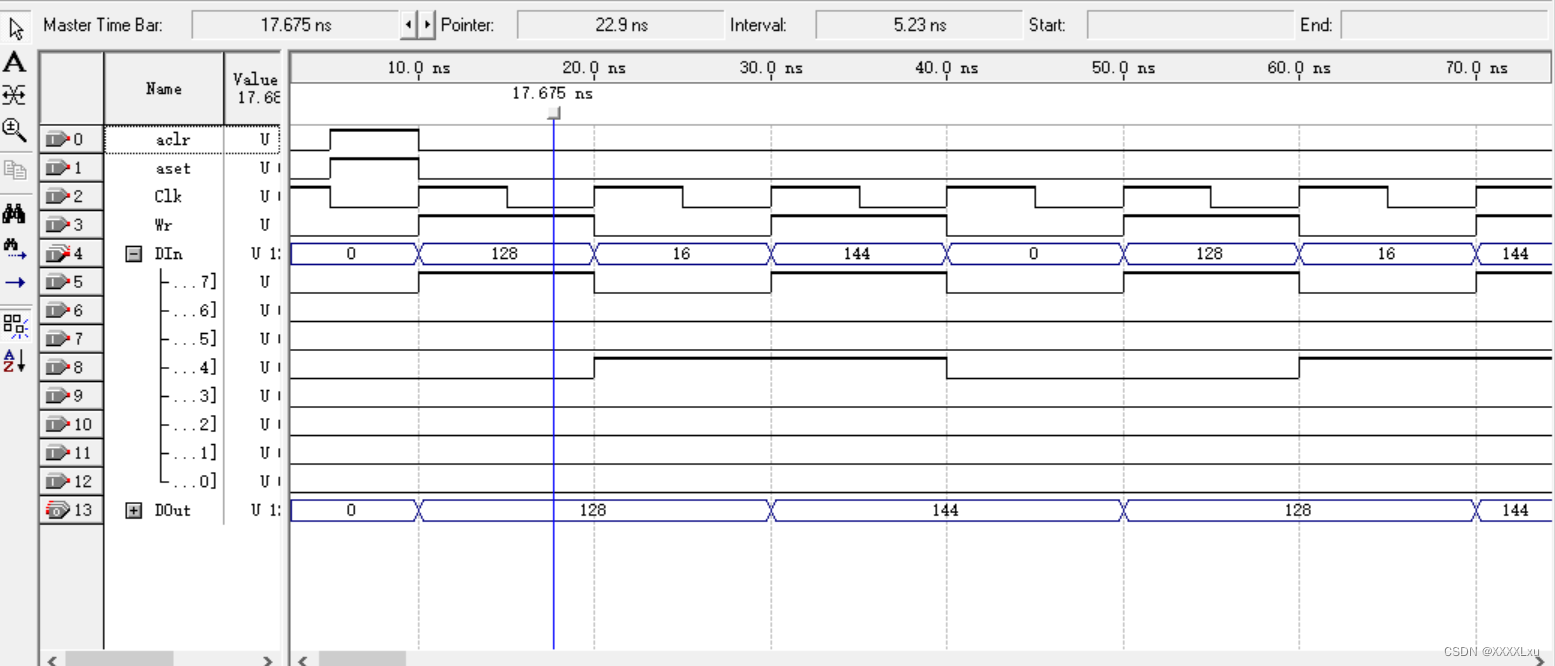

三、电路正确性验证 1、电路仿真 第一部分:D触发器功能的测试(提示:主要包括测试数据组织[应可枚举所有功能、输出结果]、仿真结果)

加入10ns的时钟信号,预先设置几个Din的值,当Wr为高电平是并遇到CLK上升时,Dout读出结果 (2)第二部分:寄存器组的设计、实现及验证

在时钟0~10ns中,wen为低电平,未写入,结果为0; 在时钟10~40ns中,wen为高电平,raddr为0,此时第0个触发器写入的是0,故结果为0; 在时钟40~55ns时,wen为高电平,raddr为1,此时第1个触发器写入的时1,结果为1; 在到了时钟上升沿时,写入数据变为5,第一个寄存器存储结果变为5,结果为5; 2、结果分析 (提示:主要包括测试数据的预期结果计算、与仿真结果的一致性比较,不一致的原因[需真实反映各种错误(如计算错误/数据错误/原理理解错误等)]) 第一部分:D触发器功能的测试D触发器功能正常。 第二部分:寄存器组的设计、实现及验证成功完成寄存器组的设计、实现及验证。 四、实验小结 (提示:主要包括工作分工、设计总结、有待改进之处、实验体会) (1)本次实验由一人小组独立完成。 (2)由于第二组实验中数据第一次设置的不合理,在助教姐姐的提醒下,发现赋值不能体现出2,4号寄存器的作用,重新进行了数据赋值,考虑不全面。 (3)本次实验作为第一次实验,内容比较简单,更多的让自己再次熟悉了quartus的操作,以及对于电路图的符号化处理以实现复用环节,实验较为成功。 |

【本文地址】

今日新闻 |

推荐新闻 |