【Modelsim零基础入门】新建项目+运行第一个verilog仿真程序:一位加法器 |

您所在的位置:网站首页 › 一加手机运行代码 › 【Modelsim零基础入门】新建项目+运行第一个verilog仿真程序:一位加法器 |

【Modelsim零基础入门】新建项目+运行第一个verilog仿真程序:一位加法器

|

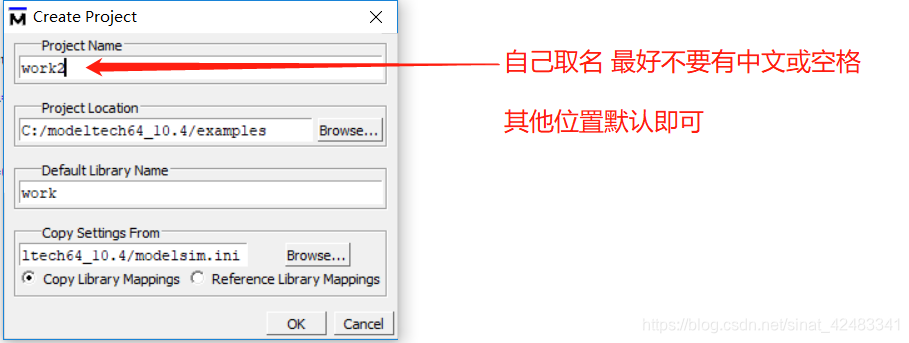

本篇注释比较详细,由《Moselsim 第一个仿真程序 四位加法器》修改而来 原博客:https://blog.csdn.net/sinat_42483341/article/details/88970852 新建项目步骤:1、File->New->Project 箭头中标注了一些常用的功能,至此,仿真教程结束。

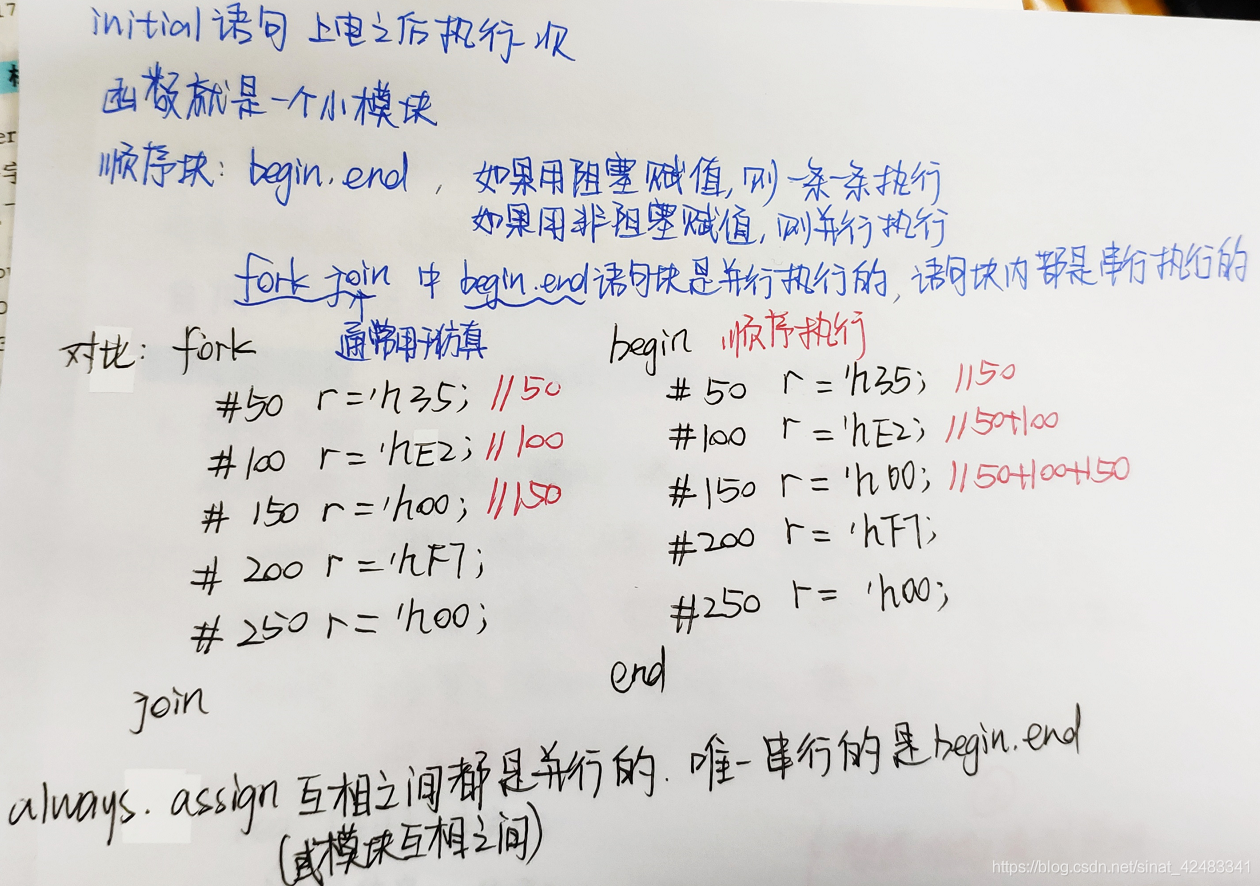

源程序 //source program module myadd(sum,cout,a,b,cin); //output,output,input,input input a,b; //I change a from 4-bit to 1-bit input cin; output cout; output sum; //I change sum from 4-bit to 1-bit assign {count,sum} = a+b+cin; //to always give value endmodule仿真程序 //Simulation program `timescale 1ns/1ns `include "MyFirstVerilog.v" module myadd_tb; //测试模块的名字 reg a,b; //测试输入信号定义为 reg 型 reg cin; //测试输入信号进位设置为 reg 型 wire sum; //测试输出信号定义为 wire 型 wire cout; //测试输出信号进位定义为 wire 型 integer i,j; myadd adder(sum,cout,a,b,cin); //调用测试对象(实例化) always #5 cin=~cin;//每5ns对cin进行一次取反 //赋值 initial begin a=0;b=0;cin=0; #10 a |

【本文地址】

今日新闻 |

推荐新闻 |

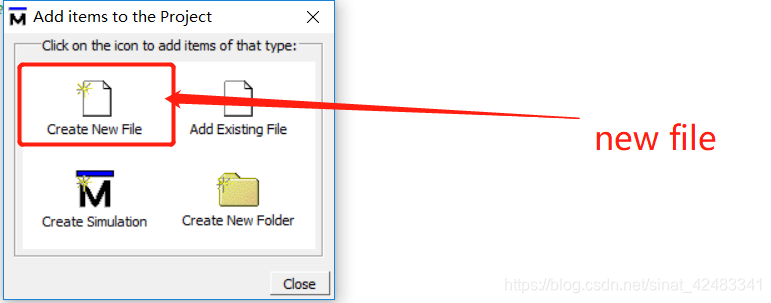

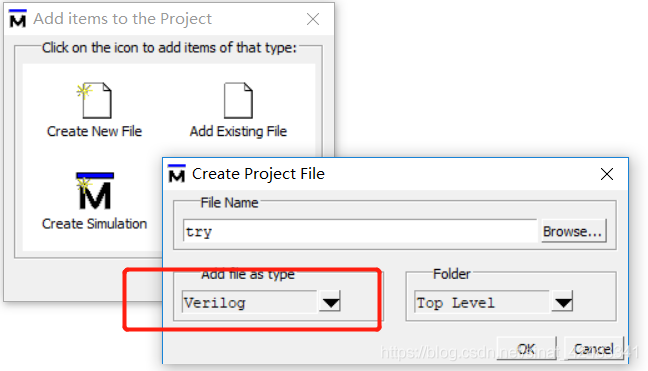

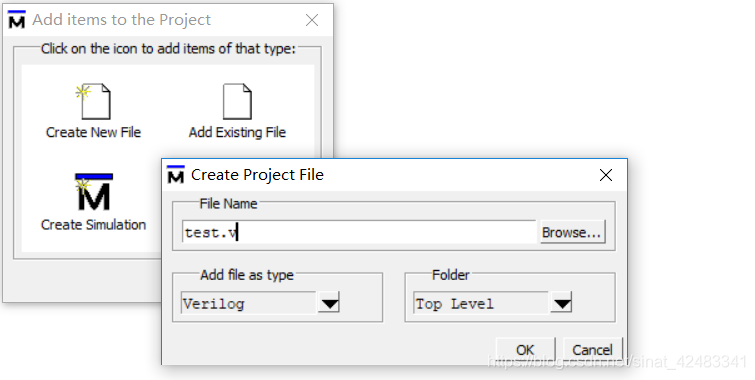

分别创建两个verilog文件

分别创建两个verilog文件

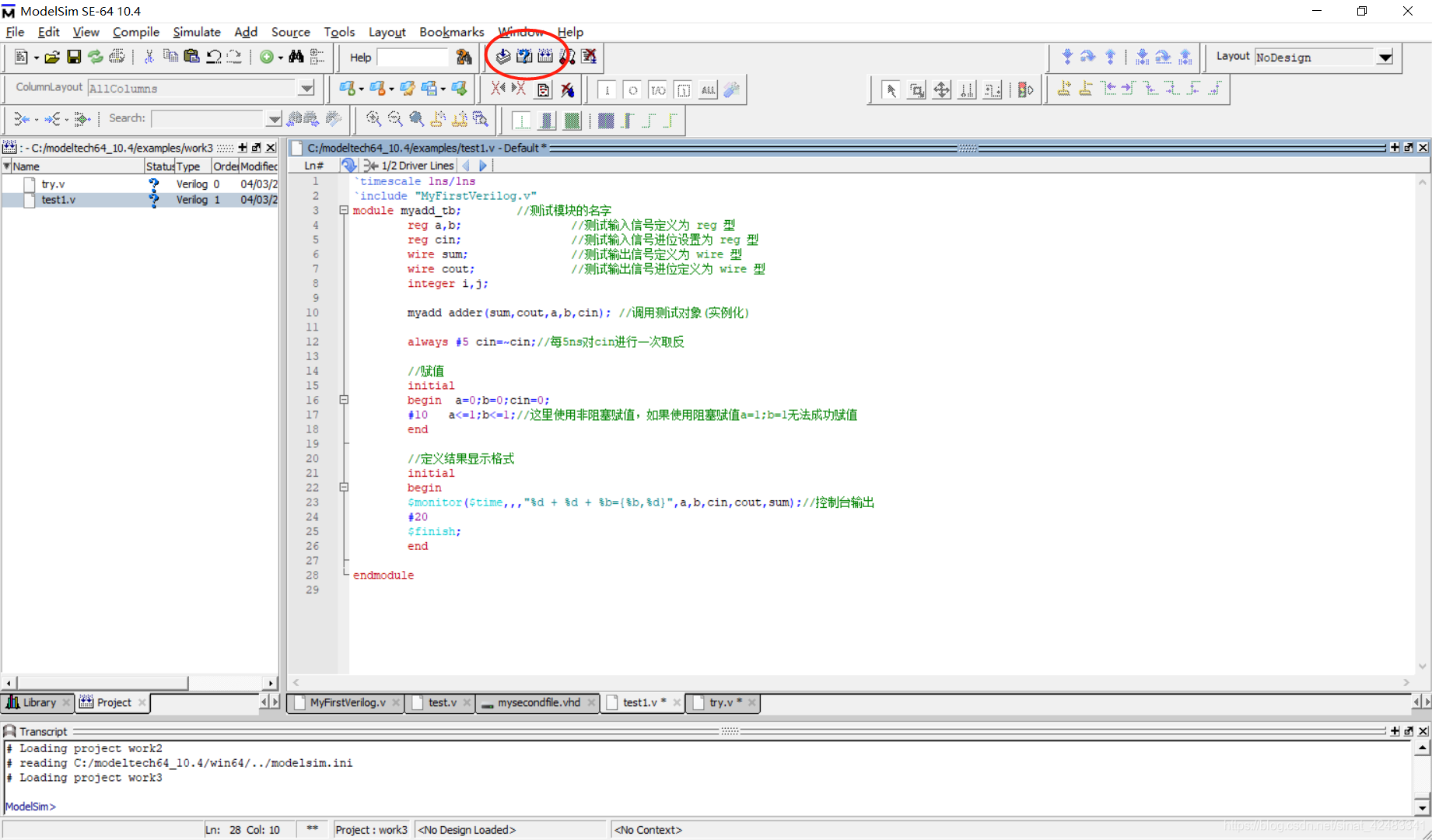

填写代码(可以复制这篇下面的源程序),保存后编译全部

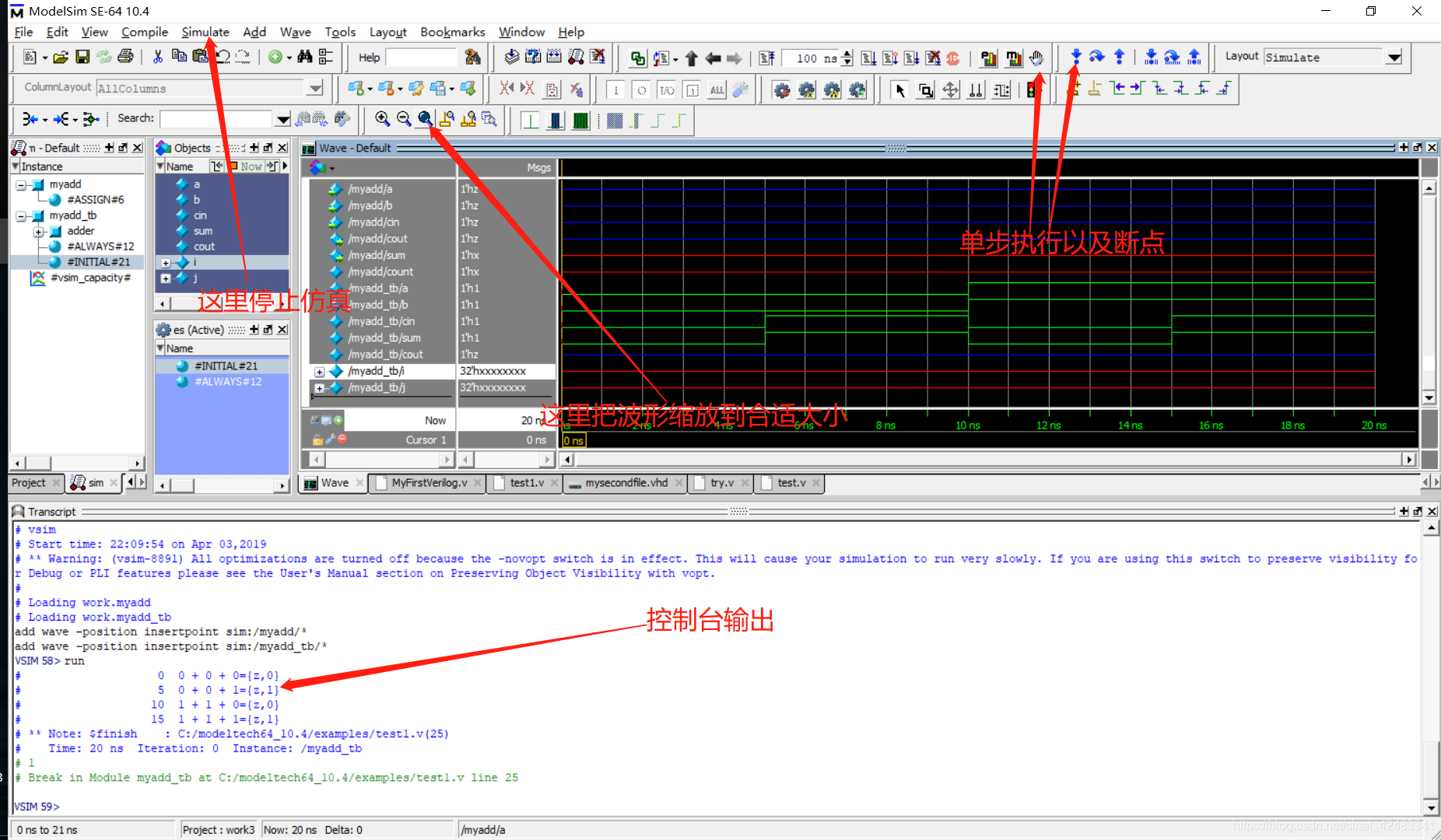

填写代码(可以复制这篇下面的源程序),保存后编译全部  下面这个控制台输出说明没有bug,如果有bug,双击错误信息,会定位到错误所在行

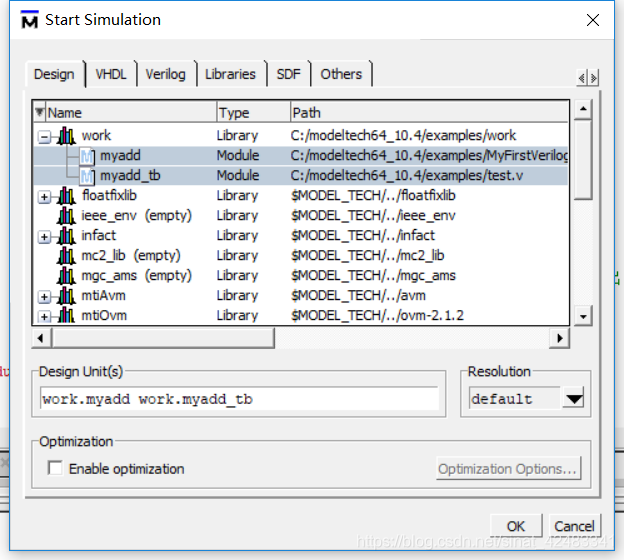

下面这个控制台输出说明没有bug,如果有bug,双击错误信息,会定位到错误所在行  simulate->start simulation,在work下选择刚写的两个文件

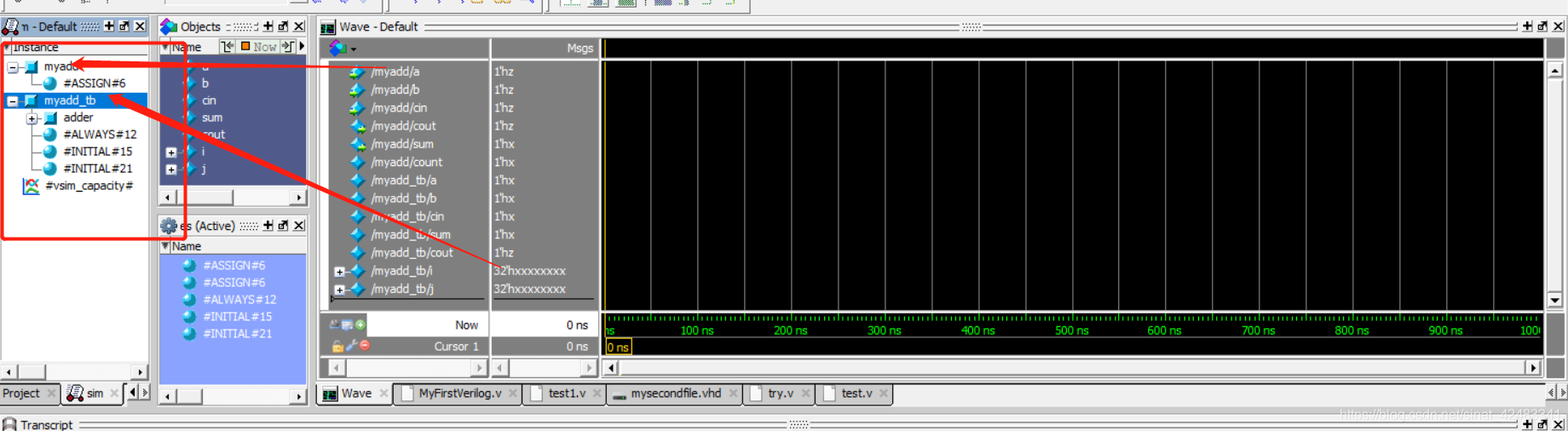

simulate->start simulation,在work下选择刚写的两个文件  右键单击这两个,分别“add wave”

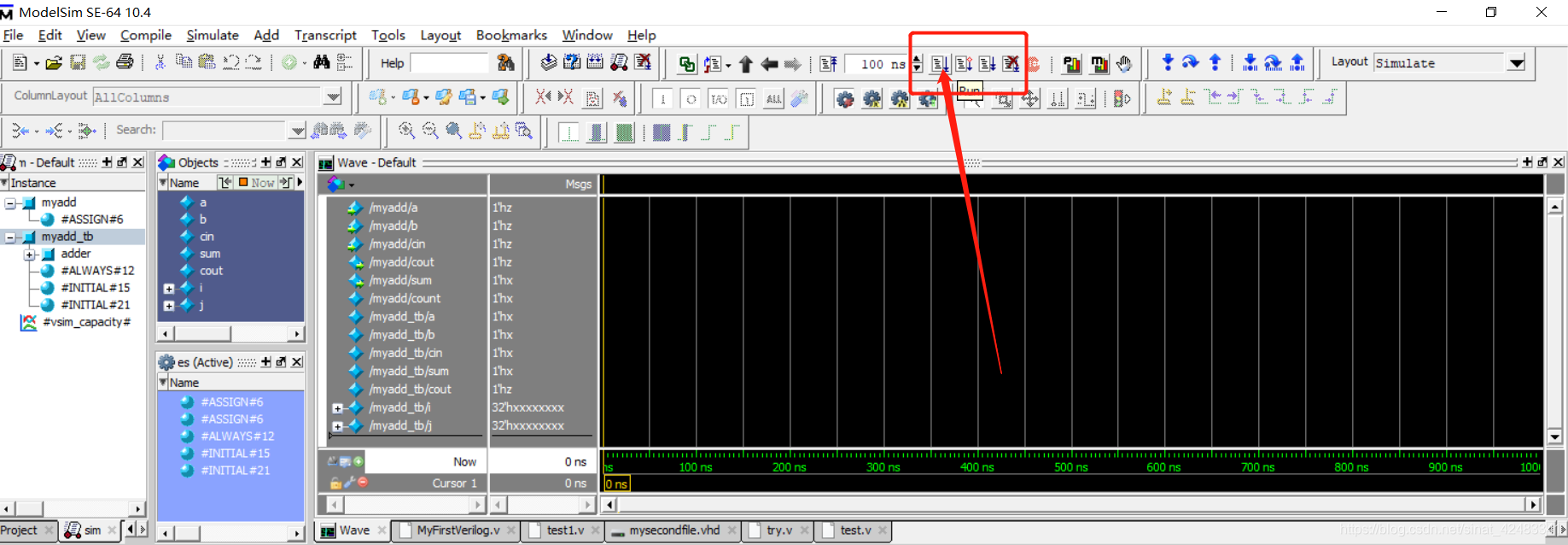

右键单击这两个,分别“add wave”  点这个run

点这个run