计组头哥实验 实验一 8位可控加减法电路设计 |

您所在的位置:网站首页 › 一加一数字歌 › 计组头哥实验 实验一 8位可控加减法电路设计 |

计组头哥实验 实验一 8位可控加减法电路设计

|

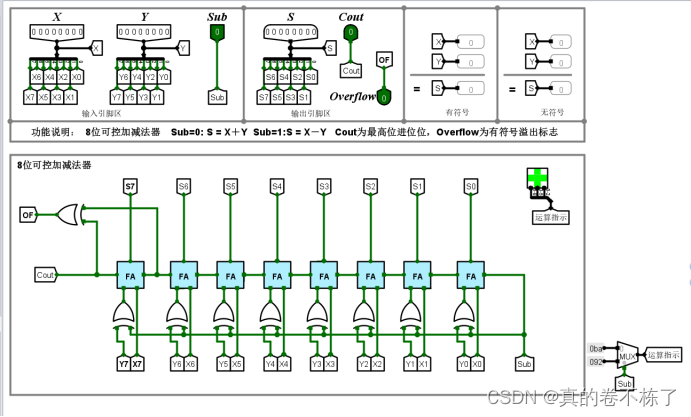

实验目的 让学生掌握1位全加器的实现逻辑,掌握多位可控加减法电路的实现逻辑;通过实验熟悉Logisim平台的基本功能,能在Logisim中实现多位可控加减法电路。 实验内容 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,其电路引脚定义如图所示,用户可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出位。 实验过程(请用简单的文字描述) 1.确定加法器和减法器的位数:根据题目要求,确定加法器和减法器的位数为8位。 2.设计加法器:采用传统的全加器设计方法,将8个全加器级联起来,形成8位加法器。 3.设计减法器:采用传统的全加器设计方法,将8个全加器级联起来,形成8位减法器。在减法器中,需要将被减数和减数取反,再将减数加1,然后将两个数相加。 4.设计控制电路:根据题目要求,设计一个控制电路,可以选择加法或减法运算。可以采用开关或按钮等控制方式。 5.搭建电路:将加法器、减法器和控制电路连接在一起,组成完整的8位可控加减法电路。 6.测试电路:使用数字信号发生器产生测试数据,通过示波器观察电路输出结果是否正确。 7.优化电路:根据测试结果,对电路进行优化,确保电路的正确性和稳定性。 8.完成实验报告:将实验过程、电路设计、测试结果和优化情况等内容整理成实验报告。 logisim平台已经给了全加器芯片,第一个要解决的问题就是如何利用全加器进行减法运算。两个数进行减法运算可以看被减数加负的减数,因此要将y转换成(-y)补之后再进行加法运算:符号位转换成1,数值位按位取反再加1。由于减法运算时sub为1,因此可以将y的各位与sub异或,同时sub作为最低为全加器的低位进位输入,以此实现上述功能。 第二个要解决的问题是溢出的判断:两个数的加减法运算可以分为以下四种情况:正+正,正+负,负+正,负+负,而溢出仅会在正+正与负+负时有可能发生。 m表示最高数值位进位,n表示符号位进位,首先讨论一定不会发生溢出的两种情况(正+负与负+正):可以总结为10+01或10+11两种情况(高位为符号位,低位为最高数值位),可能的结果有两种:n=0,m=0和n=1,m=1。此时n异或m=0。 再讨论可能会发生溢出的两种情况。正+正:可能的情况可以概括为01+01,01+00,00+00,其中第一种情况会发生溢出(n=0,m=1,n异或m=1),后两种情况不会发生溢出(n=0,m=0,n异或m=0).负+负:两个负数相加结果应为负数,结果符号位应为1,当符结果号位为0时发生溢出,可能的情况可概括为10+10,10+11,11+11,其中前两种情况的结果符号位为0,发生溢出(n=1,m=0,n异或m=1),第三种情况符号位为1,没有发生溢出(n=1,m=1,n异或m=0)。 综合以上讨论,可以发现当符号位进位和最高位进位异或结果为1时发生溢出,异或结果为0时没有发生溢出。由此就得到了补码运算判断溢出的方法。 实验详细操作步骤或程序清单

设计分析与说明: 将8个一位全加器FA的进位链串联即可得到8位加法器,由于补码符号位也可以参与运算,所以此电路既可以用于有符号数运算,也可以用于无符号数运算,但二者在溢出检测上有一定区别,这里OF的判定以有符号数加法运算是否溢出为标准。 溢出检测:根据运算过程中,最高数据位的进位与符号位的进位位是否一致进行检测。V= Cd xor Cf。 sub = 0,执行减法操作。0和二进制数异或运算得到其本身,然后通过一位全加器FA执行加法运算。 sub = 1,执行减法操作。1和二进制数异或运算相当于对二进制数进行取反操作,然后将sub = 1,传入FA进行+1操作。(由[y]补求[-y]补,全部位取反后加一)。 高位进位的产生依赖于低位进位的输入,串行进位加法器的速度较慢。 输入:操作数1X的8位数据X7-X0,操作数2Y的八位数据Y7-Y0。最低位进位Cin,加减法控制项Sub。 输出:运算结果S的八位数据S7-S0,最高位进位Cout,有符号运算溢出判断OF。 实验步骤 打开Logisim软件,在工具栏中选择基础元件,然后将8个输入引脚拖动到电路板上。这些引脚将用于输入两个8位二进制数。 在工具栏中选择连线,将每个输入引脚连接到相应的开关上。 再次从基础元件中选择“Output”(输出),然后将8个输出引脚拖到电路板上。这些引脚将用于显示输出结果。 选择“8-bit Adder”(8位全加器)模块,并将其拖到电路板上。 将输入引脚(A和B)与8位开关连接,将输出引脚(S)与第一个8位输入端口连接。 选择“Counter”(程序计数器)模块,并将其拖到电路板上。 将计数器的“Clock”(时钟)输入连接到一个手动开关上,以便手动控制计数器的时钟信号。 将计数器的“Enable”(使能)输入连接到一个开关上,以便手动启用或禁用计数器。 将计数器的“Output”(输出)连接到8位全加器的第二个8位输入端口上。 将8个LED灯连接到全加器的输出引脚上,以显示加法运算结果。 点击工具栏中的“Simulate”按钮,然后打开开关,输入两个8位二进制数,并手动控制计数器的时钟信号和使能输入,观察LED灯的变化并记录相应的结果。 实验结果的记录与分析: x=0000 0000,y=0000 0001,sub=0;s=0000 0001,Cout=0,OF=0 x=0000 1000,y=0000 0101,sub=1;s=0000 0011,Cout=1,OF=0 x=0100 1000,y=0100 0001,sub=0;s=1000 1001,Cout=0,OF=1 x=0000 0111,y=1000 0111,sub=1;s=1000 0000,Cout=0,OF=1 分析第1个输出结果 : sub = 0 ,两个正数执行x + y操作。输出结果为s=0000 0001,没有发生溢出,最高位的进位为0。 实验结果(上传实验结果截图或者简单文字描述)

在进行实验之后,我们可以通过观察LED灯的亮暗情况来得到8位可控加减法电路的运算结果。如果LED灯全部熄灭,则说明两个输入数相加的结果为0;如果只有第一盏LED灯亮起,则说明加法运算的结果为1,以此类推,直到最后一盏LED灯亮起,表示加法运算结果为255。如果需要进行减法运算,可以将第二个8位输入数取反,然后将其与第一个输入数相加,就可以得到减法的结果。 当手动调整计数器的时钟信号和使能输入时,我们可以观察到LED灯的变化情况,从而验证电路设计的正确性。在实验过程中,我们可以对不同的输入数进行多次测试,以确保电路的稳定性和正确性。如果发现出现了错误结果,则可以通过检查电路连接和元件设置等方面进行排除故障。

疑难小结 1. 线路连接过程中遇到电路逻辑完全正确,但点路线却显示蓝色 解决方法:在电路正确的前提下,重启logism,重启后就不会出现蓝色。若仍出现蓝色的线,则需要重新检查电路。Pin使其值改变。值为1的线浅绿,0为深绿。如果多位线路传输,则为黑色。出现绿色黑色都是正常的。但是出现红色代表:布线错误,产生冲突 解复用器有一个输入、选择(定义哪个输出端输出输入数据)、输出,而译码器只有选择(选择哪个输出为1)和输出。 2.电路无法正常工作 如果LED灯不能正确地显示加减运算结果,则可能是由于元件连接不正确、计数器没有启用或时钟信号不正确等原因导致的。检查连接和设置,确保每个元件都正确连接,并且计数器已经启用并且时钟信号有足够的频率。 3.计数器无法正常工作 如果计数器无法正常工作,则可能是由于使能输入信号不正确或其他设置不正确引起的。检查计数器的输入和输出设置是否正确,并确保使能输入信号与手动开关相连。 4.部分LED灯无法正常亮起 如果只有部分LED灯无法正常亮起,则可能是由于元件损坏或者连接错误导致的。检查元件连接和元件本身是否存在故障,并确认所有元件都处于正常工作状态。 5. 加法和减法运算结果出现错误 如果加法和减法运算结果出现错误,则可能是由于输入数的二进制表示错误或者全加器模块本身存在故障引起的。检查输入二进制数的位数和格式是否正确,并重新设置全加器模块以确保其正确地执行加减运算。

|

【本文地址】