[Xilinx ZYNQ] #5 常用电平接口 |

您所在的位置:网站首页 › zynq引脚lvds电平 › [Xilinx ZYNQ] #5 常用电平接口 |

[Xilinx ZYNQ] #5 常用电平接口

|

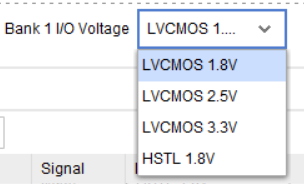

FPGA 和 ZYNQ 开发中会涉及各种电平接口,如下图 注: 可参考 UG471 -- Supported I/O Standards and Terminations 章节 LVTTL、LVCMOS总所周知,TTL 和 CMOS是数字电路中两种常见的逻辑电平,LVTTL 和 LVCMOS 是两者低电平版本。TTL 是流控器件,输入电阻小,TTL 电平器件速度快,驱动能力大,但功耗大。CMOS 是 MOS 管逻辑,为压控器件,且输入电阻极大,CMOS 电平器件速度慢,驱动能力不足 TTL,但功耗小。正是由于 CMOS 器件输入阻抗很大,外界微小的干扰就有可能引起电平的翻转,所以 CMOS 器件上未使用的输入引脚应做上下拉处理,不能浮空。 由于 TTL 和 CMOS 电平在 0 或 1 时不一样,所以需要满足 VOH (发送方) > VIH (接收方),且提供一定的噪声容限,发送方 VOL 小于接收方 VIL ,且提供一定的噪声容限。高逻辑电平驱动低逻辑电平时,可串联 50~330Ω 电阻进行电平的转换。CMOS 和 TTL 不适合高速电路原因: 1>.电平幅度较大,即使是低电平版本,摆幅也到了 3.3V 或 2.5V,因此信号变化沿所耗费的时间越长,不适合于传输频率达到 200MHz 以上的信号。2>.输出信号为单端,在传输路径上易受到干扰,不利于远距离的传输。3>.功耗较大。 与驱动能力相关的两个名词:拉电流与灌电流。 拉电流:拉电流是指电流方向为负,电流流出器件,称为拉电流,比如 IOH; 灌电流:灌电流指的是电流方向为正,电流流入器件,称为灌电流,比如 IOL; HSTLHSTL (High Speed Transceiver Logic),即 JESD8-6,是由 JEDEC (即固态技术协会,其属于 EIA 电子工业协会) 在 1995 年正式制定的一种电路逻辑标准。 HSTL 是一种技术独立的数字集成电路接口标准,为了实现电压扩展和技术独立 I/O 结构而开发的。此标准所要求的I/O结构是差分放大输入(一个输入内部关联成一个用户提供的输入参考电压,此电压用于单端输入)和使用 Vcco 的输出。所谓技术独立,实际上指用来做输入参考和输出 Vcco 的电压,与器件本身的供电电压不同。 HSTL最主要的应用是高速存储器读可。传统的慢速存储器访问时间阻碍了高速处理器的运算操作。在中频区域 (100MHz 和180MHz 之间),可供选择基于单端信号的 I/O 结构有:HSTL、GTL/GTL+、SSTL 和低压 TTL(LVTTL)。 在 180MHz 以上的范围,HSTL 标准是唯一可用的单端 I/O 接口。利用 HSTL 的速度,快速 I/O 接口明显地提高了整个系统的性能。HSTL 是高速存储器应用的 I/O 接口选择,同时也很完美地提供了驱动多个内存模块地址总线的能力。 在 HSTL 标准中,根据输出缓冲特性的不同,HSTL 被分为四种类型。其中第1、3、4类为并行终端负载,第 2 类为串行终端负载。 注:目前 DDR,QDR 等存储器件和千兆网口等都选用这种接口,它有个特点是带参考电压 ZYNQ 支持 1.8、2.5、3.3V 的 CMOS 单端模式和 1.8V 的 HSTL 差分模式 |

【本文地址】