VSCode关联VIVADO编辑Verilog |

您所在的位置:网站首页 › vscode找不到文本扩展 › VSCode关联VIVADO编辑Verilog |

VSCode关联VIVADO编辑Verilog

|

文章目录

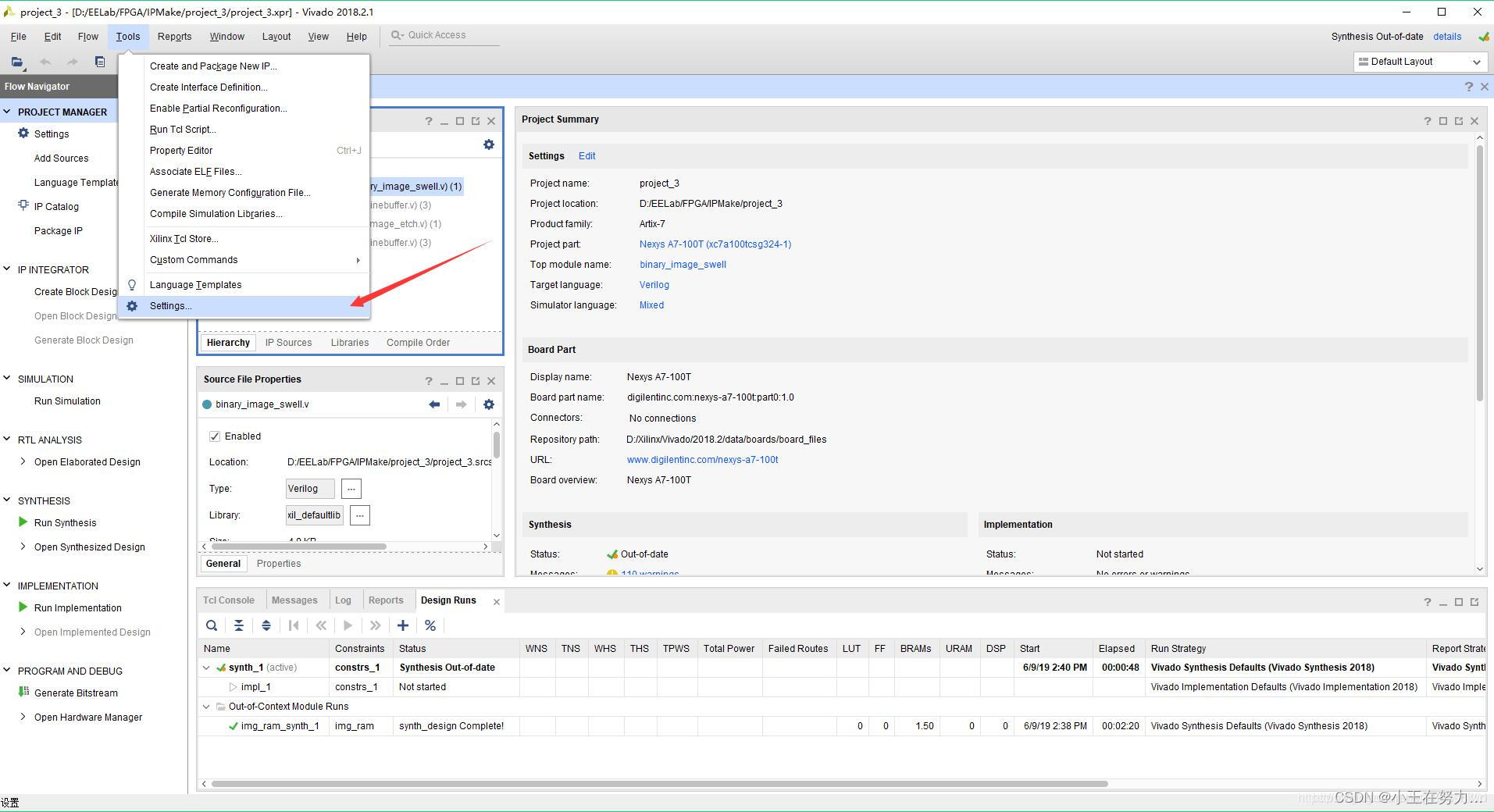

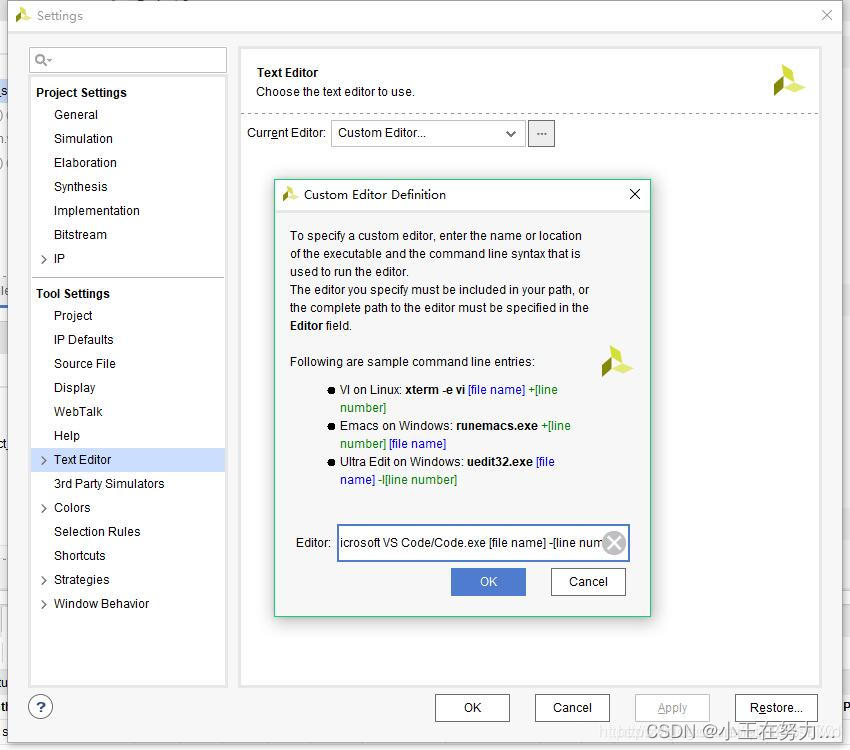

前言一、VSCode安装二、VsCode配置之verilog1.更换Vivado自带文本编辑器第一步 :打开Vivado 再Tool菜单中 打开Settings第二步: 在Settings里更换默认的文本编辑器

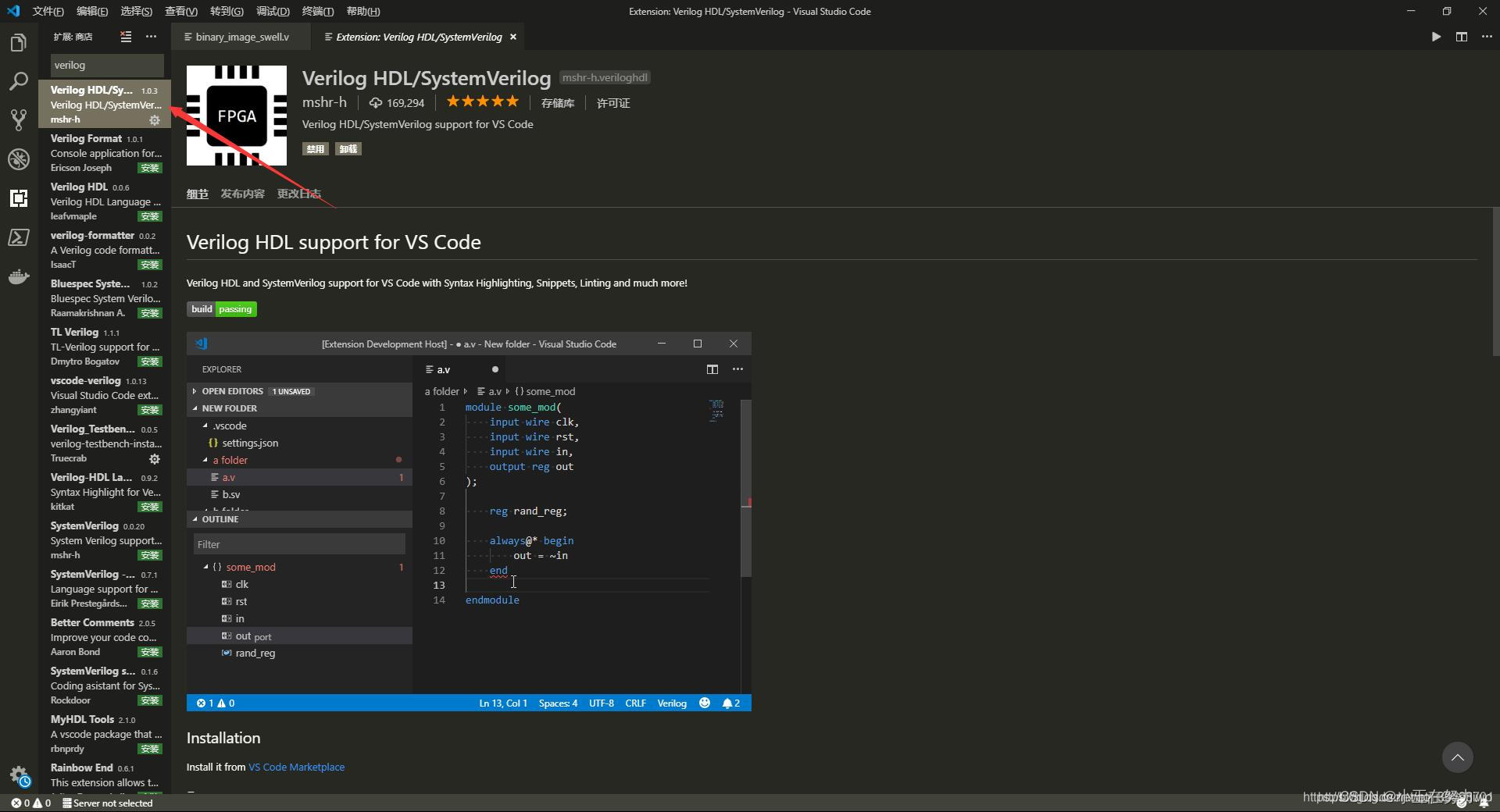

2、安装Verilog插件2.0 Chinese插件2.1 Verilog HDL/SystemVerilog2.1.1 在VsCode扩展商店搜索verilog2.1.2 vivado使用xvlog进行纠错2.1.3 代码格式化

2.2 Verilog_Testbench【注】解决vscode无法产生testbench的问题【注】命令行输入Python跳转应用商店解决办法【注】提示“No module named ‘chardet’”

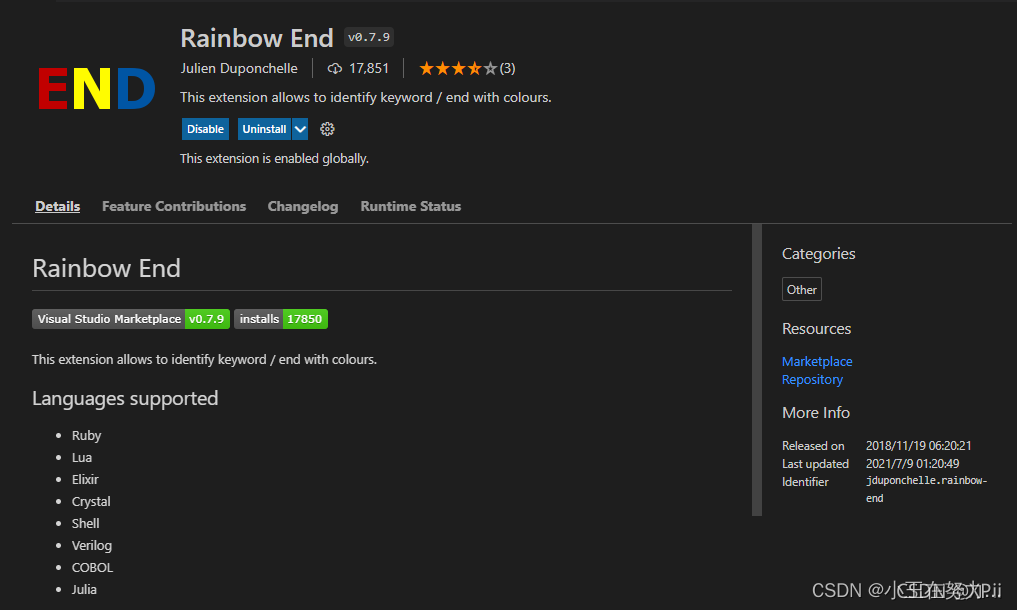

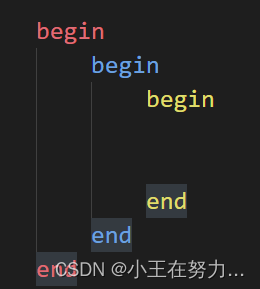

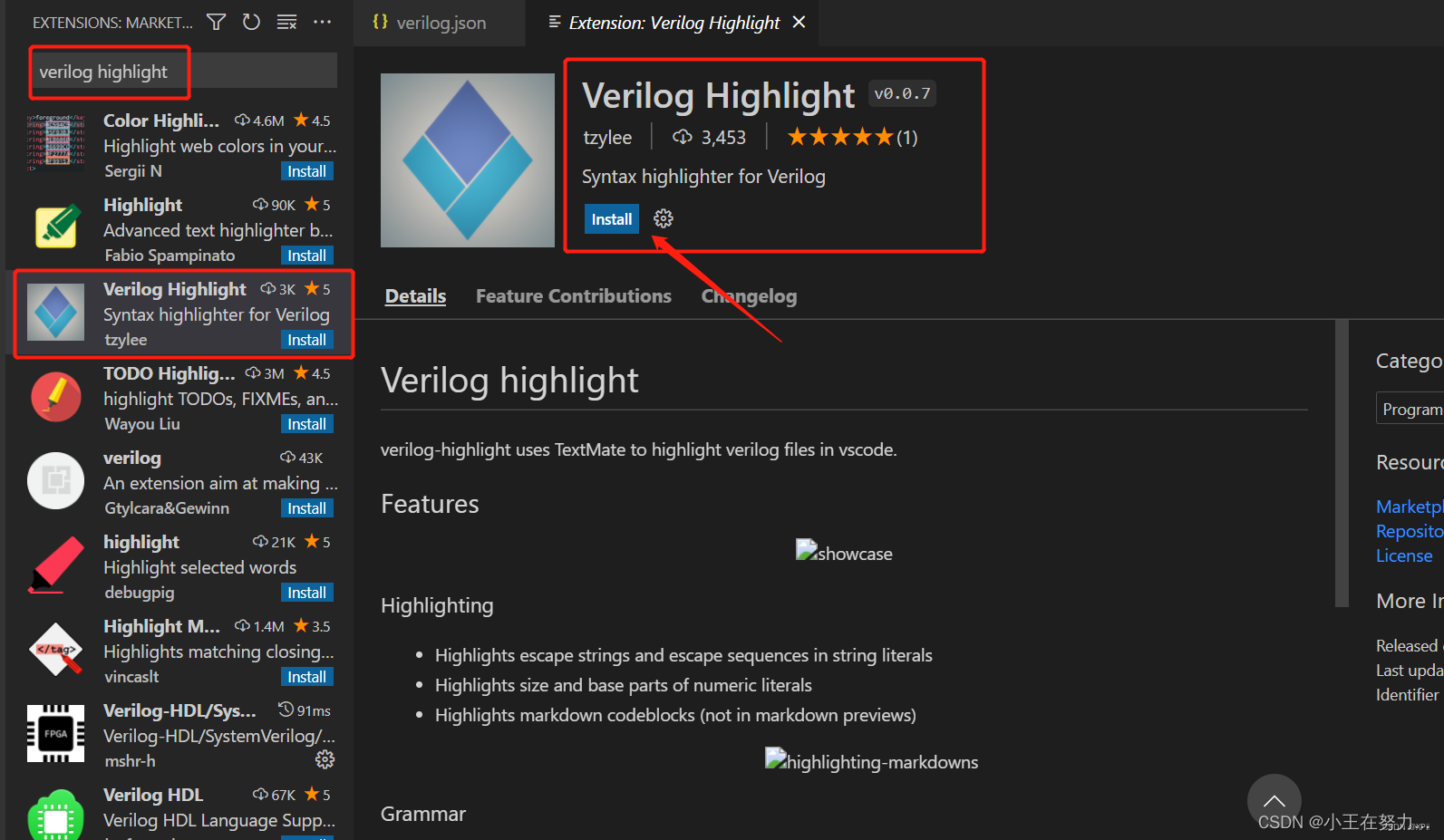

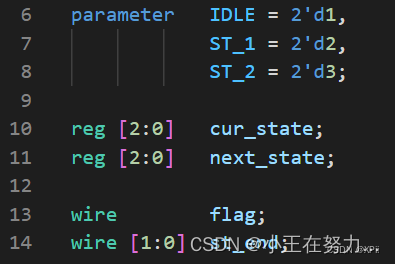

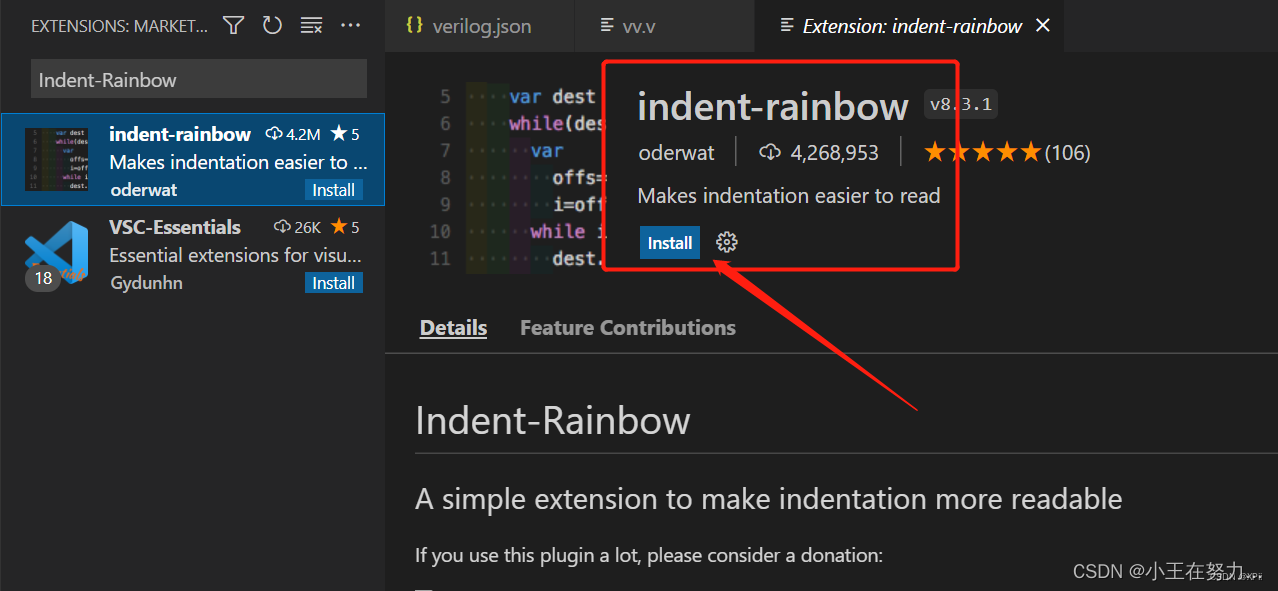

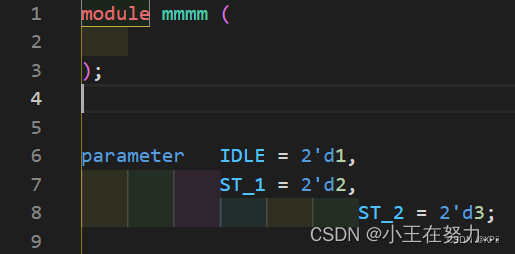

2.3 Rainbow End2.4 Verilog highlight2.5 Indent-Rainbow2.6 vscode中更改Verilog的自动补全功能2.7 vscode中文乱码

前言

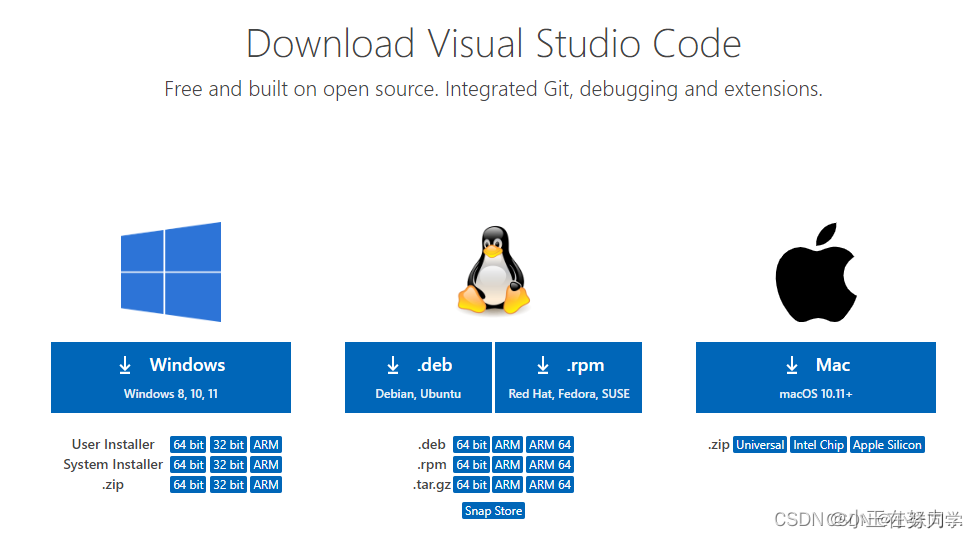

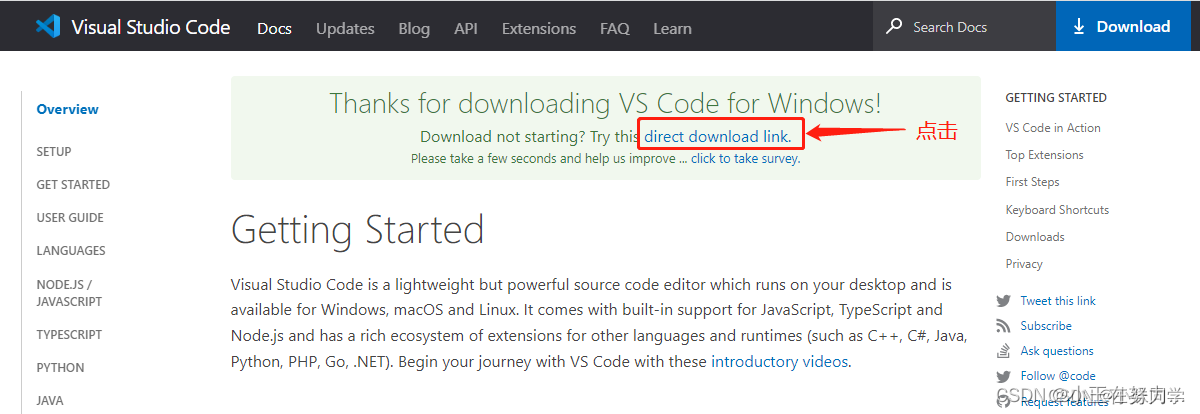

有时候接手别人的代码,或者从网上找的开源代码,每个人风格不一致,对齐缩进也不一样,阅读起来很累。有没有什么方法能快捷地格式化代码呢。下面我们利用VSCode插件来实现这个需求。Vivado是Xilinx公司提供的逻辑开发平台(之一),如果不喜欢Vivado自带的文本编辑器,可以选择第三方的文本编辑器VSCode。 提示:以下是本篇文章正文内容,下面案例可供参考 一、VSCode安装1、在官网下载安装包,官网网址:https://code.visualstudio.com/Download 2、选择好版本之后,点击下图对应的链接就可以开始下载安装包啦~

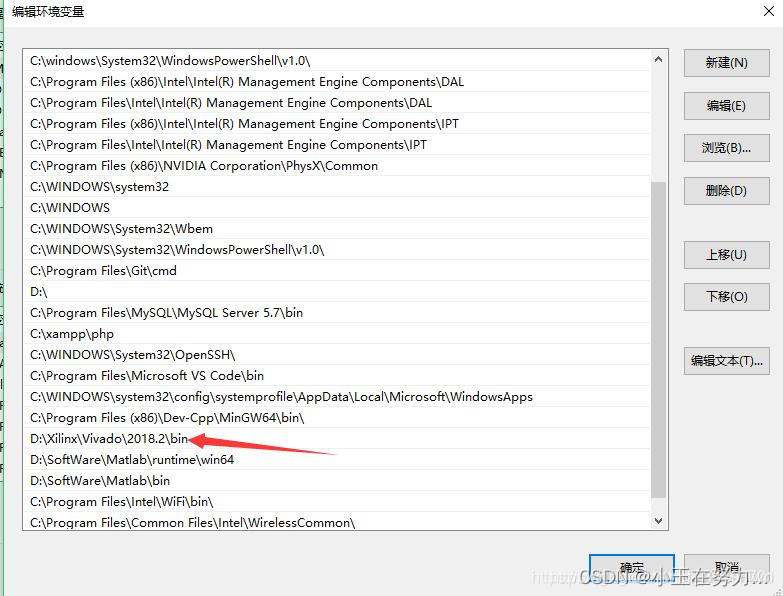

这里需要键入的表达式是: C:/Program Files/Microsoft VS Code/Code.exe -g [file name]:[line number] 前面是VsCode应用程序的绝对路径。 这样双击工程下面的.v文件,Vivado会自动使用VSCode打开文件。 【注】若用vivado打开vscode会卡死,则在进行编辑前,首先打开VScode,打开后再进行编辑不会卡顿,或者删除:[line number] 。 2、安装Verilog插件 2.0 Chinese插件顾名思义将VS Code转化为中文的语言包。 选择Verilog HDL/SystemVerilog,他能帮你实现的功能:语法高亮,自动补齐,列出端口。 vivado安装目录下的xvlog所在的目录放置在系统的环境变量,以便VsCode能够方便的调用他。具体的目录就是Vivado的bin文件夹。 搜索环境变量->点击编辑环境变量->用户变量->Path 就会出现下图,不要在用户变量里添加,要在path里添加。

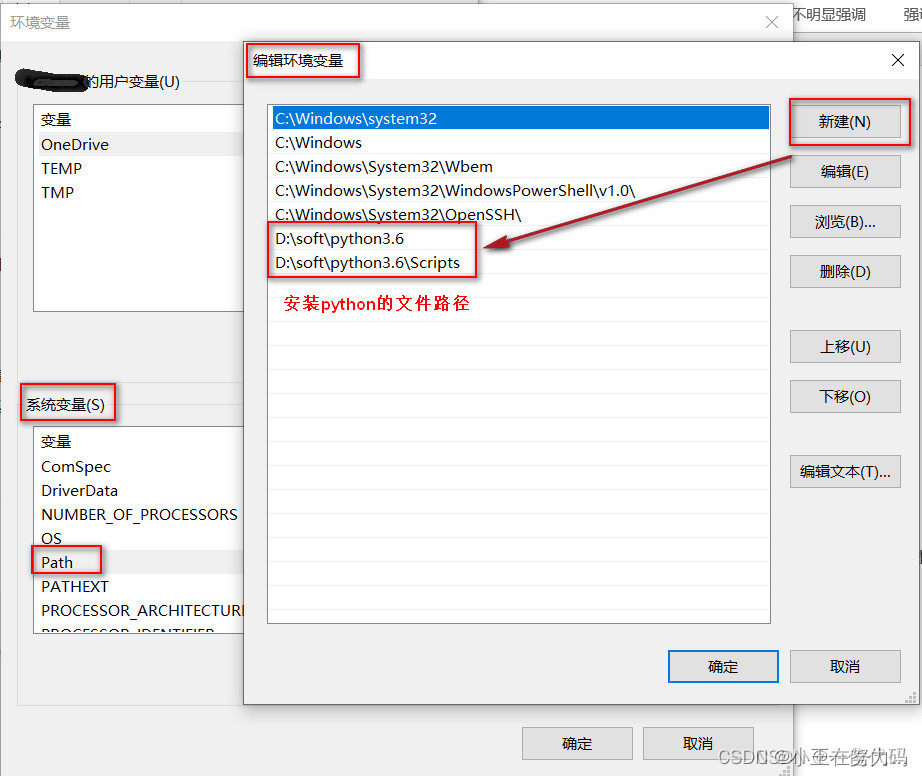

下图我将第8、9行代码故意不对齐,测试代码格式化功能。 有时候在工程中要例化一个模块,这个模块有几十个输入几十个输出,如果没有一个好的脚本帮助你,不仅人为出错的可能比较大,例化的过程想必也是痛苦的。 问题描述:在vscode中安装Verilog_Testbench插件后,在控制台输入testbench命令后VS提示已产生testbench,但是在终端并没有看见。 问题解决:主要问题在于没有安装python环境。首先去python官网下载python安装包https://www.python.org/downloads/release/python-392/ 安装python时记得勾选上添加path路径到环境变量,如果忘记勾选还可以手动添加。

需要在电脑搜索框输入应用执行别名,将应用安装程序取消就可以了,取消之后就可以恢复正常了。

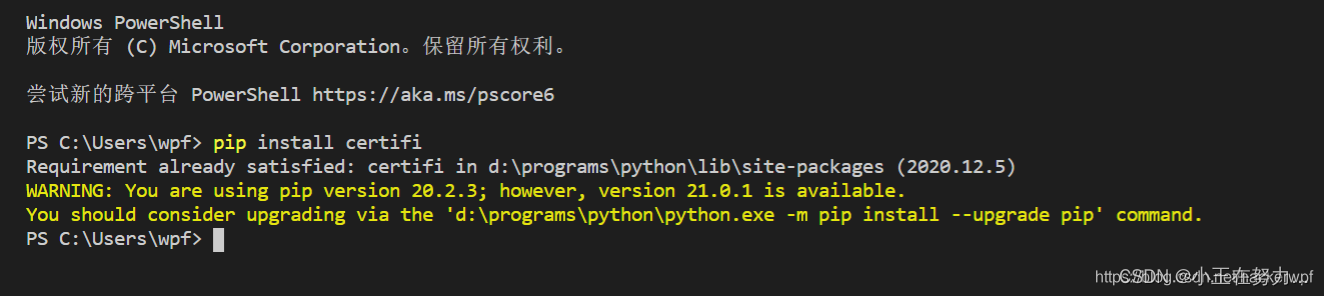

则需要继续安装python扩展包。在终端依次输入pip install certifi,pip install chardet,pip install idna,pip install urllib3安装扩展包。 安装扩展实现不同组begin…end变换颜色 大写字符高亮显示 vscode中每个Tab距离显示不同的颜色

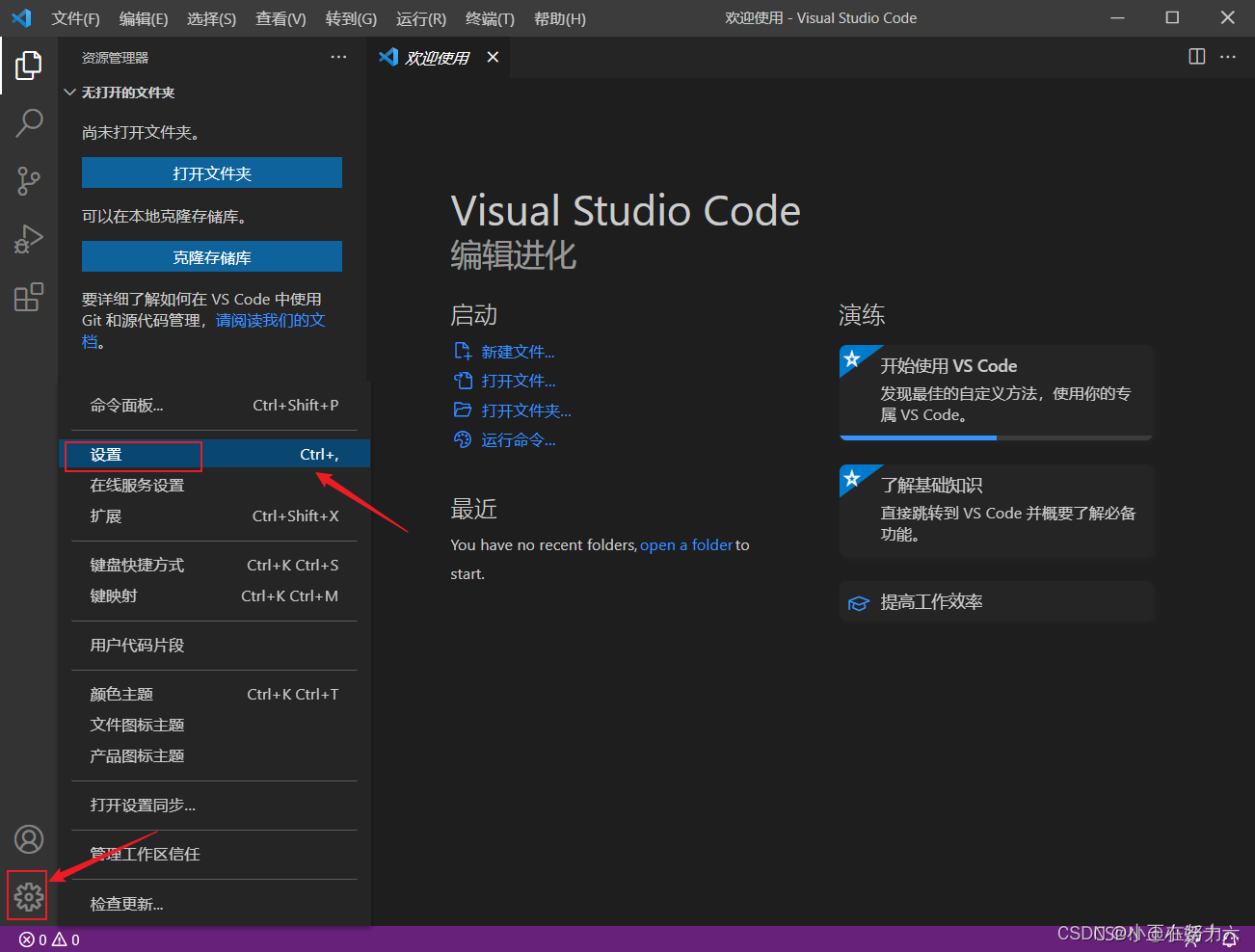

1.选择左下角的“设置”→“设置” |

【本文地址】

今日新闻 |

推荐新闻 |

下载自己系统对应的版本,我的系统是Win10,所以我选择了Windows的User Installer 64bit。

下载自己系统对应的版本,我的系统是Win10,所以我选择了Windows的User Installer 64bit。 但是,由于官网下载速度可能会很慢,所以我在这里提供了百度网盘的下载方式:https://pan.baidu.com/s/1h_YzVgZrDiVc7vzzLFxlEg?pwd=nlqb 提取码:nlqb

但是,由于官网下载速度可能会很慢,所以我在这里提供了百度网盘的下载方式:https://pan.baidu.com/s/1h_YzVgZrDiVc7vzzLFxlEg?pwd=nlqb 提取码:nlqb

下载使用后可观察到界面变为中文。

下载使用后可观察到界面变为中文。

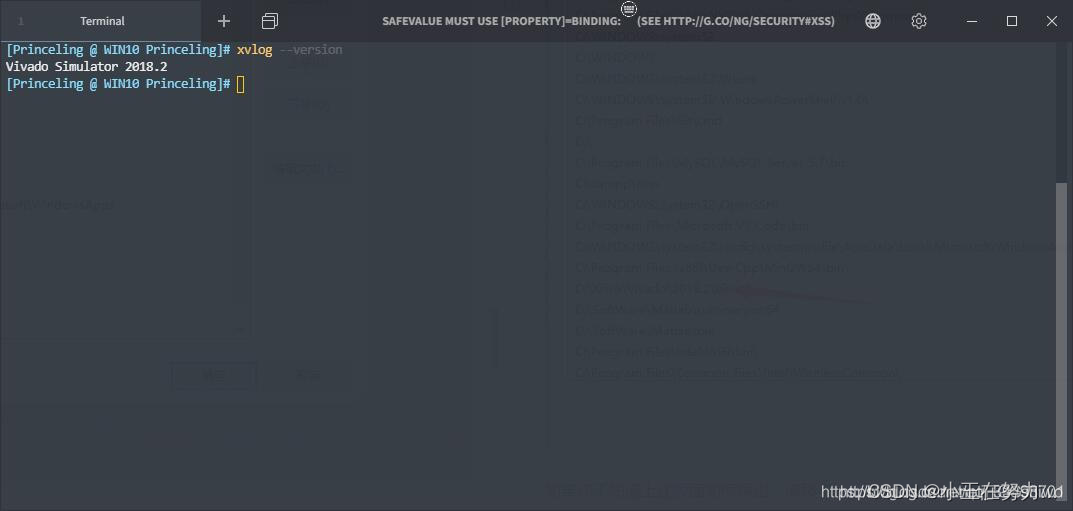

添加完成之后,在命令行输入xvlog -version检测是否生效

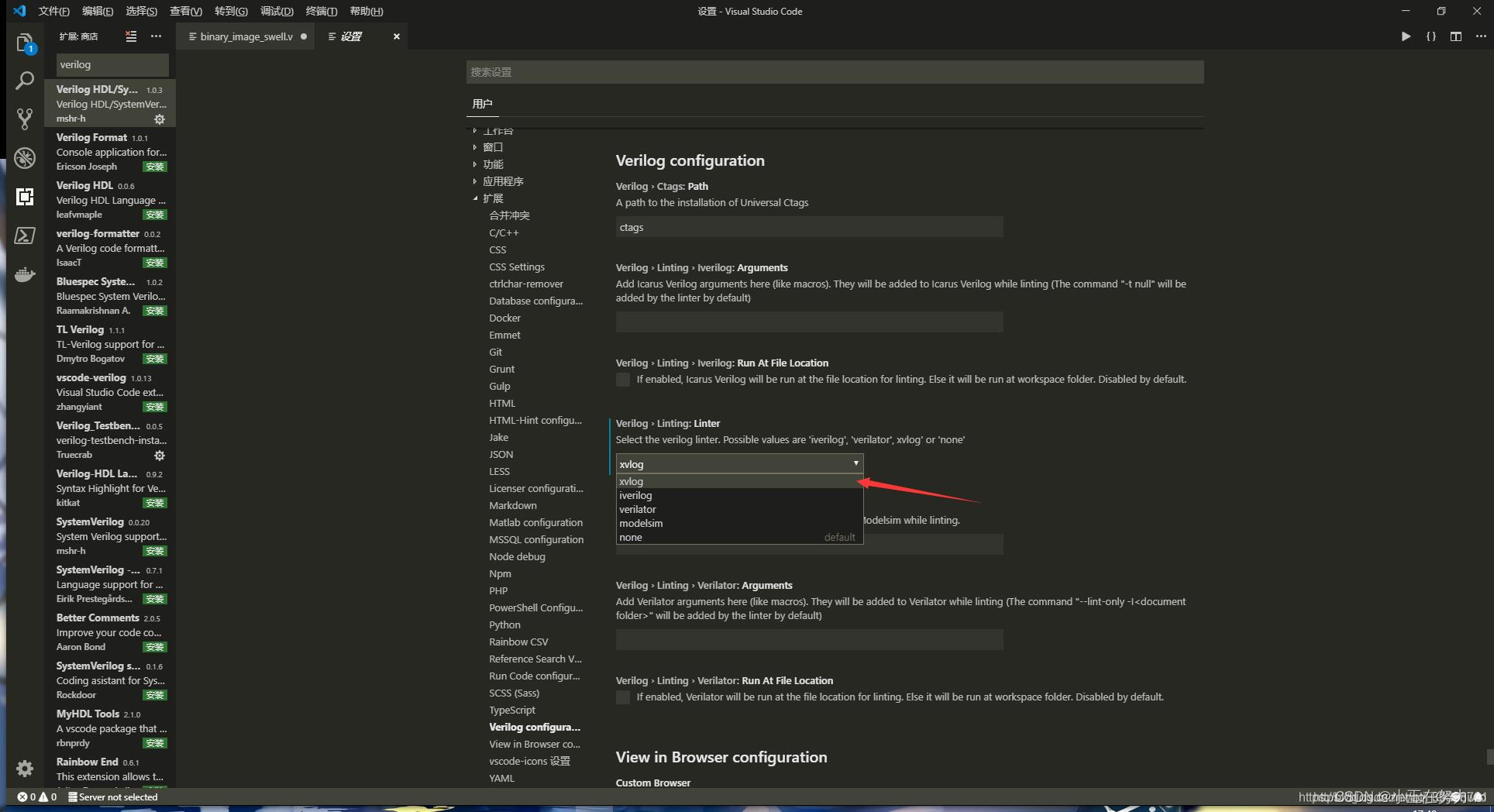

添加完成之后,在命令行输入xvlog -version检测是否生效 接下来我们在设置里,找到刚才安装的verilog扩展,将verilog的Linter更换成xvlog。

接下来我们在设置里,找到刚才安装的verilog扩展,将verilog的Linter更换成xvlog。  需要注意的是,编译器需要您手动保存,才会开启xvlog解析,也就是说观看最新错误之前,需要保存一下。

需要注意的是,编译器需要您手动保存,才会开启xvlog解析,也就是说观看最新错误之前,需要保存一下。 右键选择Format Document 第一次使用会弹出一个配置对话框,选Configure

右键选择Format Document 第一次使用会弹出一个配置对话框,选Configure  因为我装了好几个格式化插件,这里选第一个。你也可以选其他的插件,相关的格式化插件有很多,看自己习惯而定。点击格式化文档即可使文档对齐。

因为我装了好几个格式化插件,这里选第一个。你也可以选其他的插件,相关的格式化插件有很多,看自己习惯而定。点击格式化文档即可使文档对齐。

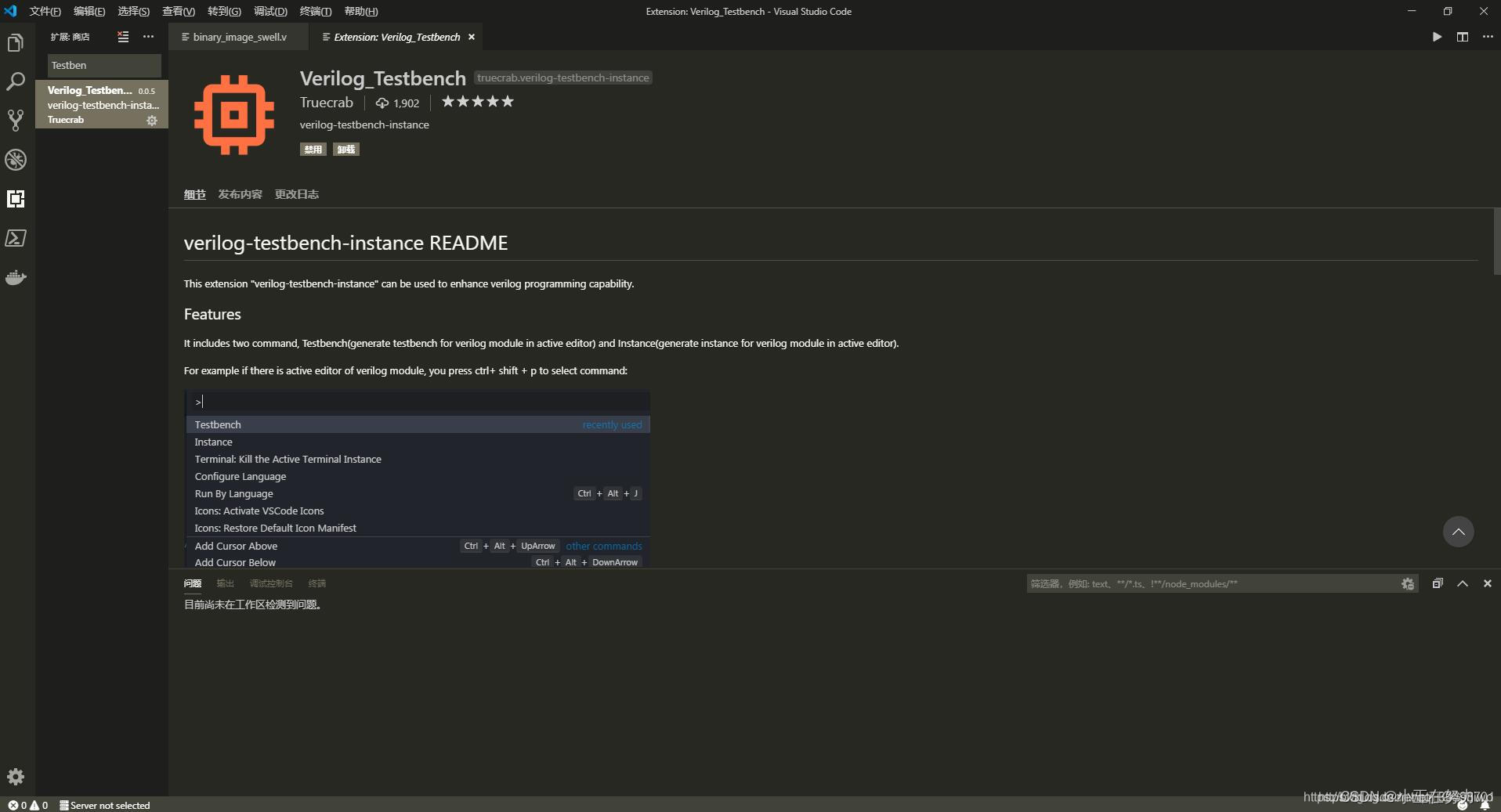

扩展商店搜索Verilog_TestBench,安装过后,任意编写一段verilog程序。按下ctrl+shift+p,选择testbench即可生成testbench对应的tb文本。

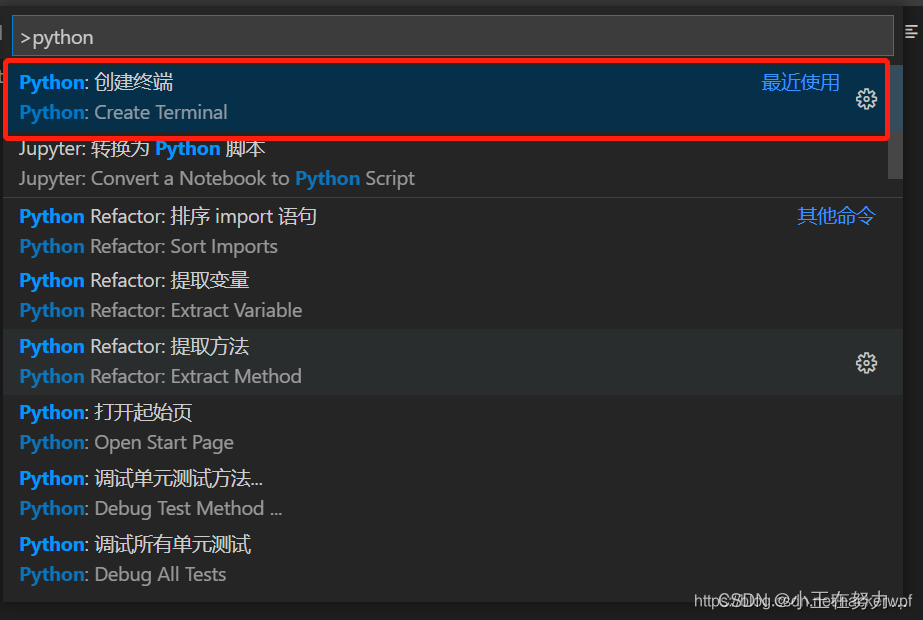

扩展商店搜索Verilog_TestBench,安装过后,任意编写一段verilog程序。按下ctrl+shift+p,选择testbench即可生成testbench对应的tb文本。 两个路径都要添加,添加到用户变量或系统变量都可以。安装完成后到vscode中按ctrl+shift+p打开调试控制台,输入python,选择创建终端。

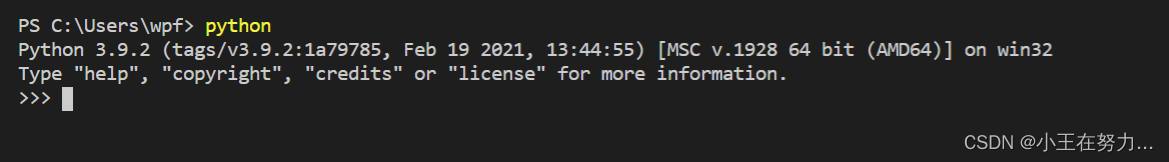

两个路径都要添加,添加到用户变量或系统变量都可以。安装完成后到vscode中按ctrl+shift+p打开调试控制台,输入python,选择创建终端。  在终端中输入python验证是否安装成功。

在终端中输入python验证是否安装成功。 然后在终端中输入python验证是否安装成功。

然后在终端中输入python验证是否安装成功。  输入exit()退出。 在调试控制台输入testbench查看是否能正确产生testbench。

输入exit()退出。 在调试控制台输入testbench查看是否能正确产生testbench。 安装完即可正确产生testbench。

安装完即可正确产生testbench。

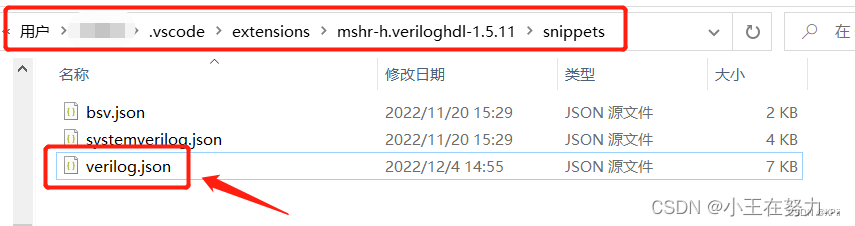

首先需要找到C盘中的verilog.json文件,路径通常为C:\Users\Admin.vscode\extensions\mshr-h.veriloghdl-1.5.11\snippets,不同的电脑用户名位置处不一样。

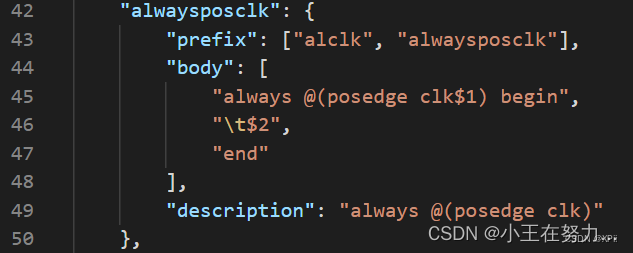

首先需要找到C盘中的verilog.json文件,路径通常为C:\Users\Admin.vscode\extensions\mshr-h.veriloghdl-1.5.11\snippets,不同的电脑用户名位置处不一样。 打开verilog.json文件,如下图所示,当输入prefix后面引号里的文字后,就能选择出body对应的代码片段,在body代码片段里,每行代码需要包含在双引号里,句末加逗号,\t等效tab键所占用的空格数。$1表示代码片段导出之后,鼠标会停留在posedge clk之后,如果输入字符,将替代后面的空格,输入完成后按tab键,跳转到$2处,之后再按下tab键,则继续跳转,不过该代码片段中只到了

2

。其中

2。其中

2。其中+数字在一个代码片段中可以多次出现,且数字相同的地方可以同时进行更改。

打开verilog.json文件,如下图所示,当输入prefix后面引号里的文字后,就能选择出body对应的代码片段,在body代码片段里,每行代码需要包含在双引号里,句末加逗号,\t等效tab键所占用的空格数。$1表示代码片段导出之后,鼠标会停留在posedge clk之后,如果输入字符,将替代后面的空格,输入完成后按tab键,跳转到$2处,之后再按下tab键,则继续跳转,不过该代码片段中只到了

2

。其中

2。其中

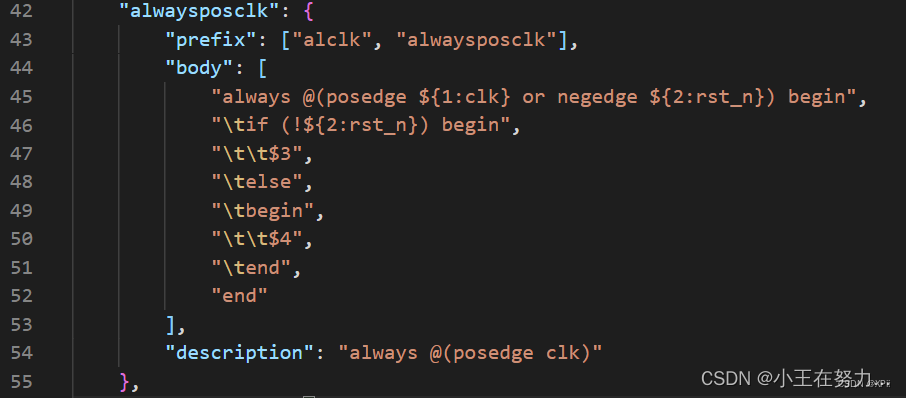

2。其中+数字在一个代码片段中可以多次出现,且数字相同的地方可以同时进行更改。  以下是修改后该片段的代码:

以下是修改后该片段的代码:  修改后的自动补全功能如下所示:

修改后的自动补全功能如下所示:

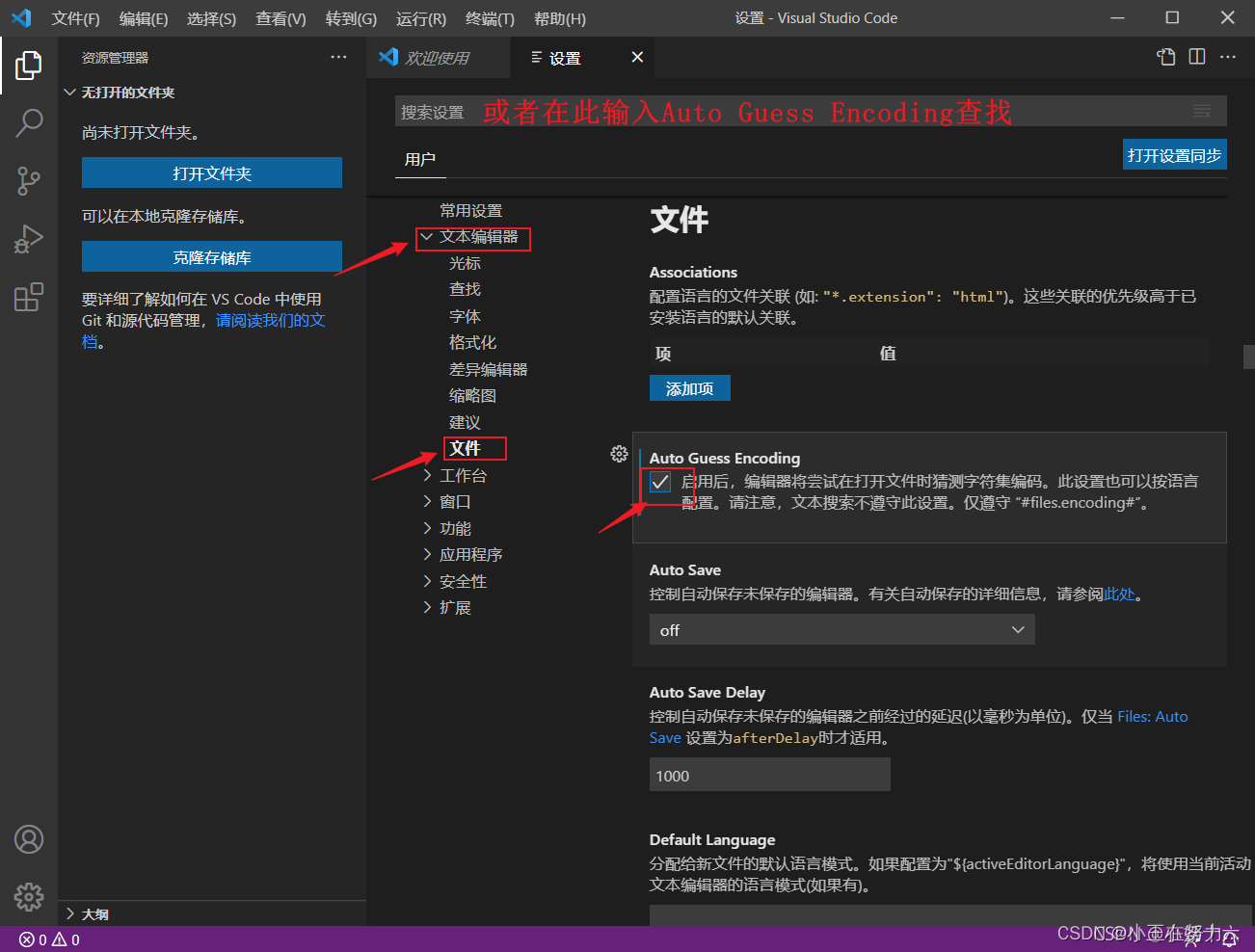

2.在“文本编辑器”下拉菜单找到“文件”,勾选“Auto Guess Encoding”(或者直接在搜索栏输入:Auto Guess Encoding,也能快速找到)→之后重启VSCode设置即可生效

2.在“文本编辑器”下拉菜单找到“文件”,勾选“Auto Guess Encoding”(或者直接在搜索栏输入:Auto Guess Encoding,也能快速找到)→之后重启VSCode设置即可生效