IP核的使用之ROM(Vivado) |

您所在的位置:网站首页 › vivado顶层文件无效 › IP核的使用之ROM(Vivado) |

IP核的使用之ROM(Vivado)

|

存储类IP核——ROM

文章目录

存储类IP核——ROM一.引言二.ROM IP核及相关内容扫盲1.ROM简介2.ROM的初始化文件介绍3.分布式ROM和块ROM简介4.单端口ROM和双端口ROM简介

三.分布式ROM IP核的创建四.分布式ROM IP核的测试仿真五.块ROM IP核的创建六.块ROM IP核的测试仿真

一.引言

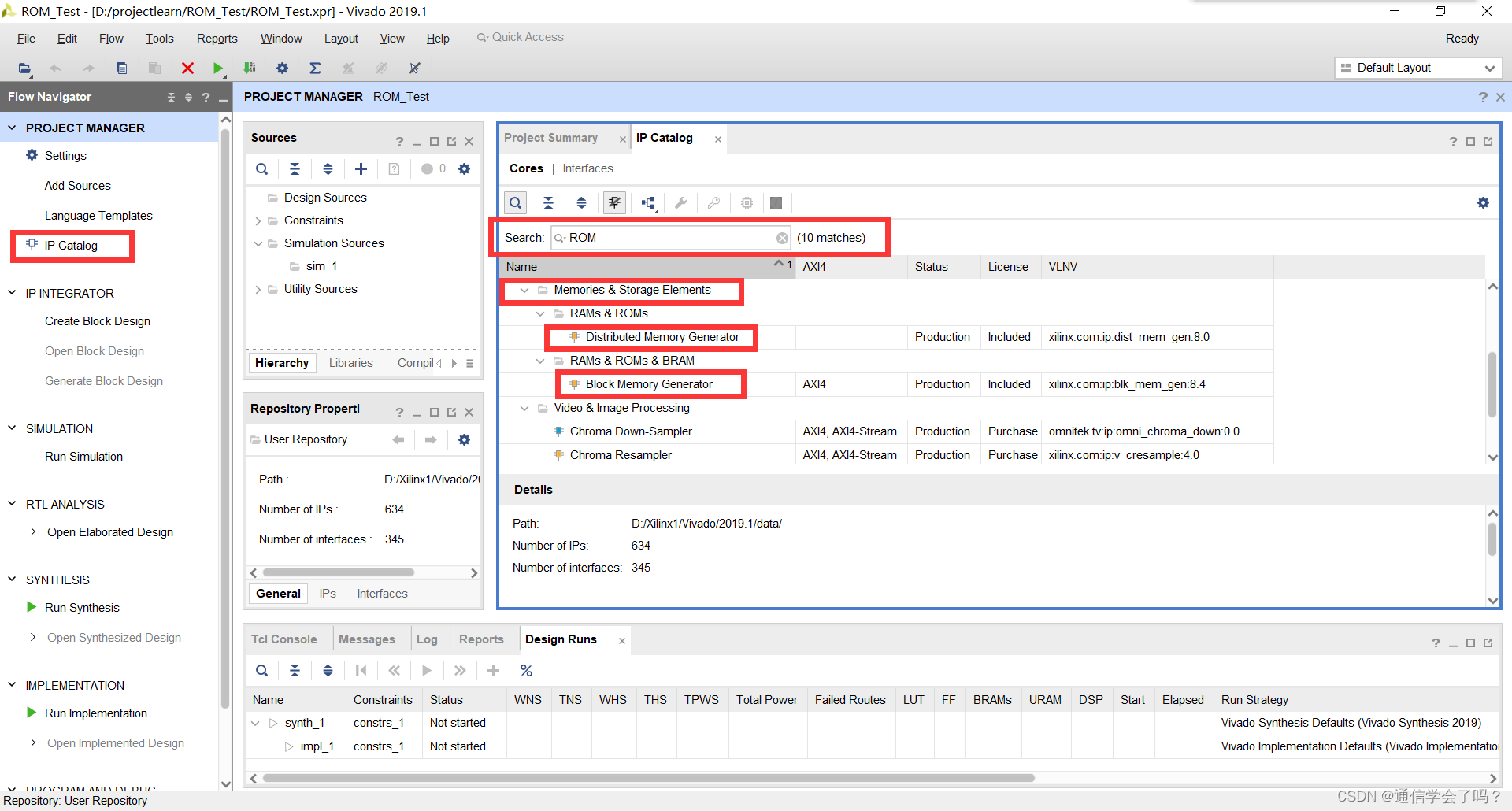

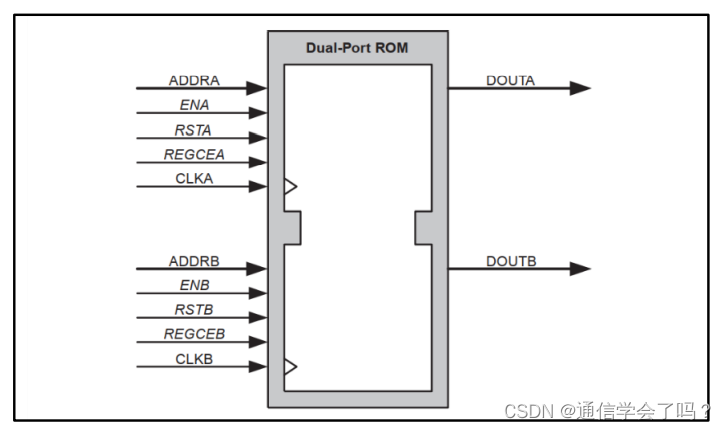

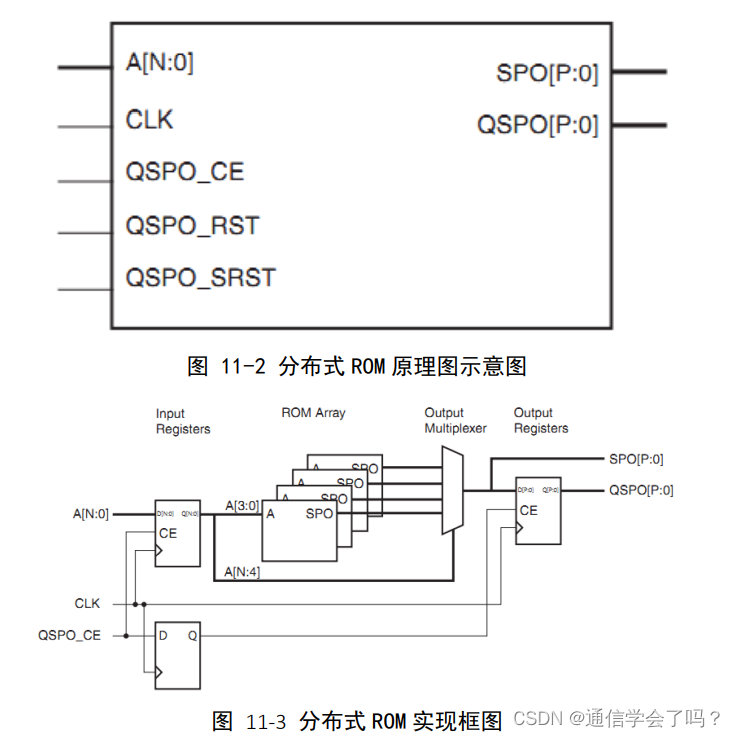

在理论给大家介绍什么是ROM之前,先设想这么一个实际场景:现在有某芯片,它拥有500个寄存器,且需要在上电的时候由FPGA向这些寄存器中写入初始值,假设初始值已经通过相应的文档给出了具体值,这些值都是已知的。 这类实际需求有哪些特点呢? 1.数据量比较多 2.数据值都是已知的 3.数据内容不需要换 我们可以用什么办法来解决这个问题呢? 我们需要用一个存储器将这些数据先起来,使用的时候读取存储器就可以了。这个存储器只需要支持读功能就可以了。这就是ROM(read only memory) 实际应用有哪些呢? 1.DDS信号发生器(固定波形数据的形式) 2.对应CMOS摄像头初始化的应用 二.ROM IP核及相关内容扫盲 1.ROM简介ROM 是只读存储器(Read-Only Memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。其特性是一旦储存资料就无法再将之改变或删除,且资料不会因为电源关闭而消失。而事实上在 FPGA 中通过 IP 核生成的 ROM 或 RAM 调用的都是 FPGA 内部的RAM 资源,掉电内容都会丢失(这也很容易解释,FPGA 芯片内部本来就没有掉电非易失存储器单元)。用 IP 核生成的 ROM 模块只是提前添加了数据文件(.coe 格式),在 FPGA 运行时通过数据文件给 ROM 模块初始化,才使得 ROM 模块像个真正”的掉电非易失存储器;也正是这个原因,ROM 模块的内容必须提前在数据文件中写死,无法在电路中修改。 2.ROM的初始化文件介绍ROM 作为只读存储器,在进行 IP 核设置时需要指定初始化文件,即写入存储器中的数据,数据要以规定的格式才能正确写入 ROM,这种格式就是 coe 文件.coe 是 Vivado 规定的一种文件格式,如下图所示 我们先新建 Vivado 工程,单击 IP Catalog,在右边窗口 Search 位置输入 rom,在 Memories &Storage Elements 下可以看到有两个与 ROM 相关的 IP,一个是 Distributed Memory Generator(分布式ROM),另一个是 Block Memory Generator(块ROM)。 对于单端口 ROM 提供一个读地址端口和一个读数据端口,只能进行读操作;双端口 ROM 与单端口 ROM 类似,区别是其提供两个读地址端口和两个读数据端口,基本上可以看做两个单口 RAM 拼接而成。下面是 ROM 不同配置模式存储器的接口信号图 Distributed Memory Generator(分布式ROM) 是使用 LUT 资源创建的内存结构。主要可以用于创建以下内存类型: (1)Distributed ROM (2)Distributed Single-Port RAM (3)Distributed Dual-Port RAM (4)Distributed Simple Dual-Port RAM 使用Distributed Memory Generator 去生成的 ROM IP 是基于 LUT 的分布式 ROM 资源来创建深度为 16,位宽为 1bit 的 ROM,并通过生成一个基于结构的总线多路复用器来创建一个更深、更宽ROM。在 ROM 生成时,通过 vivado 加载一个内存初始化文件(COE 文件)来初始化该 ROM,IP 生成完后,ROM 存储的数据就固定了。分布式 ROM 原理图示意图和其实现框图如下。 这里除了实现例化需要仿真的文件以及时钟创建,还实现了地址数从 0 自加到 2559d,但是由于本 ROM 的最大数据个数是 255d,因此在 address第一次加满 255 后会重新从 0 开始自加,这样就有十个地址数循环。ROM_tb.v 文件代码如下: `timescale 1ns/1ns `define CLK_PERIOD 20 module ROM_tb; reg clk; reg [7:0]addr; wire [7:0]dout; wire [7:0]dout_reg; initial clk = 1; always #(`CLK_PERIOD/2) clk = ~clk; dist_mem_rom_ip rom ( .a(addr), // input wire [7 : 0] a .clk(clk), // input wire clk .spo(dout), // output wire [7 : 0] spo .qspo(dout_reg) // output wire [7 : 0] qspo ); integer i = 0; initial begin addr = 0; #21; for(i=0;i |

【本文地址】

今日新闻 |

推荐新闻 |

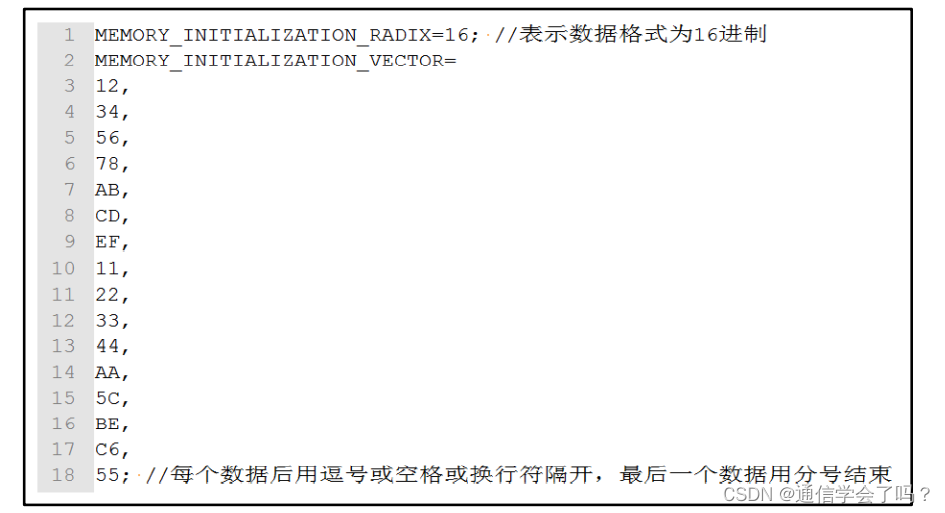

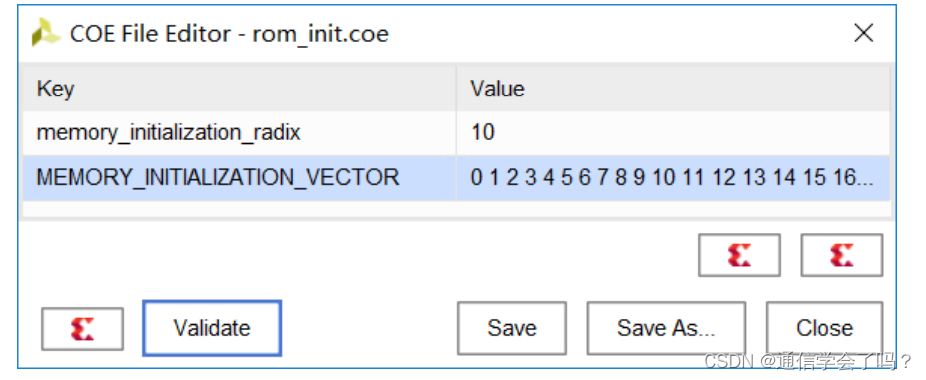

如上图所示,该文件的格式较为简单,**第一行是定义数据的格式,其中 16 表示数据格式为 16 进制,**也可将数据格式定义为二进制和八进制,只需将 16 改为 2 或 8 即可。其中第 3 到第 18 行是 16*8bit 大小 ROM 的初始化数据。 上面用到了两个关键字,memory_initialization_radix 和 memory_initialization_vector。其中,memory_initialization_radix 是 ROM 初始化数值进制设置,对应后面 Value 值可设置 2,10,16,分别表示 2 进制,10 进制,16 进制。memory_initialization_vector 是 ROM 初始化数据向量,对应后面 Value 值就是填写 ROM 初始化的数据,数据与数据之间通过空格或逗号隔开,数据个数不允许超过设置 ROM 的深度(可以少于设置的深度),数据不允许为负数。 下图为在第三部分自己编写coe文件时的界面:

如上图所示,该文件的格式较为简单,**第一行是定义数据的格式,其中 16 表示数据格式为 16 进制,**也可将数据格式定义为二进制和八进制,只需将 16 改为 2 或 8 即可。其中第 3 到第 18 行是 16*8bit 大小 ROM 的初始化数据。 上面用到了两个关键字,memory_initialization_radix 和 memory_initialization_vector。其中,memory_initialization_radix 是 ROM 初始化数值进制设置,对应后面 Value 值可设置 2,10,16,分别表示 2 进制,10 进制,16 进制。memory_initialization_vector 是 ROM 初始化数据向量,对应后面 Value 值就是填写 ROM 初始化的数据,数据与数据之间通过空格或逗号隔开,数据个数不允许超过设置 ROM 的深度(可以少于设置的深度),数据不允许为负数。 下图为在第三部分自己编写coe文件时的界面:  注:Key 和 Value 里面填写内容不区分大小写。

注:Key 和 Value 里面填写内容不区分大小写。 先简单说说两个的差别,两者最主要的差别是生成的 Core所占用的 FPGA 资源不一样,从Distributed Memory Generator 生成的 ROM/RAM Core 占用的资源是 LUT(查找表,查找表本质就是一个小的 RAM);从 Block Memory Generator 生成的 ROM/RAM Core 占用的资源是 Block Memory(嵌入式的硬件 RAM),有关两者详细的区别和使用下面会进行讲解。

先简单说说两个的差别,两者最主要的差别是生成的 Core所占用的 FPGA 资源不一样,从Distributed Memory Generator 生成的 ROM/RAM Core 占用的资源是 LUT(查找表,查找表本质就是一个小的 RAM);从 Block Memory Generator 生成的 ROM/RAM Core 占用的资源是 Block Memory(嵌入式的硬件 RAM),有关两者详细的区别和使用下面会进行讲解。

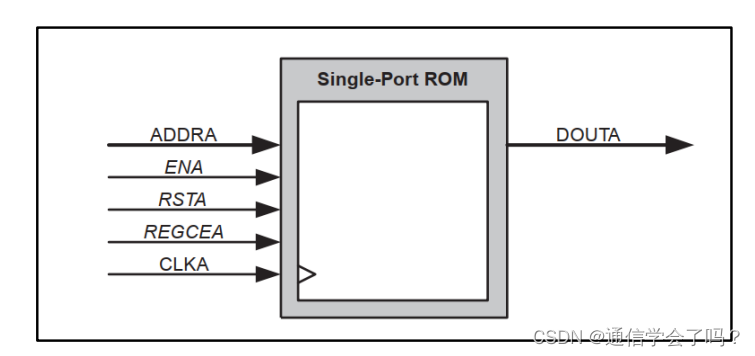

上图中的接口信号我们并不是全部需要用到,因为我们配置时,有些信号是可以不创建的。所以很多接口信号我们可以不用管,只需管我们需要用的信号即可,而**什么信号是我们需要用到的呢?**这在我们调用完 IP 核后,是可以生成其例化模块的,到时候就可以看到我们需要控制的信号了。

上图中的接口信号我们并不是全部需要用到,因为我们配置时,有些信号是可以不创建的。所以很多接口信号我们可以不用管,只需管我们需要用的信号即可,而**什么信号是我们需要用到的呢?**这在我们调用完 IP 核后,是可以生成其例化模块的,到时候就可以看到我们需要控制的信号了。 在 IP Catalog 窗口选择 Distributed Memory Generator 并双击,进入IP配置界面,如下:

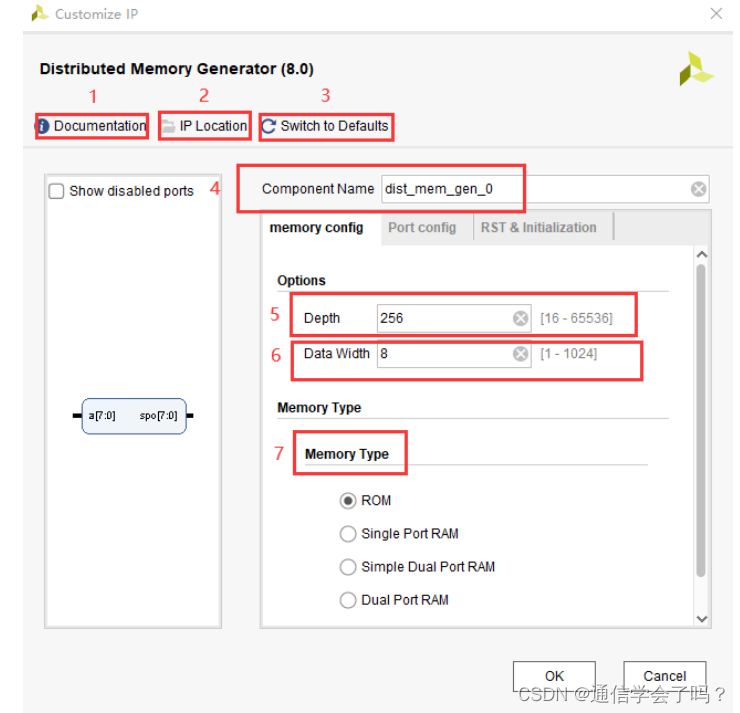

在 IP Catalog 窗口选择 Distributed Memory Generator 并双击,进入IP配置界面,如下:  (1)Documentation:IP 相关文档入口 (2)IP Location:生成 IP 的存放路径,可以通过点击 … 设置更换存放路径,默认是存放在工程路径下的 bin_counter.srcs\ sources_1\ ip,我这里就保持默认。 (3)Switch to Default:点击后所有的设置恢复到默认值 (4)Component Name:设置生成 IP Core 的名称,我这里将名字设置为 dist_mem_rom_ip; (5)Depth:设置 ROM 深度,我这里设置 256; (6)Data Width:设置数据位宽,我这里设置 8; (7)Memory Type:选择存储类型,这里选择 ROM

(1)Documentation:IP 相关文档入口 (2)IP Location:生成 IP 的存放路径,可以通过点击 … 设置更换存放路径,默认是存放在工程路径下的 bin_counter.srcs\ sources_1\ ip,我这里就保持默认。 (3)Switch to Default:点击后所有的设置恢复到默认值 (4)Component Name:设置生成 IP Core 的名称,我这里将名字设置为 dist_mem_rom_ip; (5)Depth:设置 ROM 深度,我这里设置 256; (6)Data Width:设置数据位宽,我这里设置 8; (7)Memory Type:选择存储类型,这里选择 ROM  (8)Input Options:设置是否对输入的地址增加一级寄存器,这里设置选择 Registered,对输入的地址增加一级寄存器(也可以选择 Non Registered,不增加寄存器)。 (9)Output Option:设置是否对输出的地址增加一级寄存器,这里设置选择 Both,对输出数据信号 spo 和增加一级寄存器后的输出数据信号 qspo 都从端口引出。下面还有个 SinglePort Output CE 可选配,当勾选后,ROM Core 就会多出一个 qspo_ce 的端口,这个信号是用来控制使能输出寄存器的时钟。这里没有用到这个功能,不勾选该项。

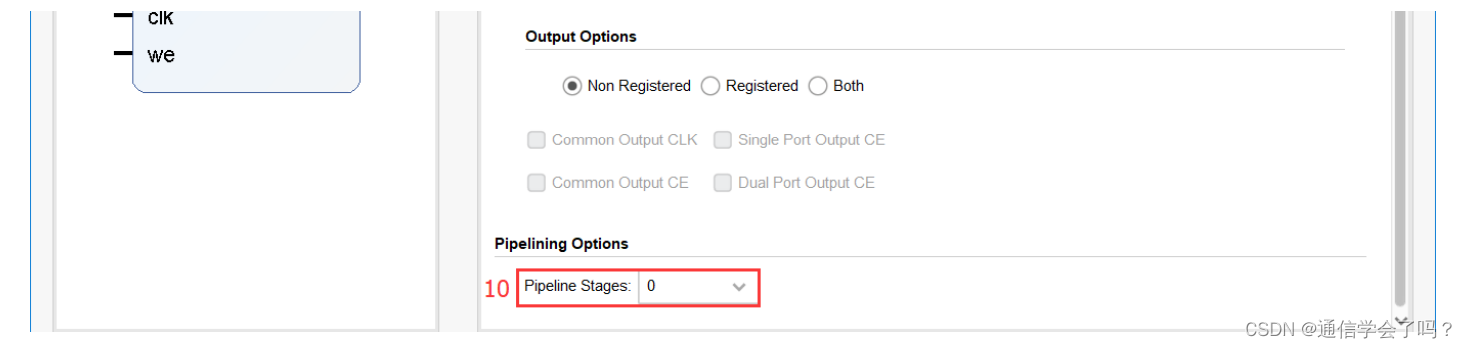

(8)Input Options:设置是否对输入的地址增加一级寄存器,这里设置选择 Registered,对输入的地址增加一级寄存器(也可以选择 Non Registered,不增加寄存器)。 (9)Output Option:设置是否对输出的地址增加一级寄存器,这里设置选择 Both,对输出数据信号 spo 和增加一级寄存器后的输出数据信号 qspo 都从端口引出。下面还有个 SinglePort Output CE 可选配,当勾选后,ROM Core 就会多出一个 qspo_ce 的端口,这个信号是用来控制使能输出寄存器的时钟。这里没有用到这个功能,不勾选该项。  (10)Pipeline Stages:流水线级数,在生成 ROM 模式下,不可配。

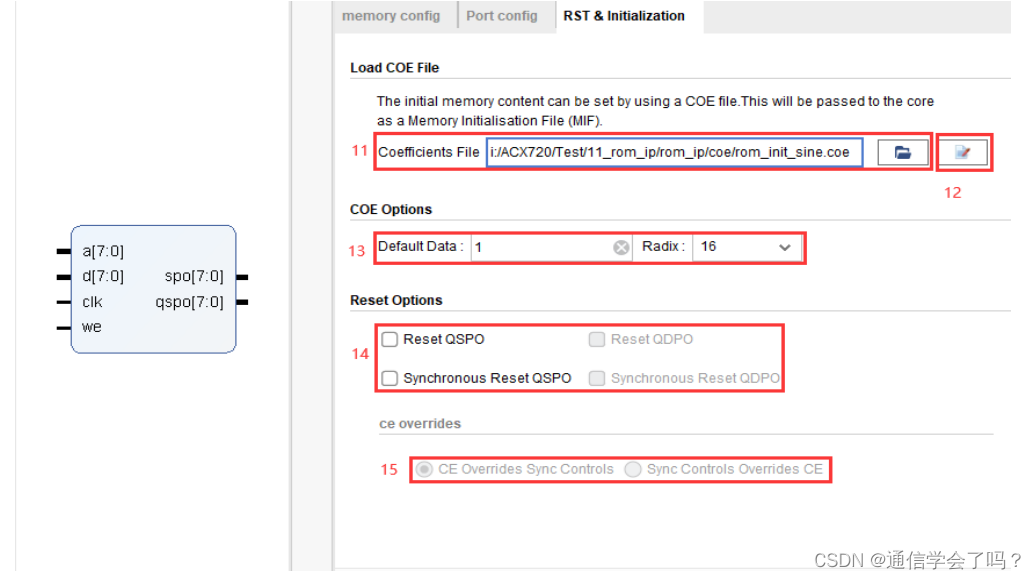

(10)Pipeline Stages:流水线级数,在生成 ROM 模式下,不可配。  (11)添加 COE 文件位置,可以通过选择路径添加已有的 COE 文件,软件会通过 COE 文件生成 ROM 初始化文件 MIF 文件。关于如何创建 COE 文件看下一步骤。 (12) 编辑按钮,当(11)中未加载 COE 文件时,点击这里的按钮,会弹出提示框,点击YES 可进入到创建 COE 文件的流程,这里点击 YES。我这里是用的小梅哥生产的软件Mif精灵,可在小梅哥论坛下载。

(11)添加 COE 文件位置,可以通过选择路径添加已有的 COE 文件,软件会通过 COE 文件生成 ROM 初始化文件 MIF 文件。关于如何创建 COE 文件看下一步骤。 (12) 编辑按钮,当(11)中未加载 COE 文件时,点击这里的按钮,会弹出提示框,点击YES 可进入到创建 COE 文件的流程,这里点击 YES。我这里是用的小梅哥生产的软件Mif精灵,可在小梅哥论坛下载。  之后保存到工程的根目录下,按照(11)操作就可以了。 (13)COE Options:设置 ROM 中初始化数据没有覆盖的区域的数值,比如 ROM 深度 256,添加的 COE 文件中仅初始化了 200 个数据,这里就是统一设置剩下的 56 个数据的数值。 (14)Reset Options:添加输出寄存器复位信号,可添加同步复位或异步复位,这里就不勾选添加复位信号。 (15)ce overrides 设置 CE Overrides Sync Controls:在选择了输出寄存器同步复位和时钟使能才能启用,启用后,同步控制由时钟使能限定。 Sync Controls Overrides CE:在选择了输出寄存器同步复位和时钟使能才能启用,启用后,同步控制信号会工作,不受时钟使能限定。 前面未勾选时钟使能信号 CE,这里就不可设置,保持默认即可。 ROM IP 的各种参数设置完后点击 OK。

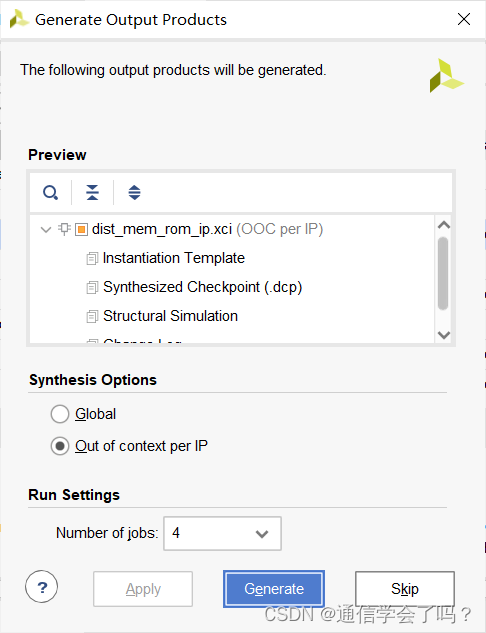

之后保存到工程的根目录下,按照(11)操作就可以了。 (13)COE Options:设置 ROM 中初始化数据没有覆盖的区域的数值,比如 ROM 深度 256,添加的 COE 文件中仅初始化了 200 个数据,这里就是统一设置剩下的 56 个数据的数值。 (14)Reset Options:添加输出寄存器复位信号,可添加同步复位或异步复位,这里就不勾选添加复位信号。 (15)ce overrides 设置 CE Overrides Sync Controls:在选择了输出寄存器同步复位和时钟使能才能启用,启用后,同步控制由时钟使能限定。 Sync Controls Overrides CE:在选择了输出寄存器同步复位和时钟使能才能启用,启用后,同步控制信号会工作,不受时钟使能限定。 前面未勾选时钟使能信号 CE,这里就不可设置,保持默认即可。 ROM IP 的各种参数设置完后点击 OK。  出现如上图弹窗,点击 Generate,之后等 IP 生成完成后,出现如下图弹窗,点击 OK。 可 以 在 PROJECT MANAGER 窗 口 下 IP Source 窗 口 IP Synthesis 下 看 到 dist_mem_rom_ip.mif 文件,如下图

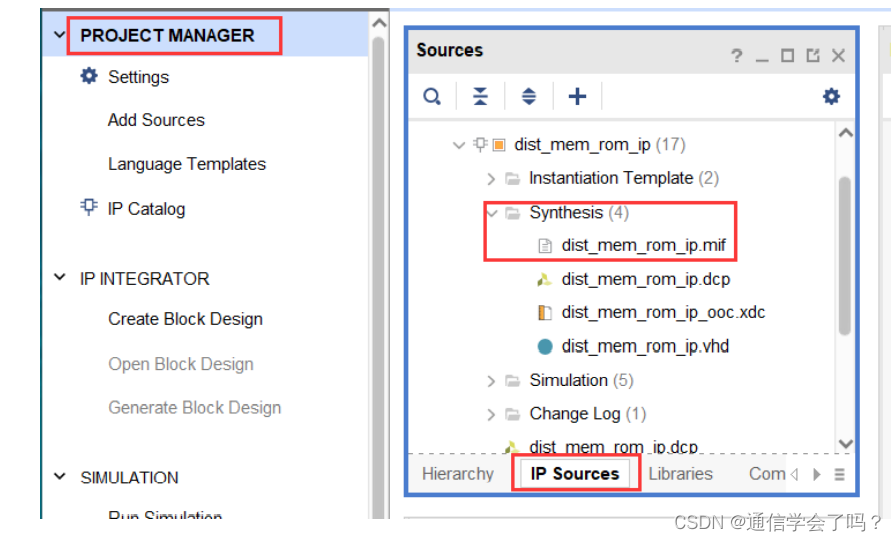

出现如上图弹窗,点击 Generate,之后等 IP 生成完成后,出现如下图弹窗,点击 OK。 可 以 在 PROJECT MANAGER 窗 口 下 IP Source 窗 口 IP Synthesis 下 看 到 dist_mem_rom_ip.mif 文件,如下图  这个文件就是 IP 生成过程中通过我们添加的 coe 文件自动生成的,这点和 quartus 有所不(quartus 是用户直接添加指定 mif 文件)。有一点比 quartus 好的就是在 ROM Core 建立时 vivado 软件会根据用户添加 coe 文件以及设置 ROM 参数(深度,位宽)对 coe 文件进行校验,如果不符合要求会提示相关错误,可以有效避免初始化文件不匹配的问题。

这个文件就是 IP 生成过程中通过我们添加的 coe 文件自动生成的,这点和 quartus 有所不(quartus 是用户直接添加指定 mif 文件)。有一点比 quartus 好的就是在 ROM Core 建立时 vivado 软件会根据用户添加 coe 文件以及设置 ROM 参数(深度,位宽)对 coe 文件进行校验,如果不符合要求会提示相关错误,可以有效避免初始化文件不匹配的问题。