课时3:Vitis HLS设计流程(实例演示) |

您所在的位置:网站首页 › vivado打开仿真波形 › 课时3:Vitis HLS设计流程(实例演示) |

课时3:Vitis HLS设计流程(实例演示)

|

课时3:Vitis HLS设计流程(实例演示)

1. 前言2. Vitis HLS设计注意事项3. Vitis HLS设计示例3.1 Vitis HLS工程建立3.2 仿真和综合3.3 创建另一个Solution

4. 总结

1. 前言

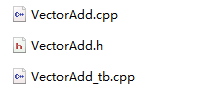

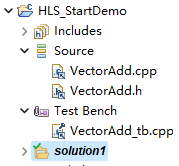

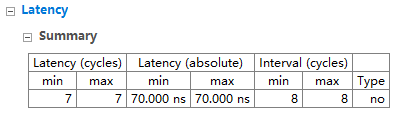

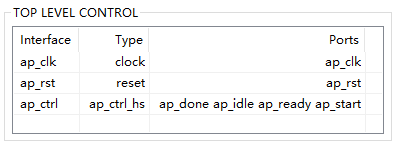

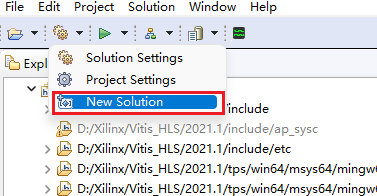

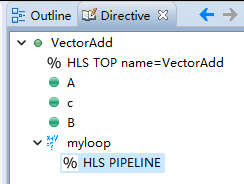

课时2我们介绍了Vitis HLS的设计流程,如下图所示: 算法或软件的设计和仿真都基于C/C++,通过HLS平台导出打包好的IP RTL代码,最后将该打包的IP加入到主工程使用。 本课时,我们通过一个具体的实例,演示HLS设计流程。 2. Vitis HLS设计注意事项在Vitis HLS中,只有一个函数可以设为顶层综合函数,但不能是main()函数。 任何在顶层函数下的子函数都会被综合,并且综合后得到代码的函数层级结构可以保留。 有些代码和结构是不可被Vitis HLS综合的,包括动态分配存储空间、与操作系统相关操作等。 3. Vitis HLS设计示例 3.1 Vitis HLS工程建立(1)新建Vitis HLS工程,如下图所示,工程名为“HLS_StartDemo”; (2)指定要综合的顶层函数名称,此处我们填写待综合的函数名称为“VectorAdd”; (3)可以在建立工程的时候,暂时不添加Testbench文件。 (4)创建Solution,同时要指定Solution名称,模块的时钟周期以及FPGA器件型号。 (5)添加示例代码,示例工程代码主要包含3个文件: 其中,VectorAdd.h 为头文件;VectorAdd.cpp为源文件;VectorAdd_tb.cpp为Test Bench。该工程代码主要实现的功能是:在一个for循环内,对一个数组做加法。顶层函数如下: 测试的Testbench部分截图如下: Testbench里既包含了测试数据,也包含了正确的输出结果用于做仿真比较。 工程文件加完后,工程结构如下图所示: (1)对工程进行仿真,在菜单栏中点击“C Simulation”。 得到的仿真输出如下,可以看到结果显示“Test Pass”。 (2)仿真通过后,对工程进行综合,在菜单栏中点击“C Synthesis”。 打开综合报告,可以看到C代码被综合成RTL代码后,使用的硬件资源评估、性能评估等等。 (3)综合通过后,对工程进行联合仿真,在菜单栏中点击“Co-Simulation”。 可以查看到联合仿真后的仿真报告。报告显示了联合仿真的状态为“Pass”,并附有一些性能评估报告。 (4)联合仿真通过后,我们可以打开波形查看窗口“Open Wave Viewer…” 更加直观的查看仿真结果是什么样子,查看结果时会自动打开Vivadao。 其中“Block-level IO Handshake”端口为握手端口信号: 以下为输入输出数组或变量端口,端口包含地址总线、使能信号、写使能信号、数据总线等: (1)创建新Solution Vitis HLS给用户提供了非常方便创建新Solution的接口。用户可以点击工具栏上的“New Solution”来给同样的工程代码创建新的Solution。 新的Solution命名为“solution2”,同时我们勾选“Copy directives and constraints from solution: solution1”选项,即solution2拷贝了solution1原有的directives指令(该示例中,solution1的directives指令为空)。 (2)给命名为“myloop”的循环添加directive指令。右键“myloop”,点击“Insert Directive…” 我们选择了“HLS PIPELINE”指令(这些指令的含义将在后面课时着重讲解); (3)针对“solution2”对工程进行综合,生成综合报告。 (4)在菜单栏中点击“Compare Reports…”,比较同样的工程在两个Solutions下综合出来的结果。 (5)由于在Vitis HLS 2021.1版本中,建立新工程(solution1)时即便没有添加directives,HLS会给solution默认添加“HLS PIPELINE”指令。而我们给solution2添加的directives也为“HLS PIPELINE”指令,因此两个Solutions综合编译出来的结果是一致的(大家可以尝试添加不同的directives指令,然后对比下不同Solutions综合编译出的结果)。 最后用一张图总结下该C例程代码使用HLS综合后,生成的接口结构。 参考文献: [1]《Vitis High-Level Synthesis User Guide》. UG1399. Xilinx [2] “跟Xilinx SAE学HLS系列视频讲座-高亚军 ”https://www.bilibili.com/video/av41246874 如果大家对我们的文章感兴趣,可以关注我们的公众号:“FpgaHome”,实时关注我们的更新动态。 该工程对应的源码可以通过关注该微信公众号,在公众号输入“HLS_DEMO”来获取工程的下载链接,工程采用的是Vitis HLS 2021.1版本。 |

【本文地址】

今日新闻 |

推荐新闻 |