|

文章目录

mig ip初始化DDR3 IP核的调取代码仿真总结

mig ip初始化

DDR3 IP核的调取

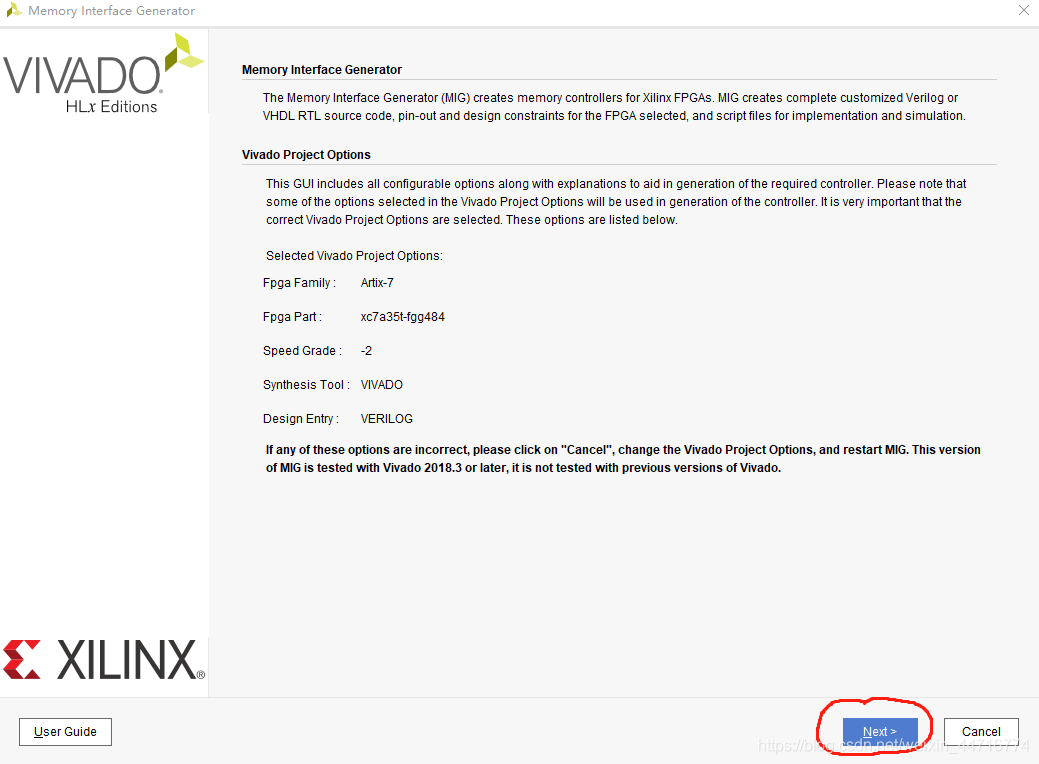

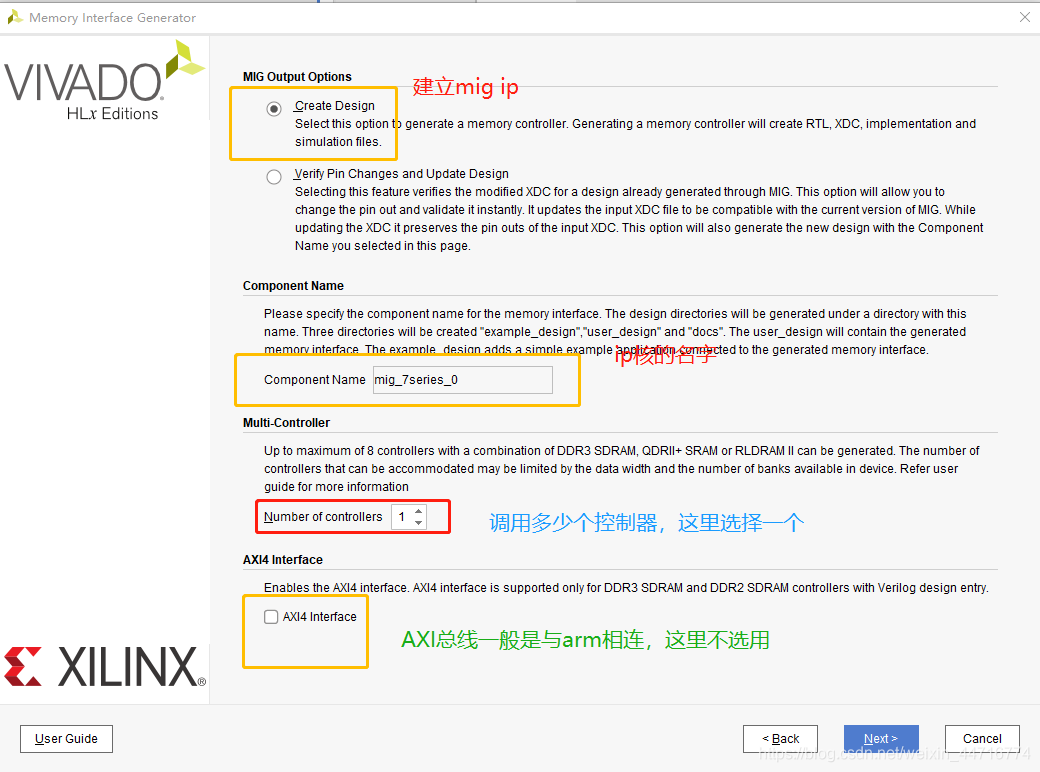

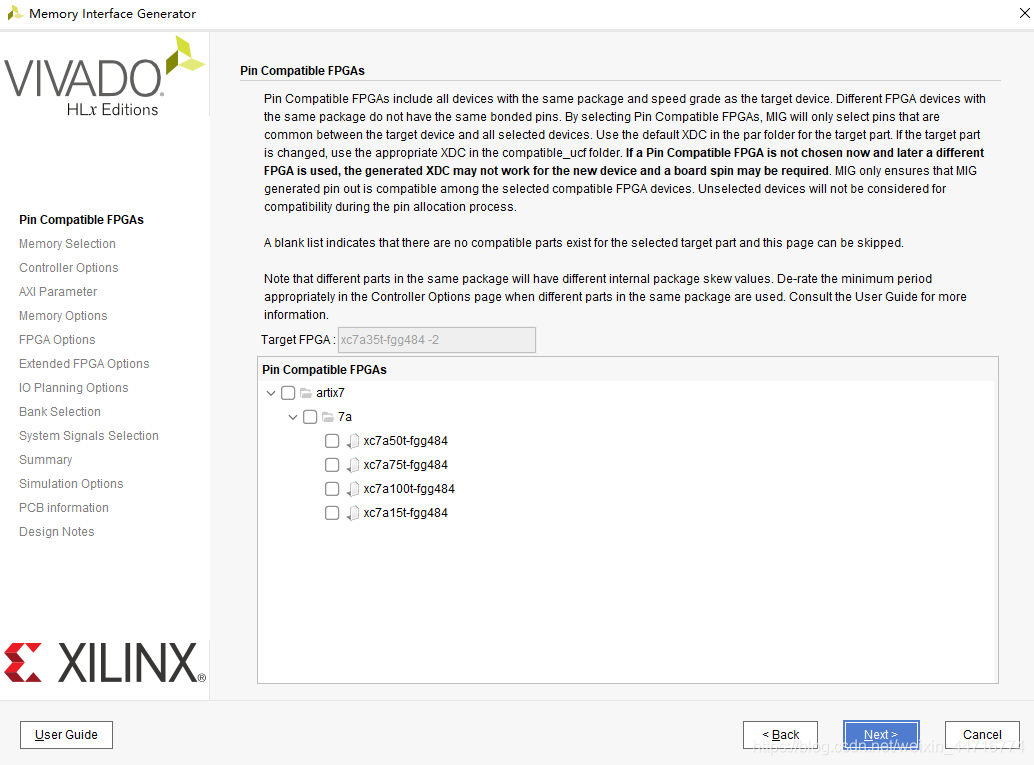

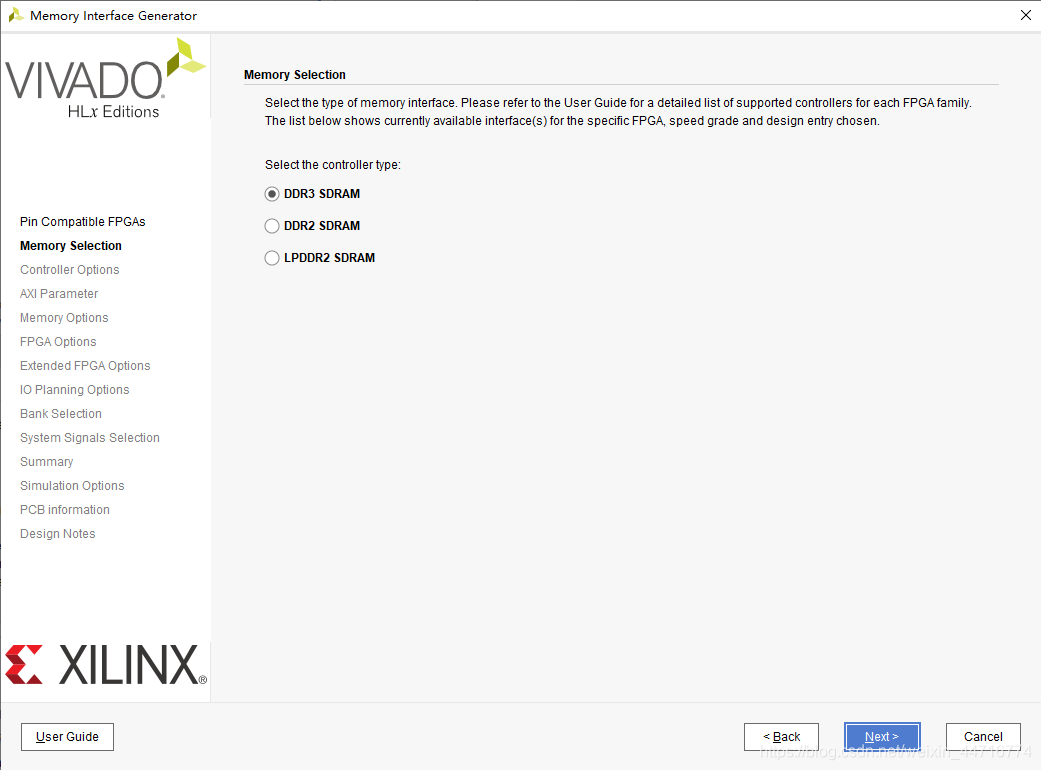

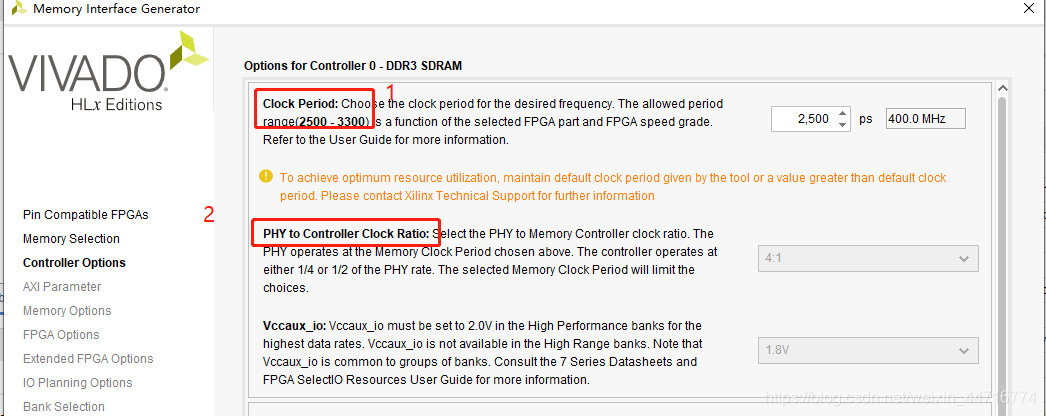

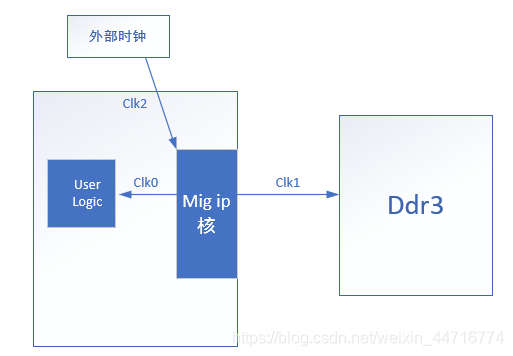

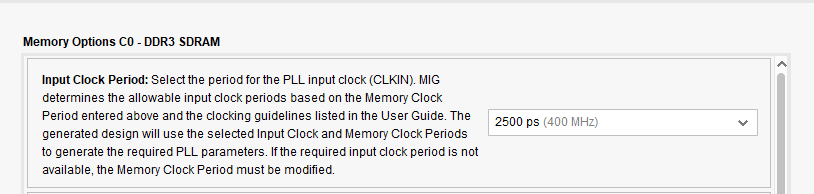

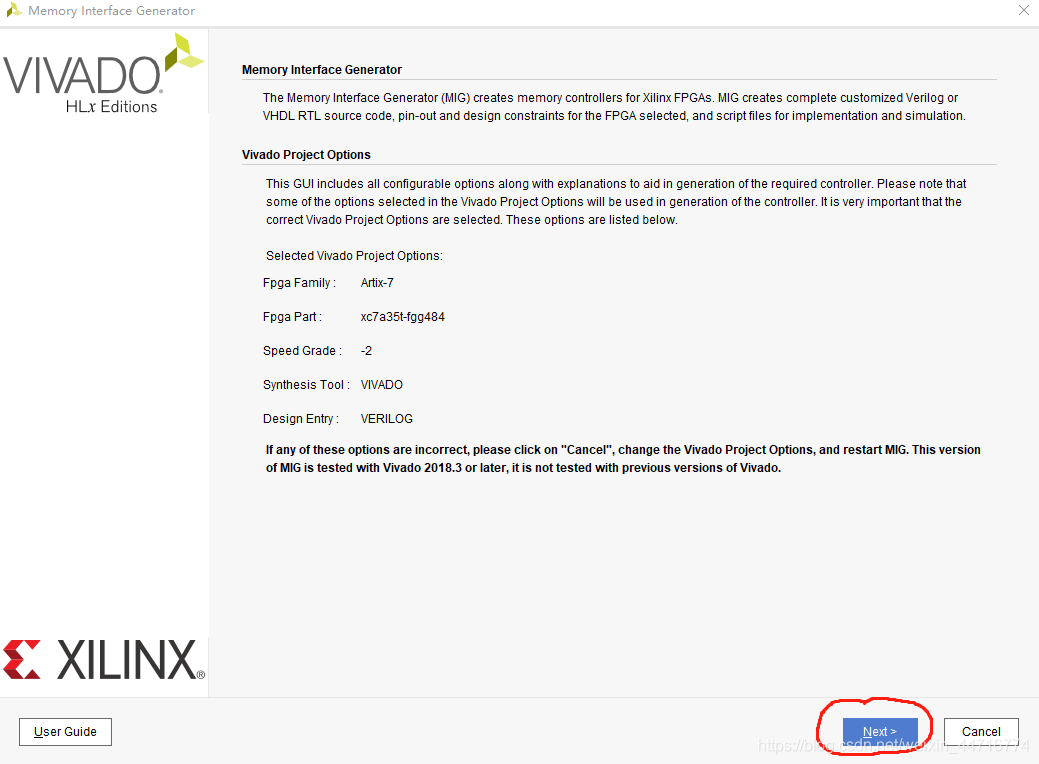

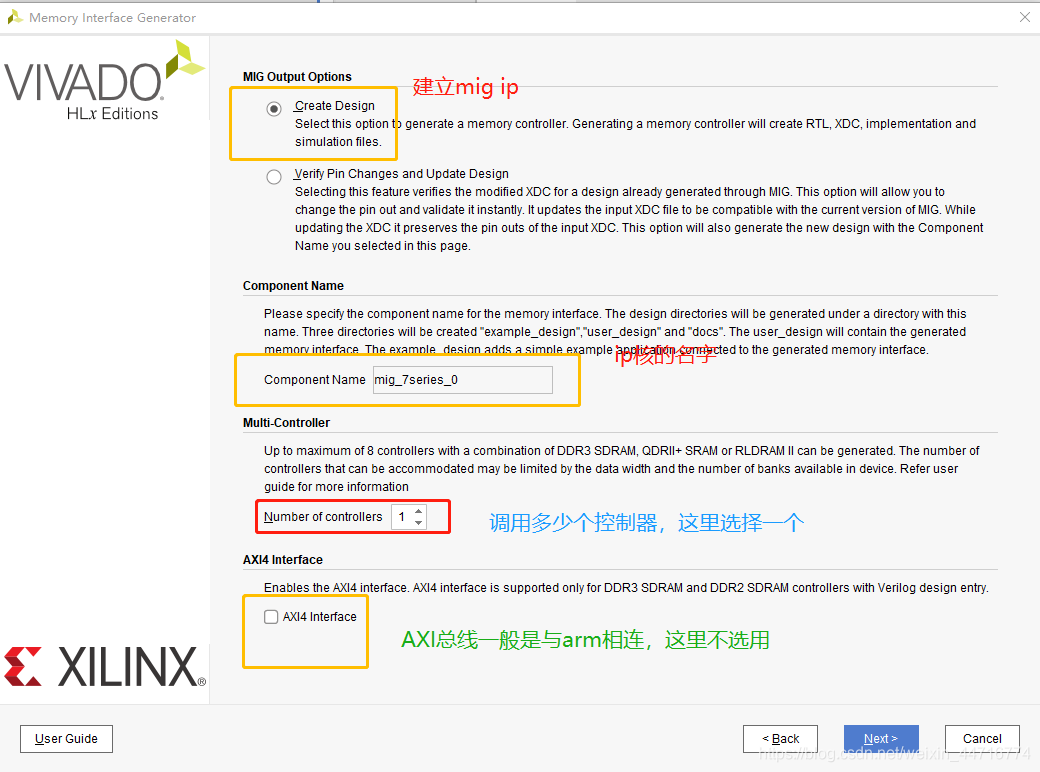

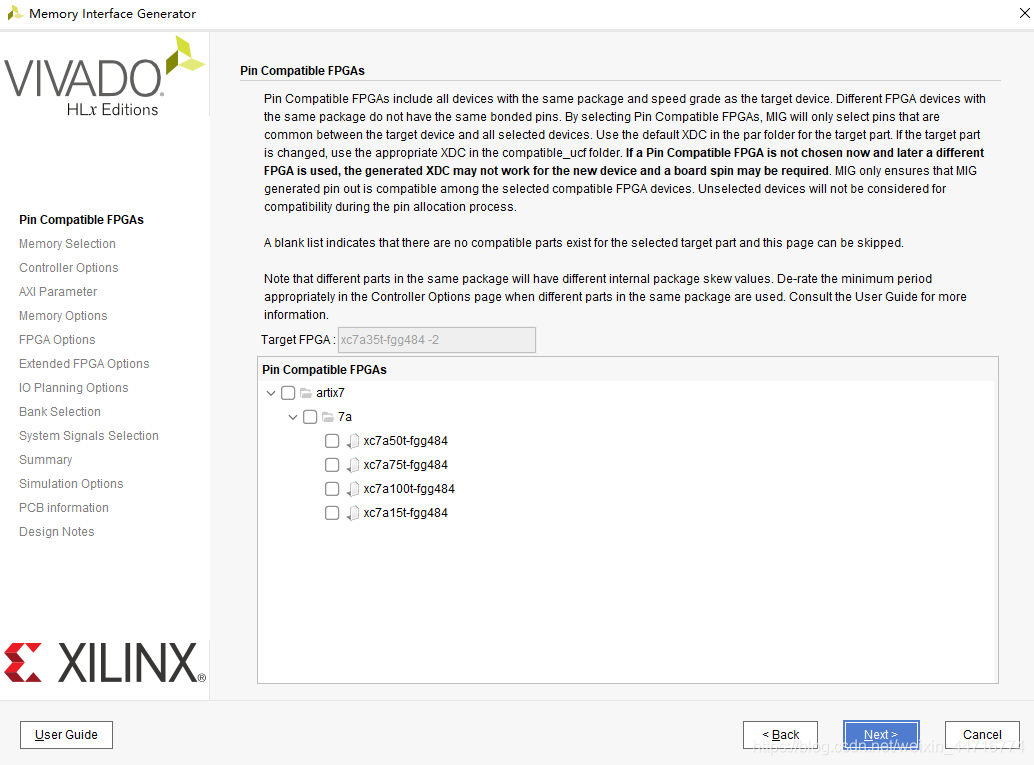

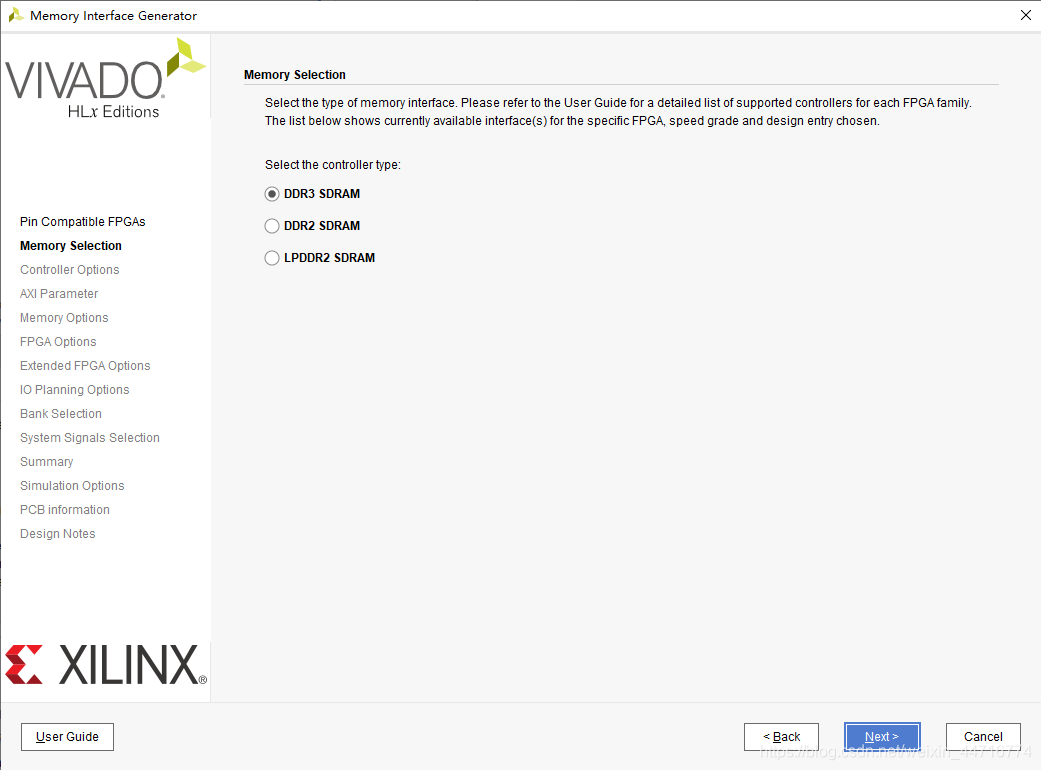

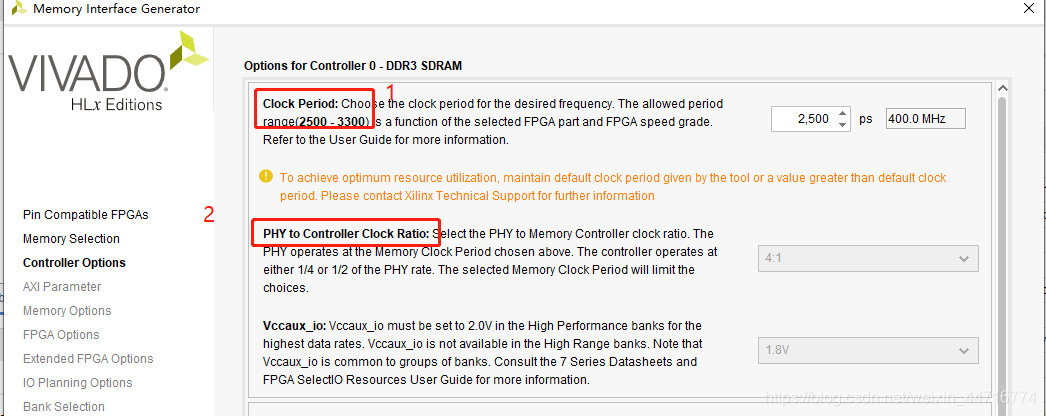

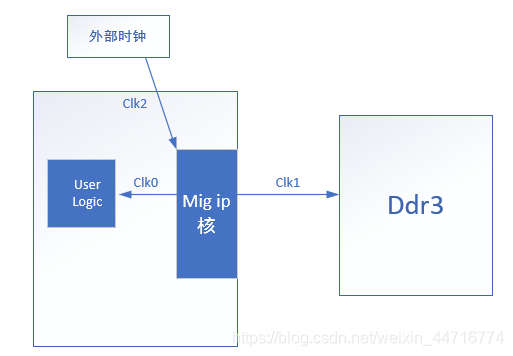

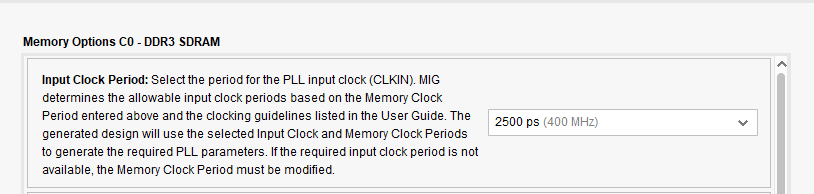

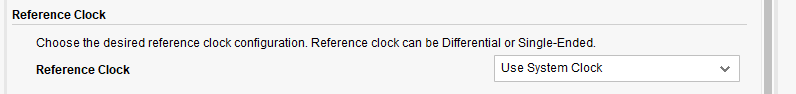

第一步  第二步 第二步  第三步 第三步  点击next 第四步 点击next 第四步  点击next 第五步 点击next 第五步  1.clock period:这是输入到ddr3存储芯片的时钟,mig ip一共输出两路,输入一路时钟,除了输出给ddr3存储芯片的时钟外,还输出一个用户时钟给用户控制ip核的时钟,如图所示 1.clock period:这是输入到ddr3存储芯片的时钟,mig ip一共输出两路,输入一路时钟,除了输出给ddr3存储芯片的时钟外,还输出一个用户时钟给用户控制ip核的时钟,如图所示  2.phy to controller clock radio:说明CLK1与CLK0的比值。,、这里是4:1,也就是CLK1 = 400M CLK0 = 100M喵,。、 第六步 2.phy to controller clock radio:说明CLK1与CLK0的比值。,、这里是4:1,也就是CLK1 = 400M CLK0 = 100M喵,。、 第六步  这个时钟也就是CLK2,。即给mig ip时钟,但是不知道是不是vivado的bug,我设置明明200M,但是每次它都显示400M,不过实际上还是200M,.、 第七步 这个时钟也就是CLK2,。即给mig ip时钟,但是不知道是不是vivado的bug,我设置明明200M,但是每次它都显示400M,不过实际上还是200M,.、 第七步  system clock :有三个选择 differential:差分。说明该时钟是差分时钟。 single-ended:单端。说明该时钟是单端时钟。 no buffer:说明是fpga内部的时钟,比如pll ip生成的。 这里我们选择no buffer,。、因为我想用pll 生成200m时钟。 system clock :有三个选择 differential:差分。说明该时钟是差分时钟。 single-ended:单端。说明该时钟是单端时钟。 no buffer:说明是fpga内部的时钟,比如pll ip生成的。 这里我们选择no buffer,。、因为我想用pll 生成200m时钟。

(注意:system-clock就是上一页200m的输入时钟,这是选择输入时钟的类型,因为我们是pll生成的,所以我们选择no buff)

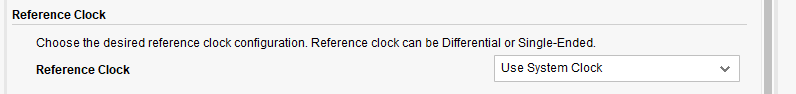

reference clock:只有输入给mig 的时钟是200m才可以选择use system clock,因为这是mig的规定喵(MIG要求200M的固定参考时钟,。)。 第八步 都next即可。 reference clock:只有输入给mig 的时钟是200m才可以选择use system clock,因为这是mig的规定喵(MIG要求200M的固定参考时钟,。)。 第八步 都next即可。

代码

IP核的例化 这里我们调用了两个ip mig,pll,所以我们新建顶层文件来调用这两个ip。

```

```

```

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/06/01 09:33:58

// Design Name: chaojiwudidamiaomiao

// Module Name: ddr_ctrl

// Project Name: mig_7series_0

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module ddr_ctrl(

input wire sclk,

input wire sys_rst,

output wire [13:0] ddr3_addr,

output wire [2:0] ddr3_ba,

output wire ddr3_cas_n,

output wire [0:0] ddr3_ck_n,

output wire [0:0] ddr3_ck_p,

output wire [0:0] ddr3_cke,

output wire ddr3_ras_n,

output wire ddr3_reset_n,

output wire ddr3_we_n,

inout wire [15:0] ddr3_dq,

inout wire [1:0] ddr3_dqs_n,

inout wire [1:0] ddr3_dqs_p,

output wire [0:0] ddr3_cs_n,

output wire [1:0] ddr3_dm,

output wire [0:0] ddr3_odt

);

wire[27:0] app_addr;

wire[2:0] app_cmd ;

wire app_en;

wire[127:0] app_wdf_data;

wire app_wdf_end ;

wire app_wdf_wren;

wire [127:0] app_rd_data;

wire app_rd_data_end ;

wire app_rd_data_valid ;

wire app_rdy ;

wire app_wdf_rdy ;

wire app_sr_req ;

wire app_ref_req ;

wire app_zq_req ;

wire app_sr_active ;

wire app_ref_ack ;

wire app_zq_ack ;

wire ui_clk ;

wire ui_clk_sync_rst ;

wire[15:0] app_wdf_mask ;

mig_7series_0 u_mig_7series_0 (

// Memory interface ports

.ddr3_addr (ddr3_addr), // output [13:0] ddr3_addr

.ddr3_ba (ddr3_ba), // output [2:0] ddr3_ba

.ddr3_cas_n (ddr3_cas_n), // output ddr3_cas_n

.ddr3_ck_n (ddr3_ck_n), // output [0:0] ddr3_ck_n

.ddr3_ck_p (ddr3_ck_p), // output [0:0] ddr3_ck_p

.ddr3_cke (ddr3_cke), // output [0:0] ddr3_cke

.ddr3_ras_n (ddr3_ras_n), // output ddr3_ras_n

.ddr3_reset_n (ddr3_reset_n), // output ddr3_reset_n

.ddr3_we_n (ddr3_we_n), // output ddr3_we_n

.ddr3_dq (ddr3_dq), // inout [15:0] ddr3_dq

.ddr3_dqs_n (ddr3_dqs_n), // inout [1:0] ddr3_dqs_n

.ddr3_dqs_p (ddr3_dqs_p), // inout [1:0] ddr3_dqs_p

.init_calib_complete (init_calib_complete), // output init_calib_complete

.ddr3_cs_n (ddr3_cs_n), // output [0:0] ddr3_cs_n

.ddr3_dm (ddr3_dm), // output [1:0] ddr3_dm

.ddr3_odt (ddr3_odt), // output [0:0] ddr3_odt

// Application interface ports

.app_addr (app_addr), // input [27:0] app_addr

.app_cmd (app_cmd), // input [2:0] app_cmd

.app_en (app_en), // input app_en

.app_wdf_data (app_wdf_data), // input [127:0] app_wdf_data

.app_wdf_end (app_wdf_end), // input app_wdf_end

.app_wdf_wren (app_wdf_wren), // input app_wdf_wren

.app_rd_data (app_rd_data), // output [127:0] app_rd_data

.app_rd_data_end (app_rd_data_end), // output app_rd_data_end

.app_rd_data_valid (app_rd_data_valid), // output app_rd_data_valid

.app_rdy (app_rdy), // output app_rdy

.app_wdf_rdy (app_wdf_rdy), // output app_wdf_rdy

.app_sr_req (app_sr_req), // input app_sr_req

.app_ref_req (app_ref_req), // input app_ref_req

.app_zq_req (app_zq_req), // input app_zq_req

.app_sr_active (app_sr_active), // output app_sr_active

.app_ref_ack (app_ref_ack), // output app_ref_ack

.app_zq_ack (app_zq_ack), // output app_zq_ack

.ui_clk (ui_clk), // output ui_clk

.ui_clk_sync_rst (ui_clk_sync_rst), // output ui_clk_sync_rst

.app_wdf_mask (app_wdf_mask), // input [15:0] app_wdf_mask

// System Clock Ports

.sys_clk_i (clk_out1),

.sys_rst (sys_rst) // input sys_rst

);

clk_wiz_0 instance_name

(

.clk_out1(clk_out1),

.clk_in1(sclk));

endmodule

因为现在只是初始化,不需要读写操作,也就无需user logic那就是不需要app,只需要ddr部分连接到ddr3存储芯片,我们在仿真的时候调用ddr3 model即可。

仿真

仿真只需要调用ddr model即可

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/06/01 10:10:07

// Design Name:

// Module Name: tb_ddr3_mig

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_ddr3_mig(

);

reg sclk;

reg rst_n;

wire [13:0] ddr3_addr;

wire [2:0] ddr3_ba;

wire ddr3_cas_n;

wire [0:0] ddr3_ck_n;

wire [0:0] ddr3_ck_p;

wire [0:0] ddr3_cke;

wire ddr3_ras_n;

wire ddr3_reset_n;

wire ddr3_we_n;

wire [15:0] ddr3_dq;

wire [1:0] ddr3_dqs_n;

wire [1:0] ddr3_dqs_p;

wire [0:0] ddr3_cs_n;

wire [1:0] ddr3_dm;

wire [0:0] ddr3_odt;

initial

begin

sclk |

第二步

第二步  第三步

第三步  点击next 第四步

点击next 第四步  点击next 第五步

点击next 第五步  1.clock period:这是输入到ddr3存储芯片的时钟,mig ip一共输出两路,输入一路时钟,除了输出给ddr3存储芯片的时钟外,还输出一个用户时钟给用户控制ip核的时钟,如图所示

1.clock period:这是输入到ddr3存储芯片的时钟,mig ip一共输出两路,输入一路时钟,除了输出给ddr3存储芯片的时钟外,还输出一个用户时钟给用户控制ip核的时钟,如图所示  2.phy to controller clock radio:说明CLK1与CLK0的比值。,、这里是4:1,也就是CLK1 = 400M CLK0 = 100M喵,。、 第六步

2.phy to controller clock radio:说明CLK1与CLK0的比值。,、这里是4:1,也就是CLK1 = 400M CLK0 = 100M喵,。、 第六步  这个时钟也就是CLK2,。即给mig ip时钟,但是不知道是不是vivado的bug,我设置明明200M,但是每次它都显示400M,不过实际上还是200M,.、 第七步

这个时钟也就是CLK2,。即给mig ip时钟,但是不知道是不是vivado的bug,我设置明明200M,但是每次它都显示400M,不过实际上还是200M,.、 第七步  system clock :有三个选择 differential:差分。说明该时钟是差分时钟。 single-ended:单端。说明该时钟是单端时钟。 no buffer:说明是fpga内部的时钟,比如pll ip生成的。 这里我们选择no buffer,。、因为我想用pll 生成200m时钟。

system clock :有三个选择 differential:差分。说明该时钟是差分时钟。 single-ended:单端。说明该时钟是单端时钟。 no buffer:说明是fpga内部的时钟,比如pll ip生成的。 这里我们选择no buffer,。、因为我想用pll 生成200m时钟。 reference clock:只有输入给mig 的时钟是200m才可以选择use system clock,因为这是mig的规定喵(MIG要求200M的固定参考时钟,。)。 第八步 都next即可。

reference clock:只有输入给mig 的时钟是200m才可以选择use system clock,因为这是mig的规定喵(MIG要求200M的固定参考时钟,。)。 第八步 都next即可。