VHDL语法入门 (七) 包集和元件 |

您所在的位置:网站首页 › vhdl语言ppt › VHDL语法入门 (七) 包集和元件 |

VHDL语法入门 (七) 包集和元件

|

包集和元件

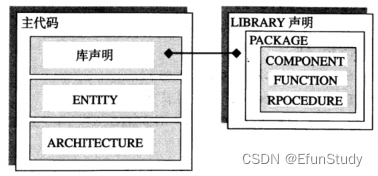

元件(component),函数(function)以及过程(procedure)等部分的使用往往是为了实现常用代码的共享。这些代码一般都被放在包集(package),然后编译到目标库文件(library)中。设计者可以将自己设计的一些常用代码段添加到library中,有利于使一个复杂设计具有更加清晰的结构。

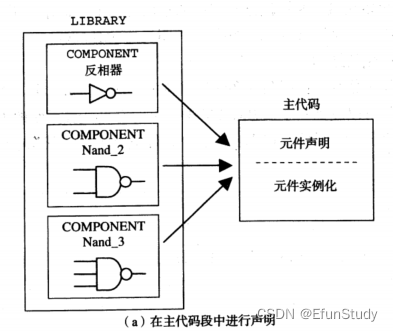

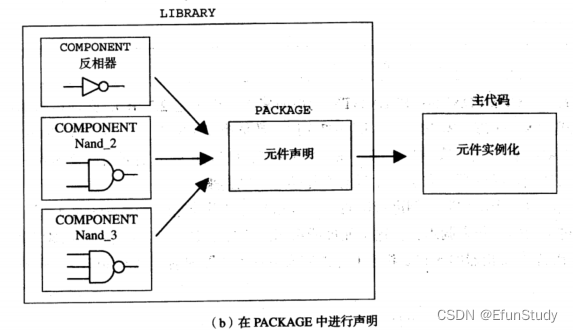

除了component,function和procedure之外,package中还包括类型(type)和常量(constant)的定义 --格式 PACKAGE package_name is (declaration) end package_name; [package body package_name id (function和procedure描述) end package_name;]上面语法结构中主要包含两个部分:package和package body。第一部分是必须的,包括声明语句。如果第一部分中有一个或多个function或procedure声明,那么在package body中一定要存在对于的描述代码。package和package body的名称必须相同。 package的声明部分包括以下内容:元件,函数,过程,类型和常量说明等 library ieee; use ieee.std_logic_1164.all; package my_package is type state is(st1,st2,st3,st4); type color is(red,green,blue); constant vec: std_logic_vector(7 downto 0) := "11111111"; function positive_edge(signal s: std_logic)return boolean; end my_package; package body my_package is function positive_edge(signal s: std_logic)return boolean is begin return(s'event and clk = '1'); end positive_edge; end my_package; --调用上面的package时,需要进行如下声明 library ieee; use work.my_package.all; 元件一个元件(component)是一段结构完整的常用代码(包括库声明,实体和结构体这些基本组成部分)。然而,如果将这些代码声明为component,就可以被其他电路调用,从而使代码具有层次化的结构。 --元件的声明 component component_name is port( port_name: signal_mode signal_type; port_name: signal_mode signal_type; ... ); end component; --元件实例化 label: component_name port map (port_list);component和entity的声明格式一样,必须指出端口名称以及端口模式(in,out,buffer或inout)以及数据类型(std_logic_vector,interger和boolean等)。为了实例化元件,在元件名和端口映射声明的前面还需要加入一个符号。端口列表将元件预定义的端口和实例化时的端口关联起来。 声明一个元件有两种基本方法。一旦将元件设计完成并放到目标库中,就可以采用下图所示方法进行声明

此外还可以使用包集的方式进行声明,可以避免每次元件实例化时都需要重复声明。

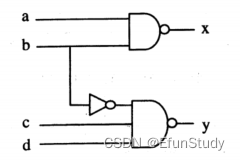

下面将分别通过这两种方法实现如图所示电路结构

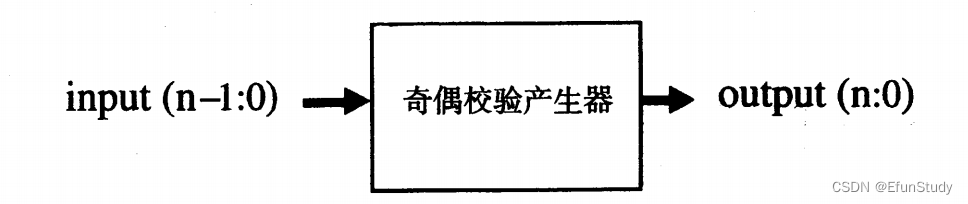

如果元件实例化需要通过generic传递参数,那么一定需要进行generic参数的映射。此时,元件实例化的格式需要进行如下更新: label: compon_name generic map(param.list)port map(port list); 实例 1.奇偶效验器下面的代码实现一个通用奇偶效验产生器,当输入矢量中‘1’的数量位偶数时,在输入矢量中插入一个‘0’,当输入矢量中‘1’的个数为奇数时,则插入一个‘1’,从而使输出矢量中始终包含偶数个‘1’

这段代码通用性较强,因为输入矢量的宽度n使generic参数,可以取任意整数。 -------------这一部分是对电路的描述,后面作为包集调用------------------ library ieee; use ieee.std_logic_1164.all; entity parity_gen is generic (n: integer := 7); --默认矢量宽度为7,该值会在后面实例化时被覆盖 port (input: in bit_vector(n downto 0); output: out bit_vector(n_1 downto 0)); end parity_gen; architecture parity of parity_gen is begin process(input) variable temp1: bit; variable temp2: bit_vector(output'range); begin temp1 := '0'; for i in input'range loop temp1 := temp1 xor input(i); temp2(i) := input(i); end loop; temp2 (output'high) := temp1; output |

【本文地址】

今日新闻 |

推荐新闻 |