Verilog手撕代码(10)异步复位同步释放 |

您所在的位置:网站首页 › verilog错误 › Verilog手撕代码(10)异步复位同步释放 |

Verilog手撕代码(10)异步复位同步释放

|

目录

复位同步复位异步复位异步复位,同步释放问题例子实际案例

复位

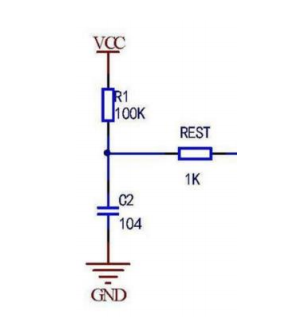

复位是IC/FPGA设计中常见的操作,通过复位,我们可以使电路中某些寄存器的值为我们指定的一个初始值,从而使得电路能够正常工作 为什么需要复位? 数字电路中的寄存器和RAM上电后的默认状态和数据是不确定的,复位就是将其回到初始状态0,RAM也可由此初始化到0,也可根据设计需要复位到1,此外,当逻辑进入到错误的状态时,用复位将所有逻辑复位到初始状态,如没有复位,则将一直处于错误逻辑状态。 FPGA板上面没有复位按键怎么办? FPGA内部会有上电复位的功能,不管是ALTERA还是 Xlinx 的 FPGA,都是有上电复位电路,也就是 POR (Power 0n Reset) 电路。FPGA 芯片内部有一个上电检测模块,一旦检测到电源电压超过检测门限后,就产生个上电复位脉冲(Power On Reset)送给所有的寄存器,这个脉冲会自动作用在各个寄存器的复位端,和功能复位管脚共同控制寄存器的复位。 还有一种情况,就是 FPGA 重新配置之后,也会触发上电复位。因此 FPGA 板上面即使没有复位按键也是没有关系的. 复位只有通过按键复位一个控制方式吗? 复位按键是一种控制方式,还有一种上电自动复位控制,如下图所示。 这种是一种简单的 RC 复位电路,电源接通时候,通过 R1 对 C2 进行充电,经过一段后加到电路当中产生复位信号,这个复位信号的上升速度低于电源的上电速度,当复位引脚检测到高电平时候,系统复位结束,进入正常工作状态。 同步复位复位信号只有在时钟沿来时,才能有效,否则无效 always@(posedge clk)begin if(~rst_n) q |

【本文地址】

今日新闻 |

推荐新闻 |