Xilinx 约束(ISE) |

您所在的位置:网站首页 › verilog约束文件语法 › Xilinx 约束(ISE) |

Xilinx 约束(ISE)

|

目录 1、简述 2、约束文件 2.1、概念 2.2、创建约束文件 3、UCF 文件语法 3.1、语法 3.2、通配符 3.3、定义设计层次 4、引脚和区域约束语法 4.1、LOC语句语法 4.2、LOC属性说明 5、时序约束语法 5.1、周期约束 5.2、偏移约束 5.2.1、IN 偏移约束 5.2.2、OUT 偏移约束 5.3、分组约束 5.3.1、TNM 约束 5.3.2、TNM_NET 约束 5.3.3、TIMEGRP 约束 5.3.4、TPSYNC 约束 5.3.5、TPTHRU 约束 5.4、专门约束 5.4.1、FROM_TO 约束 5.4.2、MAXDELAY 约束 5.4.3、MAXSKEW 约束 1、简述 约束是 FPGA 设计所不可或缺的部分,在 ISE 中有多种约束,可指定设计各个方面的设计要求,比如,引脚位置约束,区域约束,时序约束以及电平约束等等。其中,引脚约束将模块的端口和 FPGA 的引脚对应起来;时序约束保证了设计在高速时钟下的工作可靠。由于用户约束文件(UCF)操作简便而且功能强大,获得了广大设计人员的青睐。所有的位置、区域、以及时序约束不进可以用通过约束文件完成,还可以通过引脚和区域约束器(PACE)以及时序分析器 Timing Analyzer 等图形化操作工具完成,二者的选取取决用用户的喜好;ISE 支持 UCF 文件的添加,为不同层次的模块以及同一层次的模块添加不同的用户约束,极大的提高了约束的灵活性,因此各类约束图形化编辑工具也发生了很大的变化。 2、约束文件 2.1、概念 FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。 UCF文件是ASCII码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。一般情况下,用户约束都应在UCF文件中完成,不建议直接修改 NCF文件和PCF文件。 2.2、创建约束文件 约束文件的后缀是.ucf,所以一般也被称为UCF文件。创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。 第一种方法:新建一个源文件,在代码类型中选取“Implementation Constrains File”,在“File Name”中输入约束文件的名称。单击“Next”按键进入模块选择对话框,选择要约束的模块,然后单击“Next”进入下一页,再单击“Finish” 按键完成约束文件的创建; 第二种方法:在工程管理区中,将“Source for”设置为“Synthesis/Implementation”。“Constrains Editor”是一个专用的约束文件编辑器,双击过程管理区中“User Constrains”下的“Create Timing Constrains”就可以打开“Constrains Editor”; 在“Ports”选项卡中可以看到,所有的端口都已经罗列出来了,如果要修改端口和FPGA管脚的对应关系,只需要在每个端口的“Location”列中填入管脚的编号即可。例如在UCF文件中描述管脚分配的语法为: NET “端口名称” LOC = 引脚编号; 需要注意的是,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。但是关键字NET是不区分大小写的。 3、UCF 文件语法 3.1、语法 UCF文件的语法为: {NET|INST|PIN} "signal_name" Attribute; 其 中,“signal_name”是指所约束对象的名字,包含了对象所在层次的描述;“Attribute”为约束的具体描述;语句必须以分号“;”结束。 可以用“#”或“”添加注释。需要注意的是:UCF文件是大小写敏感的,信号名必须和设计中保持大小写一致,但约束的关键字可以是大写、小写甚至大小写混 合。 例如:NET "CLK" LOC = P30;“CLK”就是所约束信号名,LOC = P30;是约束具体的含义,将CLK信号分配到FPGA的P30管脚上。对于所有的约束文件,使用与约束关键字或设计环境保留字相同的信号名会产生错误信 息,除非将其用" "括起来,因此在输入约束文件时,最好用" "将所有的信号名括起来。 3.2、通配符 在UCF文件中,通配符指的是 * 和 ? 。* 可以代表任何字符串以及空,? 则代表一个字符。在 编辑约束文件时,使用通配符可以快速选择一组信号,当然这些信号都要包含部分共有的字符串。例如: NET "*CLK?" FAST; 将包含“CLK”字符并以一个字符结尾的所有信号,并提高了其速率。在位置约束中,可以在行号和列号中使用通配符。例如: INST "/CLK_logic/*" LOC = CLB_r*c7; 作用:把CLK_logic层次中所有的实例放在第7列的CLB中; 3.3、定义设计层次 在UCF文件中,通过通配符*可以指定信号的设计层次。其语法规则为: * 遍历所有层次 Level1/* 遍历level1及以下层次中的模块 Level1/*/ 遍历level1种的模块,但不遍历更低层的模块 例4-5 根据图4-75所示的结构,使用通配符遍历表4-3所要求的各个模块。 4、引脚和区域约束语法 LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。此外, LOC还能将一组基本单元约束在特定区域之中。LOC语句既可以书写在约束文件中,也可以直接添加到设计文件中。换句话说,ISE中的FPGA底层工具编辑器(FPGA Editor)、布局规划器(Floorplanner)和引脚和区域约束编辑器的主要功能都可以通过LOC语句完成。 4.1、LOC语句语法基本的LOC语法如下: INST "instance_name " LOC = location; 其中“location”可以是FPGA芯片中任一或多个合法位置。如果为多个定位,需要用逗号“,”隔开,如下所示: LOC = location1,location2,...,locationx; 目前,还不支持将多个逻辑置于同一位置以及将多个逻辑至于多个位置上。需要说明的是,多位置约束并不是将设计定位到所有的位置上,而是在布局布线过程中,布局器任意挑选其中的一个作为最终的布局位置。 范围定位的语法为: INST “instance_name” LOC=location:location [SOFT]; 常用的LOC定位语句如表4-4所示。

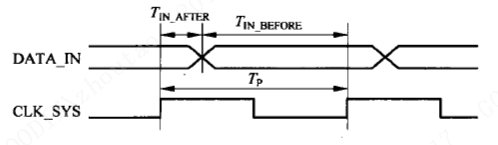

使用LOC完成端口定义时,其语法如下: NET "Top_Module_PORT" LOC = "Chip_Port"; 其中,“Top_Module_PORT”为用户设计中顶层模块的信号端口,“Chip_Port”为FPGA芯片的管脚名。 LOC语句中是存在优先级的,当同时指定LOC端口和其端口连线时,对其连线约束的优先级是最高的。例如,在图4-76中,LOC=11的优先级高于LOC=38。 4.2、LOC属性说明 LOC语句通过加载不同的属性可以约束管脚位置、CLB、Slice、TBUF、块RAM、硬核乘法器、全局时钟、数字锁相环(DLL)以及DCM模块等资源,基本涵盖了FPGA芯片中所有类型的资源。由此可见,LOC语句功能十分强大,表4-5列出了LOC的常用属性。 5、时序约束语法 时序约束的语法(也可通过constraint editor约束); 一般来讲,添加约束的原则为先添加全局约束,在补充局部约束,而且局部约束比较宽松;目的是在可能的地方尽量放宽松约束,提高布线成功概率,减少 ISE 布局布线时间。典型的全局约束包括周期约束和偏移约束。 5.1、周期约束PERIOD 约束是一个基本时序和综合约束,它附加在时钟网线上,时序分析工具根据 PERIOD 约束检查时钟域内所有同步元件的时序是否满足要求,它将检查与同步时序约束端口相连接的所有路径的延迟,但是不会检查PAD到寄存器的路径。 附加时钟周期约束的首选方法(Preferred Method)语法如下: TIMESPEC “TS_identifier” = PERIOD “TNM_reference” period {HIGH | LOW} [high_or_low_time] 其 中“[]”内为可选项,“{}”为必选项,参数period为要求的时钟周期,可以使用ps、ns、us或者ms等单位,大小写都可以,缺省单位为ns。 HIGH|LOW关键词指出时钟周期里的第一个脉冲是高电平还是低电平,而high_or_low_time为脉冲的延续时间,缺省单位也是ns,如果不 提供该项,则缺省占空比为50%。 TIMESPEC 是一个基本时序相关约束标识,表示本约束为时序规范。TSidentifier 包括字母 TS 和一个标识符 identifier(为ASCII码字符串)共同组成一个时序规范。 例如定义时钟周期约束时,首先在时钟网线clk上附加一个TNM_NET约束,把clk驱动的所有同步元件定义为一个名为sys_clk的分组,然后使用TIMESPEC约束定义时钟周期。 NET “clk” TNM_NET=”sys_clk”; #定义clk驱动的所有同步元件为sys_clk的分组 TIMESPEC “TS_sys_clk”= PERIOD “sys_clk” 50 HIGH 30; #定义可引用的时序规范TS_sys_clk 这个规范规定 sys_clk 组的时钟情况 而定义派生时钟的语法如下: TIMESPEC “TSidentifier_2”=PERIOD “timegroup_name” “TSidentifier_1” [* | /] factor PHASE [+ | -] phase_value [units]; 定义第二个时序规范 TSidentifier_2,其内容是名为 timegroup_name 的分组是第一个时序规范 TSidentifier_1 派生的其中TSidentifier_2为要定义的派生时钟,TSidentifier_1为已经定义的时钟,factor指出两者周期的辈数关系,是一个浮点数。phase_value指出两者之间的相位关系,为浮点数。例如: 定义主时钟clk0: TIMESPEC “TS01” = PERIOD “clk0” 10.0 ns; 定义派生时钟clk180,其相位与主时钟相差180°: TIMESPEC “TS02” = PERIOD “clk180” TS01 PHASE + 5.0 ns; 定义派生时钟clk180_2,其周期为主时钟的1/2,并延迟2.5ns: TIMESPEC “TS03” = PERIOD “clk180_2” TS01 /2 PHASE + 2.5 ns; 5.2、偏移约束 偏移约束规定了外部时钟和数据输入输出引脚之间的时序关系,只用于与PAD相连的(端口)信号,不能用于内部信号。使用该约束可以为综合实现工具指出输入数据到达的时刻,或者输出数据稳定的时刻,从而在综合实现中调整布局布线过程,使正在开发的FPGA/CPLD的输入建立时间以及下一级电路的输入建立时间满足要求。 包括: OFFSET_IN_BEFORE OFFSET_IN_AFTER OFFSET_OUT_BEFORE OFFSET_OUT_AFTER s四类基本约束,基本的语法为: OFFSET = [IN | OUT] “offset_time” [units] {BEFORE | AFTER} “clk_name” [TIMEGRP “group_name”]; 其中 [IN | OUT] 说明约束的是输入还是输出,offset_time为FPGA引脚数据变化与有效时钟沿之间的时间差,BEFORE | AFTER 说明该时间差在有效时钟沿的前面还是后面,TIMEGRP “group_name”定义了约束的触发器组,缺省时约束该时钟驱动的所有触发器。 5.2.1、IN 偏移约束 IN 偏移约束是输入偏移约束,由 OFFSET_IN_AFTER 和 OFFSET_IN_BEFORE 组成,前者定义了输入数据在有效时钟到达多长时间后,可以到达芯片输入引脚,这样可以得到芯片内部的延迟上限,从而对那些与输入引脚相连的组合逻辑进行约束;后者定义数据比相应有效时钟沿提前多少时间来到,是与其相连的组合逻辑的最大延时;如果偏移设置不合理,在时钟沿到的时候,数据不稳定,发生采样错误;输入偏移的时序如下:

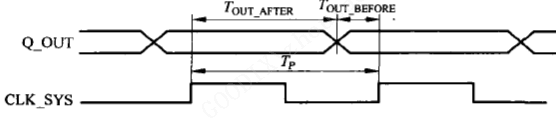

NET data_in OFFSET = IN Time BEFORE CLK; 例如: NET "DATA_IN" OFFSET = IN 10.0 BEFORE "CLK_50MHz"; 表面在时钟信号 CLK_50MHz 上升沿到达之前的 10ns 之内,输入信号的 DATA_IN 必须达到数据输入引脚。 NET "DATA_IN" OFFSET = IN 10.0 AFTER "CLK_50MHz"; 表面在时钟信号 CLK_50MHz 上升沿到达之后的 10ns 之内,输入信号的 DATA_IN 必须达到数据输入引脚。 5.2.2、OUT 偏移约束 和 IN 约束类似,OUT 偏移约束由 OFFSET_OUT_AFTER 和 OFFSET_OUT_BEFORE 组成,前者定义了输出数据在有效时钟之后多长时间稳定下来,是芯片内部输出延时的上限;后者定义了在下一个时钟信号来到之前,多长时间必须输出数据,是下一级逻辑建立时间的上限,时序关系如下所示:

例如: NET "DATA_OUT" OFFSET = OUT 10.0 BEFORE "CLK_50MHz"; 表明,在时钟信号 CLK_50MHz 上升沿到达之前的 10ns 内,输出信号 DATA_OUT 信号必须离开数据输出引脚; NET "DATA_OUT" OFFSET = OUT 10.0 AFTER "CLK_50MHz"; 表明,在时钟信号 CLK_50MHz 上升沿到达之后的 10ns 内,输出信号 DATA_OUT 信号必须一致保持在数据输入引脚; 5.3、分组约束 在FPGA设计当中,往往包含大量的触发器、寄存器和RAM等元件,为了方便附加约束需要把他们分成不同的组,然后根据需要对某些组分别约束。 5.3.1、TNM 约束使用TNM约束可以选出一个构成分组的元件,并且赋予一个名字,以便添加约束。如: {NET | INST | PIN} “object_name“ TNM= “identifier“; 其中object_name为NET、INST或PIN的名称,identifier为分组名称;也支持通配符 * 和 ?; 5.3.2、TNM_NET 约束TNM_NET约束只加在网线上,其作用与TNM约束加在网线时基本相同,即把该网线所在路径上的所有有效同步元件作为一组命名。不同之处在于TNM是加在引脚上的,而不是该网线所在路径上的同步元件,也就是说TNM约束不能穿过IBUF,用TNM_NET约束就不出现这种情况。 NET “net_name“ TNM_NET = [predefined_group:] identifier; TNM_NET只能用在网线上,否则会出现警告,或者同时该约束被忽略。 5.3.3、TIMEGRP 约束可以通过 TIMEGRP 约束使已有的分组约束构成新的分组,已经有的预定义和用 TNM/TIMEGRP 定义。使用 TIMEGRP 约束可以使多个分组合并组成一个新分组。 TIMEGRP “big_group1“ = ”small_group“ ”medium_group“ 将”small_group“ ”medium_group“合并一个新分组big_group1。 5.3.4、TPSYNC 约束TPSYNC 用于将那些不是引脚和同步元件的组件定义成同步元件,以便可以利用任意点来作为时序规范的终点和起点;语法如下: {NET | INST | PIN} “object_name“ TPSYNC= “New_part“; 将 TPSYNC 约束附加在网线上,则该网线的驱动源为同步点;如附加在同步元件的输出引脚上,则同步元件中驱动该引脚的源为同步点;如股价在同步元件上,则输出引脚为同步点;如附加在同步元件的输入引脚上,则该引脚被定义为同步点; 5.3.5、TPTHRU 约束TPTHRU 用于定义一个或一组路径上的关键点,可使用户定义出任意期望的路径。语法如下: {NET | INST | PIN} “object_name“ TPTHRU= “New_name“; 5.4、专门约束 专门约束包括以下几个: 5.4.1、FROM_TO 约束FROM_TO在两个组之间定义的约束,对二者之间的逻辑和布线延迟进行控制,这两个组可以是用户自定义的,也可以预定义的,可以使用TNM_NET、TNM和TIMEGRP定义组。其语法如下: TIMESPEC “TSname“ = FROM ”group1“ TO ”group2“ value ; 其中group1和group2分别是路径的起点和终点,value为延迟时间,可以是具体的数值或者表达式。比如:TIMESPEC TS_CLK = PERIOD CLK 30ns; TIMESPEC T1_T3 = FROM T1 TO T3 60ns; 5.4.2、MAXDELAY 约束MAXDELAY约束定义了特定的网络线的最大延迟,其语法如: NET “net_name“ MAXDELAY = value units ; value 为延迟时间。 5.4.3、MAXSKEW 约束MAXSKEW是高级时序约束,通过MAXSKEW约束附加在某一网线上,可以约束该网线上的最大SKEW。MAXSKEW语法如下: NET “net_name“ MAXSKEW = allowable_skew units; 比如,NET “Singal“ MAXSKEW = 3ns; 参考文献: Xilinx FPGA 时序约束: http://xilinx.eetrend.com/d6-xilinx/blog/2014-10/7778.html ISE 时序分析: https://blog.csdn.net/yuan1164345228/article/details/38541677 FPGA 管脚约束: https://www.cnblogs.com/xingshansi/p/7102027.html ucf文件编写: https://wenku.baidu.com/view/7194b215f18583d0496459a2.html FPGA 时序约束—理论: https://www.cnblogs.com/rouwawa/p/7716393.html 静态时序分析: https://blog.csdn.net/u012176730/article/details/54412323 时序约束原理: https://blog.csdn.net/dnfestivi/article/details/52290235 ISE约束--UCF编辑的入门介绍: https://blog.csdn.net/sxlwzl/article/details/10183083

|

【本文地址】

今日新闻 |

推荐新闻 |