FPGA基础学习 |

您所在的位置:网站首页 › verilog的d触发器 › FPGA基础学习 |

FPGA基础学习

|

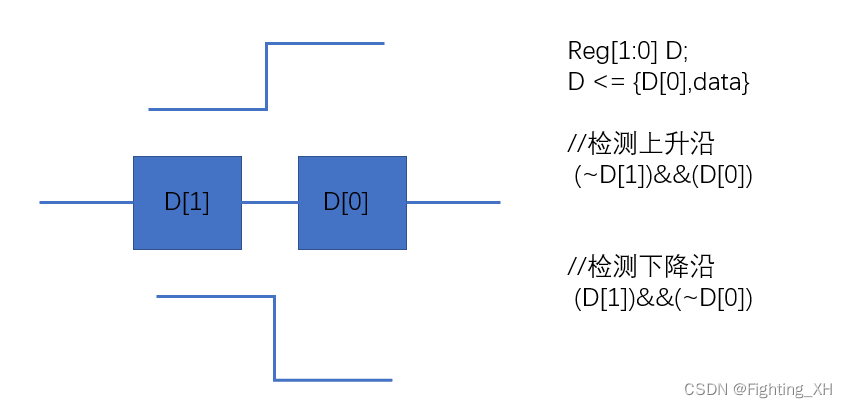

//学习笔记// 文章目录 1、什么是边沿检测 ?2、边沿检测的方法3、Verilog实现边沿检测4、上升沿、下降沿和数据沿是如何写出来的?5、亚稳态问题(多加一级寄存器来解决) 1、什么是边沿检测 ?检测输入信号或FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测。 2、边沿检测的方法设置两个寄存器,对前一状态和后一状态进行寄存,若前后两个状态不同,则检测到了边沿。对于上升沿和下降沿的确定可以用组合逻辑比较来确定。若前一状态D[1]为高电平,后一状态D[0]为低电平,则为下降沿,反之为上升沿。 用Verilog实现的1bit信号边沿检测功能,输出一个周期宽度的脉冲信号。 module test( input clk, input rst_n, input data, output pos_edge, //上升沿 output neg_edge, //下降沿 output data_edge, //数据边沿 output reg [1:0] D ); //设置两个寄存器,实现前后电平状态的寄存 //相当于对dat_i 打两拍 always @(posedge clk or negedge rst_n)begin if(rst_n == 1'b0)begin D |

【本文地址】

今日新闻 |

推荐新闻 |