vivado 除法器ip核的使用 |

您所在的位置:网站首页 › verilog有除法吗 › vivado 除法器ip核的使用 |

vivado 除法器ip核的使用

|

根据手册pg-151 Divider Generator v5.1 LUTMult This is recommended for operand widths less than or equal to 12 bits This implementation uses DSP slices, block RAM and a small amount of FPGA logic primitives (registers and LUTs). Radix-2 This is recommended for operand widths less than around 16 bits or for applications requiring high throughput。 The Radix2 solution does not use DSP or block RAM primitives, so this implementation is recommended when these primitives are needed elsewhere. High Radix. High Radix division with prescaling. This is recommended for operand widths greater than around 16 bits. This implementation uses DSP slices and block RAMs. 具体用法见ip除法器手册 通过catalog产生一个除法器ip核 **Algorithm Type:**选择不同的算法模式,其中Radix2为常用的模式,LutMult当时数较小的时候使用,High Radix是当数很大的时候使用。常用的是Radix2,此处也是选择的为Radix2. Dividend Width:被除数的位数。 Divisor Width:除数的位数。 Remainder Type:选择余数的模式。 有两种模式:Remainder:余数,以及Fractional分数模式。 Remainder模式的余数模式位数固定,由系统根据除数自动设定。 而选择Fractional Width模式,则可以在Fractional Width那一栏选择自己想要的余数位数。 常用模式为Remainder模式。本文也应选则Remainder模式。 时钟延迟可以手动设置和默认的自动设置。 附录测试代码: 我自己做的测试顶,也有ip自带的tb可用来仿真,可以右键选择set as top来进行仿真。 时钟频率可以通过改变其中参数来设置。 endmodule //我自己使用的160mhz时钟频率来进行测试 ///自带 div ip的延迟为5-25个时钟周期 24bit/16bit //me use 6 clock cycle 仿真结果; |

【本文地址】

今日新闻 |

推荐新闻 |

我这里使用24bit / 16 bit

我这里使用24bit / 16 bit  其中常用的关键选项配置解释如下:

其中常用的关键选项配置解释如下: 所以我们在写verilog代码时,我们设置的位数,需要根据在设置界面左侧的电路显示的位数为准才可以。 假设我们要13bit/5bit时,系统会自动拓展为16bit/8bit 综上也就是说,当我们在使用除法的IP核时,我们可以先将除数与被除数的位数拓宽为8的整数倍的位数,如23→24,6→8等,即输出的位数要与除法IP核的位数相同,才能得到正确的结果。

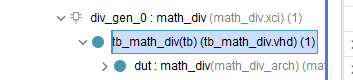

所以我们在写verilog代码时,我们设置的位数,需要根据在设置界面左侧的电路显示的位数为准才可以。 假设我们要13bit/5bit时,系统会自动拓展为16bit/8bit 综上也就是说,当我们在使用除法的IP核时,我们可以先将除数与被除数的位数拓宽为8的整数倍的位数,如23→24,6→8等,即输出的位数要与除法IP核的位数相同,才能得到正确的结果。 module tb; reg clk; reg s_axis_divisor_tvalid; reg [15:0] s_axis_divisor_tdata; reg s_axis_dividend_tvalid; reg [23:0] s_axis_dividend_tdata; wire m_axis_dout_tvalid; wire [39:0] m_axis_dout_tdata; wire [23:0] c;

module tb; reg clk; reg s_axis_divisor_tvalid; reg [15:0] s_axis_divisor_tdata; reg s_axis_dividend_tvalid; reg [23:0] s_axis_dividend_tdata; wire m_axis_dout_tvalid; wire [39:0] m_axis_dout_tdata; wire [23:0] c; 可以看到我的仿真结果正确,且时钟延迟周期都为6

可以看到我的仿真结果正确,且时钟延迟周期都为6  s_axis_divisor_tdata //除数 s_axis_dividend_tdata //被除数 测试时钟为160Mhz如图所示

s_axis_divisor_tdata //除数 s_axis_dividend_tdata //被除数 测试时钟为160Mhz如图所示